クロックレート2.4Ghzの100Mhz帯域幅80dBダイナミックレンジ連続時間デルタシグマ変調器

要約

Δの帯域幅 Σ 変調器は、オーバーサンプリング比の要件により、クロックレートによって制限されます。ナノスケールのCMOSプロセスが急速に発展しているため、広い帯域幅と高いダイナミックレンジの連続時間Δを設計することが可能です。 Σ 高周波アプリケーション用の変調器。本論文では、3次4ビット連続時間Δを提案する。 Σ シングルループフィードフォワードトポロジーの変調器。この変調器は40nm CMOSプロセスで設計されており、2.4GHzのクロックレートで80dBのダイナミックレンジと100MHzの帯域幅を実現します。変調器は1.2V電源から69.7mWを消費します。

はじめに

セルラー規格などの無線通信アプリケーションの需要の高まりに牽引されて、アナログ-デジタルコンバーター(ADC)は急速に進化し、より高い信号帯域幅(BW)とダイナミックレンジ(DR)をサポートします。 Long-Term-Evolution Advanced(LTE-A)通信規格でのBWの要件は100MHzに上昇しました。ナイキストADC、通常はパイプラインADC [1、2]は、高いBWのためにマクロ基地局で使用されてきました。ただし、熱雑音が制限されたスイッチ入力コンデンサとアンチエイリアシングフィルタを駆動するために不可欠な入力バッファは、大幅な消費電力と設計の複雑さを引き起こします。さらに、パイプラインADCが高利得広帯域残留増幅器と校正技術を決定する正確な段間利得に依存しているという事実は、複雑さと電力損失につながります。 Δ Σ ADCは、オーバーサンプリングとノイズシェーピング技術を採用した高性能と電力効率で知られています。ただし、オーバーサンプリング比(OSR)の要件は、通常16 [3–6]を超えており、GHzを超えるサンプリング周波数を決定します。最近、Δ Σ 50 MHz BWを超えるADCは、マルチGHzクロックレートを可能にするナノスケールCMOSプロセスを使用して提案されています。以前は、高周波Δ Σ ADCは通常、離散時間(DT)の実現ではなく、連続時間(CT)の実現[3–9]を採用します。後者はスイッチトキャパシタ回路によって実装され、その精度はコンデンサのマッチングに依存します。これは、プロセス変動下での堅牢な動作が提供されることを意味します。さらに、コンデンサとスイッチの時定数が十分に小さいため、クロックジッタに対する優れた耐性が提供されます。ただし、変調器の前にサンプリング操作が実行されるため、アンチエイリアシングフィルターが必要です。一方、ステージでの安定性を確保するためのセトリング要件により、DT変調器のオペアンプはCT変調器よりも広いユニティゲイン帯域幅(UGBW)で実装されます。要約すると、DT変調器は高精度で狭い信号を提供でき[10、11]、スマートセンサーや生物医学画像などの計測アプリケーションを実装するために広く使用されています。対照的に、高周波アプリケーション用のCT変調器を設計するための取り組みは、同等の複雑さと消費電力を備えたDT変調器よりも広く行われています。

特定のプロセスでのより高いBWの厳しい設計目標は、プロセスが制限されたクロックレートのために、より低いOSRを決定します。十分なDRを達成するには、従来はループフィルターカスケードによって実行され、以前の作業では一般に3以上であった、高ノイズ伝達関数次数によって実装される積極的なノイズシェーピングが必要です。ただし、ループフィルタの次数が増えると、消費電力、不安定性、および設計の複雑さが発生します。カスケード接続された低次ローカルΔによって実装された多段ノイズシェーピング(MASH)アーキテクチャ[6、8] Σ 相互にフィードバックパスのない変調器は、安定性の問題を軽減するために採用されましたが、不一致の感度があります。さらに、マルチビット量子化器を備えた変調器は、指数関数的に増加するコンパレータ量で条件付きで高いDRを取得します。

このホワイトペーパーでは、40 nmCMOSプロセスを使用して69.7mWの消費量で100MHzBWで80DRを達成する40nmCMOSのCT変調器について説明します。この論文は次のように構成されています。 「方法」のセクションでは、変調器のトポロジーと回路の実装について説明します。 「結果と考察」セクションにはシミュレーション結果が表示され、「結論」セクションにはこの作業の概要が示されます。

メソッド

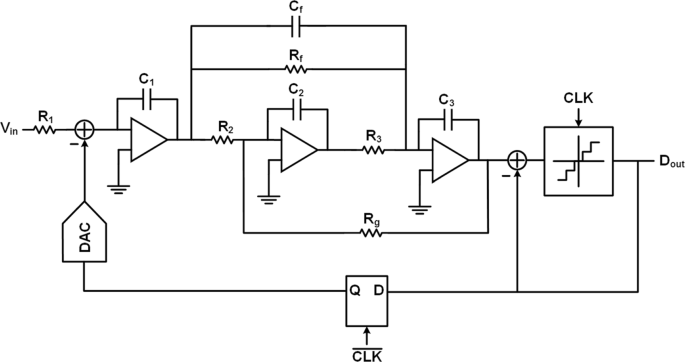

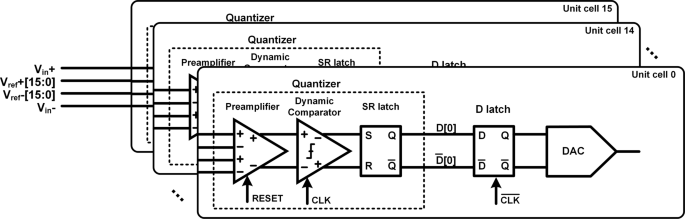

図1は、提案された3次CT Δの全体的な概略図を示しています。 Σ 簡略化のためのシングルエンド構造の変調器。 3次ノイズシェーピングは、DRとループの安定性の間で大きな妥協点を獲得します。提案された変調器は、12OSRで2.4GHzのサンプリングレートを持っています。 Δの比較的高いOSR Σ 変調器が100MHz BWを超えると、高いDRが保証されます。変調器には、3つのRC積分器、4ビットの量子化器と4ビットの電流ステアリングDACが含まれています。積分器は、高エネルギー効率のための革新的な低電力消費フィードフォワード増幅器によって実装されます。フィードバックDACには、量子化器の準安定要件を緩和するために、サンプリング期間の半分の追加遅延があります。パッシブ加算器によって実装され、量子化器によって直接駆動される高速フィードバックパスは、超過ループ遅延(ELD)補償を実現します。フィードフォワードトポロジは、帯域外の信号伝達関数を犠牲にして電力効率を高めるために採用されています。

提案されたシングルループ3次4ビットCTの全体的な概略図Δ Σ フィードフォワードトポロジーを備えた変調器

アンプの設計

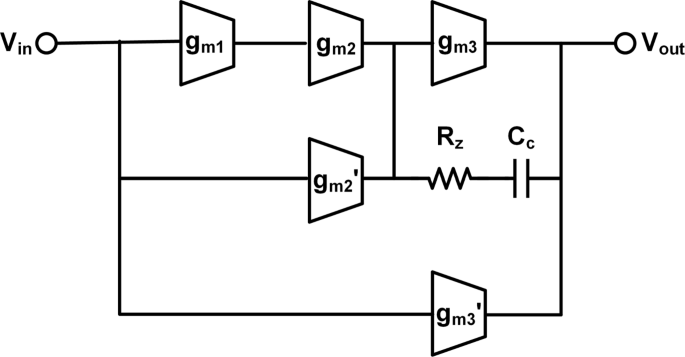

Δでは高いアンプゲインが必要です Σ 必要なノイズ変換機能を確保するための変調器。ただし、マルチGHzクロックレートを達成するために使用されるナノスケール技術は、低い固有ゲインに悩まされています。そのため、図2に示すように、十分なDCゲインを実装するために、3ステージアンプが採用されています。フィードフォワードトポロジとミラー補償を組み合わせて、ユニットゲイン帯域幅を減らすことなく位相マージンを改善します。フィードフォワードアンプは、適切なUGBWと位相マージン(PM)で高ゲインを実現するための一般的なソリューションの1つです。フィードフォワード経路によって引き起こされる左半分の平面ゼロは、極の負の位相シフトを効果的にキャンセルすると考えられています。フィードフォワードパス上の増幅器の高い相互コンダクタンスが必要であり、かなりの電力を消費します。バイアス電流を再利用するという利点のあるスキームは、電力を節約しますが、 g を制限します。 m 値。不十分な g m 通常、UGBWを超えてゼロが発生し、適切な位相マージンを提供できません。 UGBW全体の下にある最適化されたゼロは、ミラー補償コンデンサとヌル抵抗を追加することによって提供されます。

ミラー補償を備えた提案された3段フィードフォワード増幅器のトポロジー

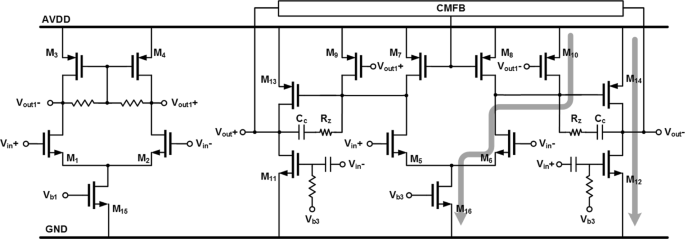

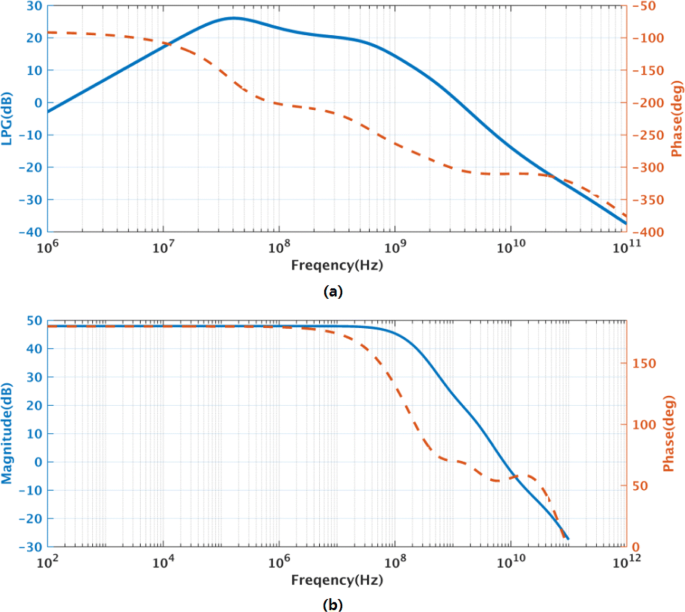

図3は、最初の積分器で使用される増幅器のトランジスタレベルの回路図を示しています。トランジスタ M 1−4 アンプの入力段を形成し、トランジスタは M 9,10 および M 13,14 それぞれ第2段階と第3段階を形成します。トランジスタ M 5−8 および M 11,12 2段目と3段目のアンプとバイアス電流を共有しながら、入力と出力の間に2つの高速フィードフォワードパスを作成します。第1ステージの出力コモンモード(CM)はローカルで固定されています。 2段目と3段目の出力CMは、CMFB増幅器 M を横切る2段目のフィードバックパスによって固定されます。 7,8 および M 13,14 。図4aは、すべての負荷がかかった最初の積分器の増幅器のシミュレートされたレイアウト後の開ループ応答を示し、図4bは閉ループ応答を示しています。最初のインテグレータは、3.6GHzのUGBWと57.8の ∘ を実現します。 1.2V電源から10.5mWを消費しながら、すべての負荷効果を備えたPMの2番目と3番目のインテグレータは同じトポロジを採用していますが、バイアス電流がスケーリングされており、UGBWが4.7および3.3 GHz、PMが58.0および57.8になっています ∘ それぞれ4.3および17.3mWを消費します。

増幅器のトランジスタレベルの回路図

1番目の積分器の増幅器のレイアウト後のシミュレーション結果。 a 開ループAC応答; b 閉ループAC応答

量子化器とDAC

図5に示す量子化器とDACの概略図として、それぞれが16個のユニットセルで構成されています。量子化器は、17タップの抵抗ラダーから生成された16レベルのエンコーダを備えた4ビットフラッシュADCとして実現されています。ループの安定性を確保するためにELDがサンプリング周期の半分未満に動作時間を要求する量子化器は、最大帯域幅の制限として重要なブロックです。

量子化器とDACの簡略化された回路図

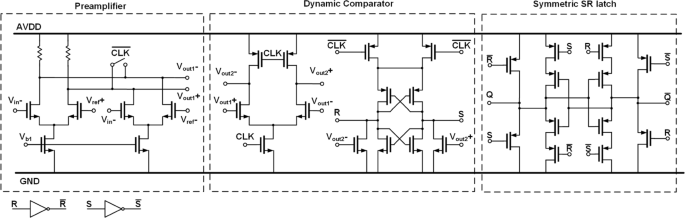

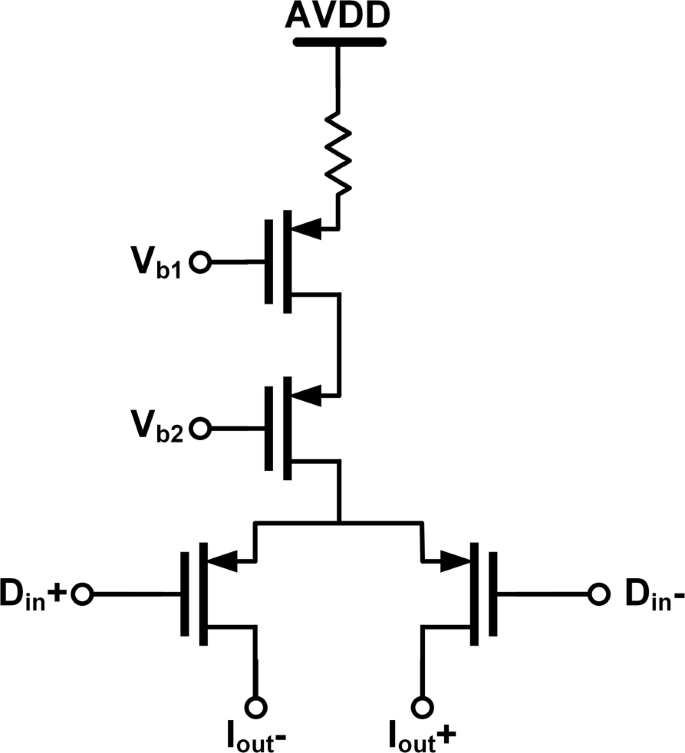

高速フラッシュADCを実装するために、図6に示すように、プリアンプ段、ダイナミックコンパレータ段、および対称セットアンドリセット(SR)ラッチ[12]で構成される3段コンパレータアーキテクチャが採用されています。入力換算オフセット低減用のプリアンプは、2つの抵抗性負荷差動ペアであり、リセットスイッチが出力間に接続されているため、迅速な回復が可能です。従来のダイナミックコンパレータとは異なり、差動ペアおよび交差結合インバータは2つの部分に分割され、低電圧電源のすべての電流パスでトランジスタの量を最小限に抑えます。クロックがハイレベルになると、ダイナミックコンパレータが入力に依存する比較決定を開始します。次に、クロックリターンがハイからローになると、各ダイナミックコンパレータの2つの出力が両方とも0にリセットされ、対称SRラッチの再生とラッチがトリガーされます。各ブランチでアクティブなトランジスタは1つだけであるため、対称SRラッチ構造により、強力な負荷駆動能力が得られます。それはかなりのスイッチオフ速度と低消費電力で小さなトランジスタサイズを可能にします。さらに、両方の出力信号の遅延が等しくなります。 DACユニットの前のDラッチは、クロック信号のレベルに対して低レベルに敏感であり、ELD期間の半分を保証します。電流ステアリングDACユニットのトランジスタレベルの回路を図7に示します。

提案された量子化器の1つの単位要素のトランジスタレベル回路

PNG電流ステアリングDACユニットエレメント

結果と考察

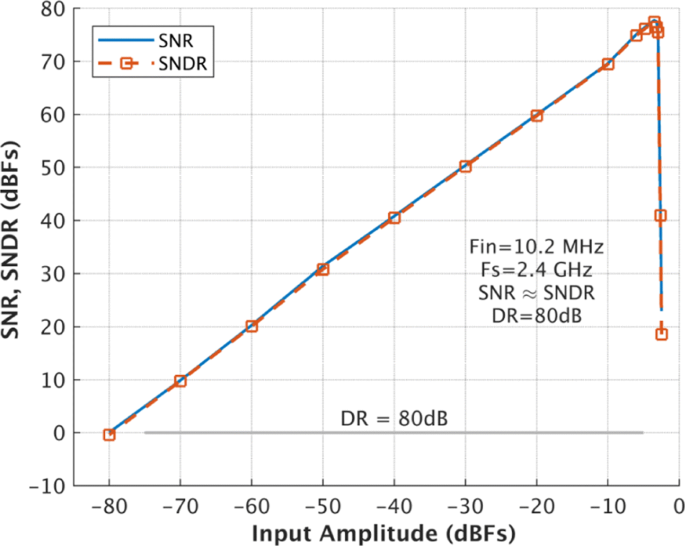

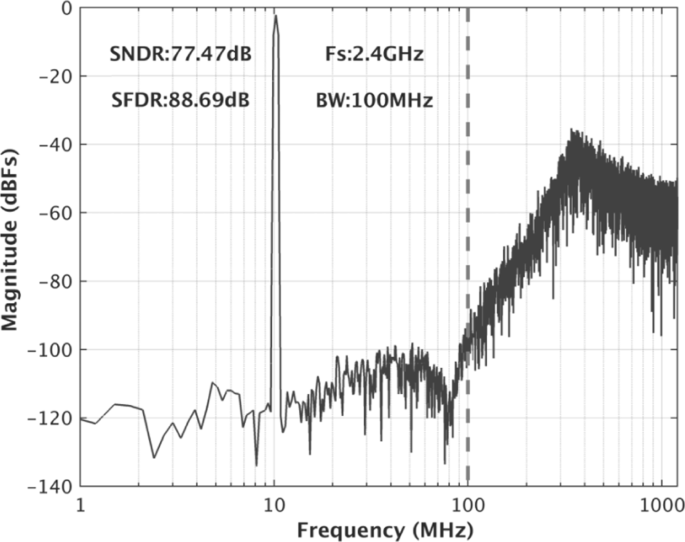

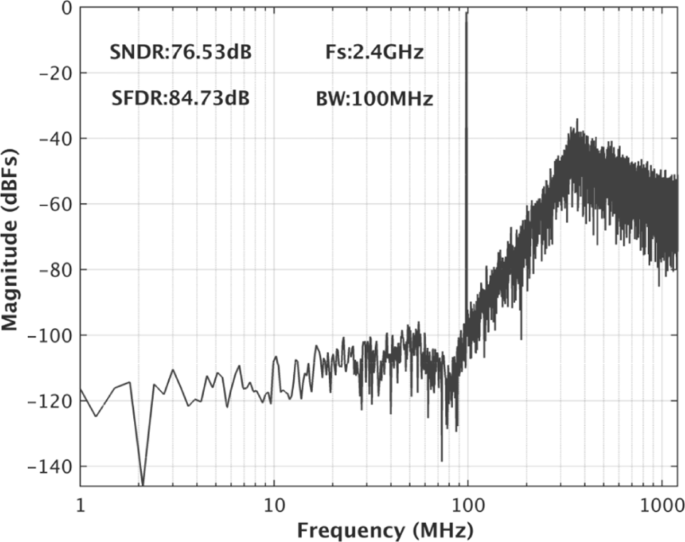

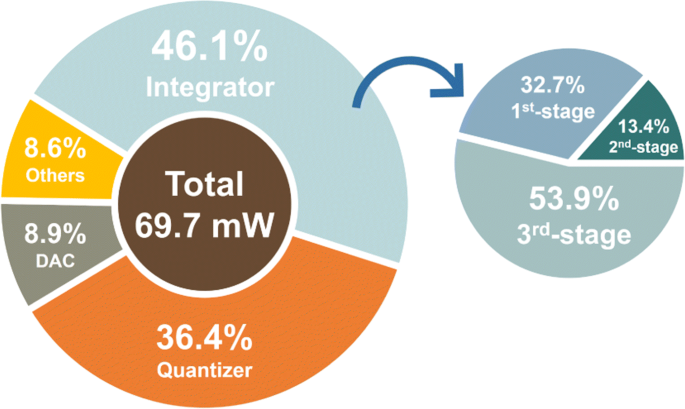

プロトタイプΔ Σ 変調器は40nmのCMOSプロセスに組み込まれています。図8に示す10.2MHzでのSNRおよびSDNRと入力振幅のシミュレーション後の結果として、80dBのDRが達成されます。図9と図10は、0dBFが2.4Vpp変調器のフルスケールに対応するため、それぞれ10.2MHzと97MHzで-3.52-dBFシングルトーン入力を使用してシミュレートされたスペクトルを示しています。 SNDRはそれぞれ77.47dBと76.53dBです。図11に示すように、変調器の消費電力は69.7mWです。積分器、量子化器、およびDACは、それぞれ32.1 mW、25.4 mW、および6.2mWを消費します。 6.0 mWの電力は、クロックバッファ、電流バイアス、電圧リファレンスなどの他の電流によって消費されます。変調器は、DRに基づいて171.6dBのシュライアーFOMを実現します。表1は、この作品を以前に公開されたいくつかの作品と比較しています。提案された変調器は、最高のFOMで広い帯域幅を実現します。

シミュレート後のSNRおよびSNDRと10.2MHz入力の入力信号振幅

10.2MHzでのシングルトーン入力によるポストシミュレーションスペクトル

97MHzのシングルトーン入力によるポストシミュレーションスペクトル

シミュレート後の消費電力の内訳

結論

この作業では、3次4ビットCT Δを提案しました。 Σ シングルループフィードフォワードトポロジーの変調器。この変調器は40nm CMOSプロセスで設計されており、2.4GHzのクロックレートで100MHzBWで80dBのDRを実現します。低電力消費増幅器の構造は高エネルギー効率を導き、変調器は1.2V電源から69.7mwを消費し、171.6dBのシュライアーFOMを達成します。

データと資料の可用性

この調査中に生成または分析されたすべてのデータは、この公開された記事に含まれています。

略語

- ADC:

-

アナログ-デジタルコンバーター

- BW:

-

帯域幅

- CT:

-

連続時間

- DR:

-

ダイナミックレンジ

- DT:

-

離散時間

- ELD:

-

過剰ループ遅延

- LTE-A:

-

ロングタームエボリューションアドバンスト

- OSR:

-

オーバーサンプリング比

- PM:

-

位相マージン

- UGBW:

-

ユニティゲイン帯域幅

ナノマテリアル

- Arduinoを使用したDIYの最もシンプルなIV9Numitron時計

- AION500MK3による高速3Dプリント

- 誘電体メタ表面を介した帯域幅の拡大による完全なテラヘルツ分極制御

- AFMチップベースの動的耕起リソグラフィーを使用したポリマー薄膜上での高スループットのナノスケールピットの製造

- RGOと3次元グラフェンネットワークが高性能でTIMを共同修正

- 高度に圧縮耐性のあるスーパーキャパシタ電極としての超弾性と高静電容量を備えたグラフェン/ポリアニリンエアロゲル

- ハイブリッド全誘電体-グラフェンメタ表面に基づく制御可能な複屈折を備えた偏光変換器

- 表面構造が変更された高性能有機ナノ構造シリコンハイブリッド太陽電池

- 高コンダクタンスのトポロジカル絶縁体ナノシートにおける非常に強化された光電流応答

- テラヘルツ範囲での吸収と偏光変換の切り替え可能な機能を備えた多機能デバイス

- 高PSRRのナノスケール低電力抵抗なし電圧リファレンス