Hf1-xZrxO2ゲート構造を備えた低電圧動作2DMoS2強誘電体メモリトランジスタ

要約

強電界効果トランジスタ(FeFET)は、その有望な動作速度と耐久性により、興味深い不揮発性メモリ技術として登場しました。ただし、分極を反転させるには、読み取りの電圧に比べて高い電圧が必要であり、セルの書き込みの消費電力に影響を与えます。ここでは、動作電圧が低いCMOS互換のFeFETセルについて報告します。強誘電体Hf 1-x を設計します Zr x O 2 (HZO)薄膜は、負の静電容量(NC)ゲート誘電体を形成します。これにより、数層の二硫化モリブデン(MoS 2 )に分極ドメインの反時計回りのヒステリシスループが生成されます。 )FeFET。安定化されていない負のコンデンサは、本質的にサブサーモニックスイングレートをサポートし、したがって、動作電圧の半分よりはるかに小さいヒステリシスウィンドウで強誘電分極を切り替えることができます。 FeFETは、10 7 を超える高いオン/オフ電流比を示します。 最小プログラム(P)/消去(E)電圧3Vで0.1Vの反時計回りのメモリウィンドウ(MW)。堅牢な耐久性(10 3 サイクル)および保持(10 4 s)プロパティも示されています。私たちの結果は、HZO / MoS 2 強誘電体メモリトランジスタは、サイズおよび電圧スケーラブルな不揮発性メモリアプリケーションで新しい機会を実現できます。

背景

システムオンチップ(SoC)組み込みメモリ市場は現在、驚異的な成長の時代にあり、メモリがより高速な動作、より小さなセルサイズ、およびより少ない消費電力を達成できる必要があります[1,2,3,4,5,6 ]。 2011年に強誘電性酸化ハフニウムが発見されたため、最も有望な候補の1つである強誘電体メモリが再検討されました[7]。

過去数十年間、FeFETは、メモリ動作のための低電圧要件、プロセスステップの単純さ、最小相補型金属酸化膜半導体(CMOS)統合プロセス、および限定された汚染の懸念など、これらすべての側面でうまく機能しませんでした[8,9,10、 11]。これに対処するために、最近、PbZrTiO 3 を含むさまざまな強誘電体材料に基づいて、2D FeFET不揮発性メモリ(NVM)に関する膨大な調査が行われています。 (PZT)、および[P(VDF-TrFE)]ポリマー[12,13,14,15,16,17,18]。これは、「ムーア以上の時代」における2D材料の有望な特性によるものです。 FeFETでは、トランジスタゲートスタックに組み込まれた強誘電体材料の2つの安定した自発分極状態が、印加された収縮P / Eゲート電圧によって可能になる制御可能なしきい値電圧を介したデータストレージに利用されます。再現性のあるヒステリシス動作、10 4 の高いオン/オフ比が報告されています。 、10 4 までの良好な保持特性 s、PZT / MoS 2 で安定したスイッチング動作を実現 FeFET [19]。注目すべきことに、最大移動度は625 cm 2 / V∙s、±26Vゲートで16Vの大分子量—電圧範囲と8×10 5 の高いオン/オフ比 n型[P(VDF-TrFE)]ポリマー/ MoS 2 によっても実証されています FeFET [15]。ただし、CMOSの互換性、スケーリング機能、Feと2D材料間の界面状態など、実際のアプリケーションを妨げる可能性のある基本的な問題が非常に多くあります。新しい強誘電体材料の一種である強誘電性酸化ハフニウムは、優れたCMOS互換性とスケーリング機能を備えており、今後5〜10年でサブ5nmテクノロジーノードの高度なFeFETNVMに役立つ可能性があります[20]。したがって、HfO 2 のバッチ ベースの誘電体スタックが2DFeFETに組み込まれ、サブ60 mV / decadeスロープとヒステリシスのない特性を介して急なON / OFFスイッチングを備えた負の静電容量電界効果トランジスタ(NCFET)を実現することを目的としています[21、22、23 、24、25、26]、代替の2Dチャネル材料を使用したNC誘電体スタックに基づく質量実験は素晴らしい結論を導き出しましたが、NCFETとFeFETを区別するためのサージ要件を強調しました。 MoS 2 に基づく1トランジスタ強誘電体メモリでのデバイス技術の物理学と実行可能性に関する体系的な調査はまだ不足しています。 および強誘電性HZO。

この作業では、数層のHZO MoS 2 を備えたFeFET トランジスタが提案されています。収縮したP / E電圧の下でゲートスタックエンジニアリングによって誘発されるNC効果を介してP / E電圧をスケーリングすることができます。 HZO MoS 2 で、反時計回りのMW 0.1 V、サブ60 mV / decadeスロープが達成されたことを実験的に示しました。 FeFET。これは、強誘電性双極子の高速フリッピングによる2Dチャネルの局所キャリア密度変調に起因する可能性があります。 HZO / MoS 2 のヒステリシスが減少したためです。 ドレイン電圧としてのFeFETは、負のドレイン誘導障壁低下(DIBL)効果に増加します。さらに、保持、耐久性、およびしきい値電圧のHZO MoS 2 のドレイン電圧への依存性についても体系的に調査しました。 FeFET、HZO MoS 2 を設計するための実行可能な経路を開く FeFETNVMとその実用的なアプリケーション。

メソッド

6 nmHf 1-x Zr x O 2 フィルムと2nmAl 2 O 3 p + にデポジットされました 300°CでALDを使用し、[(CH 3 ) 2 N] 4 Hf(TDMAHf)、[(CH 3 ) 2 N] 4 Zr(TDMAZr)、およびH 2 それぞれ、Hf前駆体、Zr前駆体、および酸化剤前駆体としてのO蒸気。続いて、基板はN 2 で450°Cで30秒間ラピッドサーマルアニーリング(RTA)を受けました。 アンビエント。その後、数層のMoS 2 フレークは機械的に剥離され、基板上に転写されました。 p + の直径 HZO(6 nm)/ AI 2 の堆積に使用されるSi基板 O 3 (2 nm)は6インチです。電子ビームリソグラフィー(EBL)を使用して、ポリ(メチルメタクリレート)(PMMA)A5レジストのコンタクトパッドをパターン化しました。スピンパラメーター、ベーキングパラメーター、およびイメージングパラメーターは、それぞれ500 r / min(9 s)+ 4000 r / min(40 s)、170°C(5 min)、MIBK:IPA =1:3(15 s)です。 。次に、ソース/ドレイン電極(Ti / Au、厚さ5/65 nm)を電子ビーム蒸着(EBE)システムを使用して蒸着し、アセトン溶液でエッチングしました。リフトオフ後、デバイスを300°Cで2時間アニーリングして、接触を強化しました。製造したMoS 2 の電気的特性評価を実施しました マイクロマニピュレーターを備えたプローブステーションを使用した/ HZO電界効果トランジスタ。バックゲート電圧( V GS )は、p型の高濃度にドープされたSi基板に適用されました。半導体特性評価システム(PDA)を使用して、ソース-ドレイン電圧( V )を測定しました。 DS )、バックゲート電圧( V GS )、およびソース-ドレイン電流( I DS 。

結果と考察

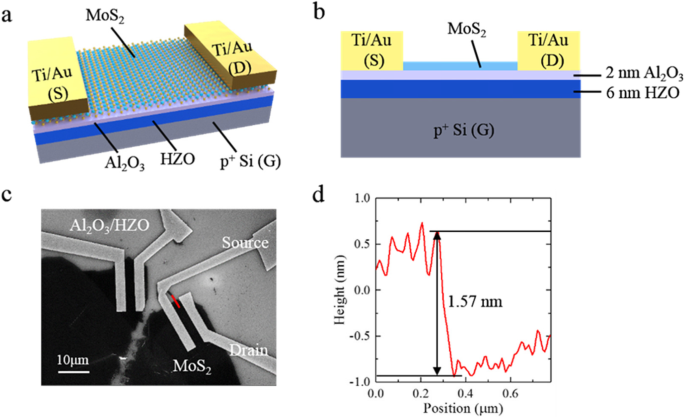

数層のMoS 2 を用意しました バルク結晶の機械的剥離とMoS 2 の転写による 2nmのAl 2 へのナノフレーク O 3 / 6 nmHZO / p + Si基板(「実験」セクションの詳細を参照)。図1aおよびbは、HZO / MoS 2 の3D概略図と断面図を示しています。 それぞれFeFET構造。 HZO / MoS 2 の上面走査型電子顕微鏡(SEM)画像 FeFETを図1cに示します。 MoS 2 の幅と長さ チャネルはそれぞれ2μmと12μmです。図1dに示すように、MoS 2 の厚さ チャネルは、原子間力顕微鏡(AFM)を使用して確認されました。測定された1.57nmの厚さは、MoS 2 の4層の存在を示しています。 [26]。

MoS 2 のデバイス構造と基本特性 / HZOFeFET。 a MoS 2 の3次元概略図 / HZOFeFET。 b MoS 2 の概略断面図 / HZOFeFET。 c 作製したMoS 2 の上面SEM画像 / HZO FeFET、Ti / Auソース/ドレイン電極、HZO強誘電体ゲート絶縁体、およびMoS 2 チャネル。 d c の赤い線に沿った接触モードAFMを使用した高さプロファイル 、MoS 2 の高さを検証します チャネル。

図S1cおよびdに示すように、HZOの元素および結合組成をX線光電子(XPS)測定によって調べました。ピークは19.05eV、17.6 eV、185.5 eV、および183.2 eVであることがわかり、これらはHf 4f 5/2 に対応します。 、Hf 4f 7/2 、Zr 3d 3/2 、およびZr 3d 5/2 、それぞれ[27]。図S1eの深さプロファイルに沿った原子濃度は、Al 2 の分布をさらに確認します。 O 3 / HZO / p + Si三層構造。上記のすべてにより、原子層堆積(ALD)システムを介して成長したHZO膜が高度に結晶性であることが確認されます。

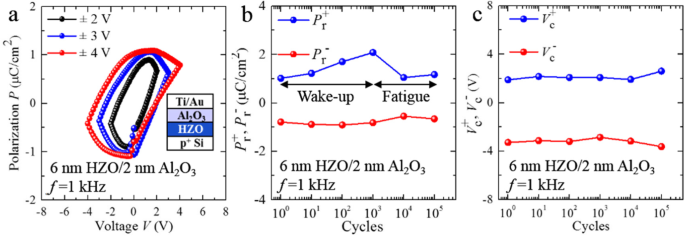

HZO / MoS 2 の特性を調査する前に FeFET、Au / 2 nmAl 2 の強誘電挙動 O 3 / 6 nmHZO / p + 分極電圧測定を使用したSiゲートスタックを図2aに示します。明らかに、私たちが製造した6 nmHZO / 2 nmAl 2 O 3 コンデンサは、分極電圧ヒステリシスループを示します(1 kHzで測定)。一方、残りの分極 P r と強制電圧 V c 最大掃引電圧の増加とともに増加します。これは、 P-V を意味します。 ヒステリシスループはマイナーループからメジャーループに変換されます。最大掃引電圧が2から4Vに増加すると、 P r 0.66μC/ cm 2 に達する 、0.86μC/ cm 2 、および1.1μC/ cm 2 、それぞれおよび V c それぞれ1.12V、1.9 V、2.04Vに達します。抽出された P r および V c 10 5 以内 耐久性のあるDC掃引サイクルを図2bおよびcに示します。明らかに、10 5 以内の有意な覚醒と倦怠感の影響 サイクルは6nmHZO / 2 nmAl 2 で観察されます O 3 コンデンサ。目覚めと疲労は、電場下の酸素空孔の拡散と再分布に起因する可能性があります。疲労効果は、一般に、酸素空孔に関連する欠陥サイトでの電荷トラップに関連しています[28]。 PRphase のヒステリシス動作 PRampl の蝶の形をしたループ ピエゾ応答力顕微鏡(PFM)を使用して図S1bおよびcに表示され、掃引バイアス電圧の関数としての偏光スイッチングを示しています。分極電圧測定とピエゾ応答電圧測定の間の異なる接触抵抗を考慮して、測定された V c 図S1bおよびcは、図2aで得られた値とそれほど一致していません。

a HZO(6 nm)/ Al 2 のP-Vヒステリシスループ O 3 (2 nm)異なる電圧掃引範囲のコンデンサ。 ( b の依存関係 ) P r および c V c HZO(6 nm)/ Al 2 のサイクリングについて O 3 (2 nm)±4 V / 1kHzサイクリングのコンデンサ

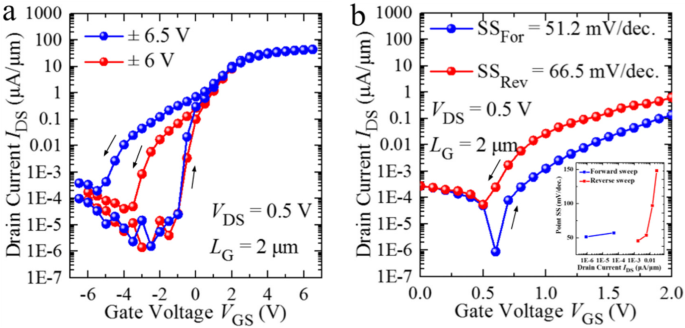

さらに、ゲート電圧の掃引電圧範囲( V )の上昇に伴い、MWが増加することが観察されています。 GS、範囲 )。通常、多結晶HZO膜はマルチドメイン状態として存在し[29]、これらのドメインの強制場分布はガウス分布を満たします。したがって、上昇した V への依存度が高くなる必要があります。 GS、範囲 。強制的に提出された E C 残留分極をゼロに減らすことができる外部電界の値に対応します。したがって、 V GS 、範囲 HZOフィルムの分極を切り替えるために使用されるものは、関連する強制電圧 V が高くなると大きくなります。 C 。これが、HZOフィルムの分極電圧ループがより大きな V で拡張される理由です。 GS、範囲 、これは図2aに示されています。言い換えると、 V を上げると、分極強度と強誘電体スイッチングが向上します。 GS、範囲 、増加した V によって生成される拡張された反時計回りのMWの前述の現象につながります GS、範囲 。 V で GS、範囲 =(-2、2 V)、MWはほとんど消失し、ほぼヒステリシスのない特性が現れます。これは、強誘電体スイッチングの効果と電荷トラップ/デトラップの効果の間のほぼ完全な補償を意味します。

強誘電体スイッチングの影響をさらに調査するために、 V GS、範囲 (-6、6 V)および(-6.5、6.5 V)に継続的に増加しています。測定された I DS - V GS HZO MoS 2 の曲線 V でのFeFET GS、範囲 =(-6、6 V)、および(-6.5、6.5 V)を図3aに示します。同様に、反時計回りのメモリウィンドウは、拡張された V で増加します。 GS、範囲 。 V で GS、範囲 =(− 6.5、6.5 V)、反時計回りのMWは4 Vを超え、オン/オフ比も10 7 に増加します。 これは、より大きな外部印加電圧の下での分極スイッチングの強化によるものです。一般に、 I に示されているヒステリシス動作の根底にあるメカニズム DS - V GS V の双方向スイープ中の曲線 GS はしきい値電圧シフトであり、これは分極スイッチングの主な効果、つまりNC効果[30,31,32]によって変更でき、反時計回りのヒステリシスをもたらします。改善された閾値下特性のさらなる研究は、収縮した V の下で他のデバイスで実行されました。 GS、範囲 。測定された I DS - V GS 抽出されたポイントSS— I DS V での他のデバイスの曲線 GS、範囲 =(-3、3 V)が図3bにプロットされています。 V で GS、範囲 =(− 3、3 V)、HZO / MoS 2 FeFETはSS For を展示しています =51.2 mV / decadeおよびSS Rev =それぞれ66.5mV / decade。つまり、HZO / MoS 2 では、サブ60 mV / decadeのSSと0.48VのMWを同時に達成できます。 室温でのFeFET。NCFETとFeFETを区別するためのヒントになります。

HZO / MoS 2 の直流(DC)テスト ドレイン電圧( V )時のFeFET DS )は0.5Vです。 a バックゲート電圧の最大値として6Vと6.5Vの伝達曲線の比較。 b V の0〜-2V間隔での伝達曲線の拡大図 GS、範囲 =(− 3、3 V)。ドレイン電流( I )の関数としてのポイントサブスレッショルドスロープ(SS) DS )HZO / MoS 2 の FeFETは( b )はめ込み。デバイスはSS For を示します =51.2 mV / dec

知られているように、NCFETでは、負のゲート誘電容量( C )が組み込まれているため、SSは室温で60 mV / decadeよりも小さくなる可能性があります。 ins )、これはd P の負の勾配セグメントを介して取得できます / d E <0は強誘電体膜によって誘発され、ゲートスタック係数(m)<1に寄与します。NC効果の根底にあるメカニズム[33]は、強誘電体膜によって生成される脱分極場です[34,35,36,37,38]。強誘電体膜の界面での不完全なスクリーニングのために[39]、残留分極電荷が強誘電体膜の両端に内部電界を生成し、外部から印加された電圧と反対方向になり、再印加につながる可能性があることが実験的に報告されています。 「電圧増幅効果」と呼ばれる、ゲートスタックと増幅されたチャネル表面電位の両端の電圧の分布[40、41、42]。電圧増幅は通常、チャネル表面電位の加速された変化とそれに続くブーストされた値の2つの部分に分けることができ、急なON / OFF切り替えと改善された I を提供します。 オン / 私 オフ 、 それぞれ。ただし、FeFETについては、別の話があります。強誘電体コンデンサー間の静電容量マッチングの概念によると( C FE )および金属酸化物-半導体静電容量( C MOS )[43,44,45]、| C の場合 FE |> C MOS 、理論上の総静電容量( C 合計 )は正であり、システムは安定しているため、 V の双方向スイープ中に同じ偏光動作が発生します。 GS 安定したヒステリシスのないNCFET。ただし、 C の両方が存在するため、SSと相互コンダクタンスの改善をもたらす良好なマッチングを実現するのは非常に困難です。 MOS および C FE 非常に非線形で、バイアスに依存するコンデンサです。さらに、| C FE |> C MOS ヒステリシスを回避するために、すべての動作電圧範囲を確保する必要があります。代わりに、一度| C FE | < C MOS 、理論上の C 合計 が負であり、システムが不安定である場合、 V のバイスイッチング中に分離分極動作が発生する必要があります GS C を維持する 合計 正の値。これにより、NVMアプリケーションのFeFETで反時計回りのヒステリシスが発生する可能性があります。ここで、ヒステリシス挙動は、分離された偏光スイッチングのその後の効果であると述べられています。これは、ヒステリシスウィンドウの幅が、の変化によって操作できるなどの静電容量マッチングの概念に基づいて簡単に変更できることを意味します。 i> V DS 。 V が大幅に縮小されている場合でも、適切な静電容量のマッチングが必要です。 GS、範囲 =(− 3、3 V)、HZO / MoS 2 FeFETは依然として明らかなヒステリシスウィンドウを示し、SS For の急なスイッチングを示します。 =51.2 mV / dec同時に、これはサブスレッショルド領域にもNC効果(強誘電分極効果)が存在することをさらに示唆しています。 NCFETとFeFETは異なりますが、FeFETは、同等の小さいMW、深いサブ60 mV / dec SS、および高い I を維持するロジックデバイスとして採用することもできます。 オン / 私 オフ NC効果による比率も。

V の影響 DS MWの幅については注意深く調査されています。 私 DS - V GS さまざまな V での対数目盛の曲線 DS 図S3に示されています。固定された V で GS、範囲 =(− 2、2 V)、 V の値 GS I で抽出 DS = V の双方向スイープの場合は70nA GS すべて負の方向にシフトします。一方、 V の前方掃引の変動も示されています GS 逆掃引よりもはるかに明白であり、負のDIBLの重要な現象を示しています。負のDIBL効果は常にNC効果で発生することに注意する必要があります[46、47]。

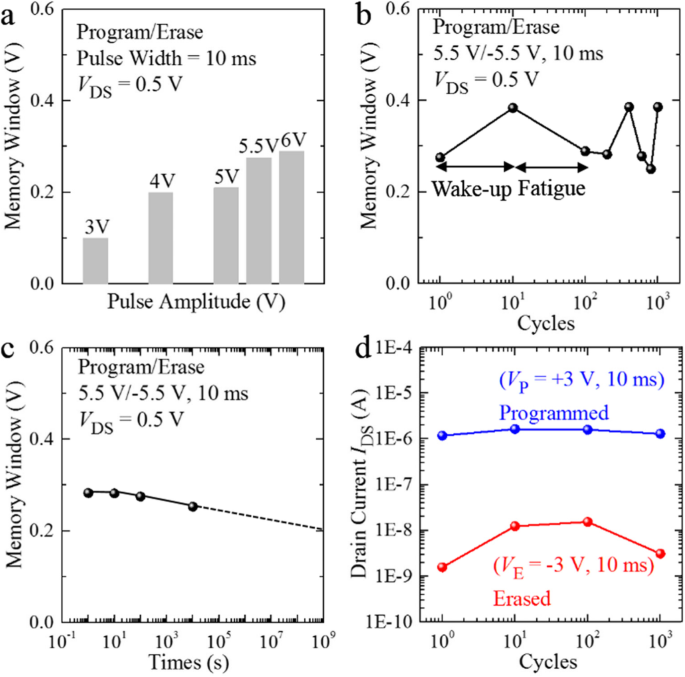

上記のHZO / MoS 2 の直流(DC)テスト後 FeFETでは、さまざまなP / E V のMWをさらに測定しました。 GS 図4aの幅10msのパルス。 MWは、最大変化Δ V として定義されます。 TH P / E V の後 GS パルス。パルス V の間 GS アプリケーションでは、他の端子は V に固定されました S = V D =0V。読み取り(R)操作の場合、 V GS V で-1Vから1Vの範囲でした D =0.5Vおよび V S =0V。図4aに示すように、抽出されたMWはP / E V として大きくなります。 GS パルスが増加します。課されたP / E V の場合 GS パルスは±3V、抽出されたMWは0.1Vです。課されたP / E V の場合 GS パルスは±5.5V、抽出されたMWは0.275 Vです。図3aおよびbの反時計回りのMWと比較すると、P / E V 後の抽出されたMWは4Vおよび0.48Vです。 GS 脈拍が大幅に減少します。これはおそらく、空気中の高湿度によって引き起こされるトラップ状態の密度が高いためです[48]。したがって、電荷トラップ/デトラップメカニズムが強化され、反時計回りのヒステリシスループが最終的に減少します。さらに、HZO / MoS 2 のサイクリング耐久性とデータ保持について調査しました。 図4bの高さ±5.5VのP / Eパルス下のFeFET。プログラム V GS パルスの幅は10ミリ秒で、 V S = V D =0V。図4bは、耐久サイクルの関数として測定されたMWを示しています。耐久性サイクルは、バックゲート電圧の周期的なP / R / E / Rパルスによって形成されます。 P、E、Rの高さのバックゲートに印加される電圧は、それぞれ+ 5.5 V、-5.5 V、0Vでした。そして、PとEのパルス幅は10msでした。明らかに、0.3VのMWは10 3 後に大幅な劣化なしに維持できます。 P / Eサイクル。耐久サイクルの数が増えると、MWは10サイクル後に0.38 Vに増加し、600サイクル後に0.28Vに戻ります。最初に広がったMWはウェイクアップ効果と呼ばれ、後で縮小したMWは疲労効果と呼ばれます。ウェイクアップ効果は磁壁のピン止め解除に対応し、HZO膜の切り替え可能な偏光ドメインの増加につながります[49]。疲労効果は、多数のP / Eサイクルの後に磁壁を固定する新しく注入された電荷に対応します[50]。室温でのデータ保持を図4cに示します。ここでは、MWの低下は10 4 以降は無視できます。 s。したがって、点線の外挿線により、約0.3VのMWが10年以上持続可能であると期待できます。図4dに示すように、デバイスは10 3 以降は安定しています。 ±3Vの高さのP / Eパルスの下でサイクルします。 HZO / MoS 2 の安定性 FeFETは、不揮発性メモリ技術のアプリケーションの優れた展望を示しています。

HZO / MoS 2 のメモリパフォーマンス P / Eパルス下のFeFET。 a ±3V、±4 V、±5 V、±5.5 V、および±6Vの高さのP / Eパルスの下で抽出されたMW(MW)。 b P / Eパルス条件下での耐久性測定。 c HZO / MoS 2 の保持特性 FeFET。 d HZO / MoS 2 の耐久性 10 3 のFeFET ±3Vの高さのP / Eパルスの下でのサイクル

MoS 2 を組み合わせたFeFETベースのデバイスと性能指数の比較 表1に、強誘電体ゲート誘電体を示します。ここでは、デバイス構造、残留分極、強制電界、ヒステリシスループ方向、MW、動作電圧、耐久性サイクル、および保持時間を示します。私たちが製造したデバイスは、6 nm HZOの最も薄い強誘電体層を示し、他の作品と比較して最も低い動作電圧を示していることは明らかです[12、13、14、15、16、17、18]。これは将来の2nmにとって重要です。または、バックエンドオブライン(BEOL)メモリの3nmプロセスノード。強誘電体層の厚さをスケーリングすることにより、±3Vの低い動作電圧で約0.1VのMWが達成されました。このような低い動作電圧は、Pなどの対応するものと比較したHZO層の固有の特性に起因する可能性があります。 (VDF-TrFE)またはHfO 2 、はるかに厚いです。さらに、私たちのデバイスは、より低い残留分極 P を持っています r 1.1μC/ cm 2 他の報告されたFeFETと比較して。 FeFETの保持損失の急速な減衰は、脱分極場 E の存在によるものです。 dep 、Al 2 の存在による不完全な電荷補償に起因します O 3 層。ここで、 E dep 残留分極 P に正比例します r [51]。したがって、高い E c と低い P r 比率を E にします dep / E c MoS 2 で / HZO FeFETは非常に小さく、脱分極場効果に関連する保持損失は非常に小さくなります。 MoS 2 の保持性能は HZOとP(VDF-TrFE)に基づくFeFETは、どちらも約10 4 です。 s、P(VDF-TrFE)フィルムは150nmである必要があります[17]。

<図>結論

結論として、数層のMoS 2 を調査しました。 HZOバックゲート誘電体を使用したベースの強誘電体メモリトランジスタデバイス。私たちが製造したデバイスは、強誘電分極によって引き起こされる反時計回りのヒステリシスを示します。さらに、HZO / MoS 2 強誘電体メモリトランジスタは、優れたデバイス性能を示しました。10 7 を超える高いオン/オフ電流比 そして、3VのP / E電圧で0.1Vの反時計回りのMWは、耐久性(10 3 サイクル)および保持(10 4 s)パフォーマンス。したがって、MoS 2 の結果は ベースの不揮発性強誘電体メモリトランジスタは、2D低電力不揮発性メモリアプリケーションの将来に有望な展望を示しています。

データと資料の可用性

著者は、資料、データ、および関連するプロトコルが読者に利用可能であり、分析に使用されるすべてのデータがこの記事に含まれていることを宣言します。

ナノマテリアル

- トランジスタの定格とパッケージ(BJT)

- AC回路のいくつかの例

- American Control Electronics:スナップオンプログラマブルボードオプション付きの低電圧DCドライブ

- 電気触媒水素発生のための制御された厚さのMoS2

- スーパーキャパシターの電極材料としての階層的多孔質構造を持つ単分散カーボンナノスフェア

- 電気抵抗率の低いUV硬化インクジェット印刷された銀ゲート電極

- スパイラル型アンテナによるマイクロブリッジ構造のTHzマイクロボロメータの周波数変調と吸収改善

- GeSiSnナノアイランドと歪み層を備えた半導体膜の形態、構造、および光学特性

- HfO2欠陥制御層を備えた単層カーボンナノチューブが支配的なミクロンワイドストライプパターンベースの強誘電体電界効果トランジスタ

- T型ゲートデュアルソーストンネル電界効果トランジスタのアナログ/ RF性能

- 低電圧制御市場の成長