切り替え可能な酸素空孔双極子によって可能になるZrO2強誘電性電界効果トランジスタ

要約

この論文では、ポストラピッドサーマルアニーリング(RTA)とZrO 2 の厚さの影響を調査します。 分極について P TaN / ZrO 2 の電気的特性 それぞれ/ GeコンデンサとFeFET。 350〜500°Cの範囲のRTAの後、TaN / ZrO 2 2.5および4nmの厚さのアモルファスZrO 2 を備えた/ Geコンデンサ フィルムは安定した P を示します 。強誘電性の振る舞いは、酸素空孔と負電荷によって形成された電圧駆動双極子の移動に起因することが提案されています。 2.5 nm、4 nm、および9nmのZrO 2 を備えたFeFET 100 nsのプログラム/消去パルスで適切なメモリウィンドウ(MW)を示します。厚さ4nmのZrO 2 FeFETは、2.5nmおよび9nmのZrO 2 を備えたデバイスと比較して、疲労および保持特性が大幅に向上しています。 。 ZrO 2 の保持パフォーマンス FeFETは、RTA温度の上昇とともに改善できます。 MWが約0.46Vであると推定され、4nmのZrO 2 を備えたデバイスで10年以上維持されます。 。

背景

ドープされたpoly-HfO 2 強誘電性電界効果トランジスタ(FeFET)は、CMOSプロセスとの互換性があるため、不揮発性メモリ(NVM)アプリケーションでかなりの関心を集めています[1]。まともな電気的性能はドープされたHfO 2 で実証されていますが ベースのFeFET [2]には、斜方晶相を形成するために必要な500°Cのアニーリングという高い熱収支や、強誘電体の厚さの縮小に伴う粒界に沿った望ましくないリーク電流など、いくつかの基本的な制限が依然として実際のアプリケーションを悩ませています。強誘電体は、Sb 2 など、さまざまな材料で広く観察されています。 S 3 ナノワイヤー[3]、GaFeO 3 フィルム[4]、LaAlO 3 -SrTiO 3 フィルム[5]、およびアモルファスAl 2 O 3 ナノ結晶を含む[6、7]。最近、部分的に結晶化したZrO 2 を備えたFeFETを報告しました。 NVMおよびアナログシナプスとして機能するゲート絶縁体[8]。 ZrO 2 トランジスタは、報告されているドープされたHfO 2 と比較して、より薄い厚さでまともな電気的性能を示しました。 、ZrO 2 の強誘電性の根本的なメカニズム フィルムは不明なままです。切り替え可能な分極の起源を解明することは重要かつ重要です P ZrO 2 のパフォーマンス制限を評価するため FeFET。

この作品では、TaN / ZrO 2 2.5 nm、4 nm、および9nmの厚さの絶縁体を備えた/ GeFeFETが製造されます。切り替え可能な P TaN / ZrO 2 で / Geコンデンサは、電圧駆動の酸素空孔と負電荷の移動に起因するものとして提案されています。 ZrO 2 の影響 P の厚さとポストラピッドサーマルアニーリング(RTA) TaN / ZrO 2 の / Geと、FeFETのメモリウィンドウ(MW)、耐久性、および保持特性が調査されます。

メソッド

ZrO 2 を使用したFeFET ゲート絶縁体は4インチで製造されました。 [8、9]の同様のプロセスを使用したn-Ge(001)基板。希釈HF(1:50)溶液でのゲート前洗浄後、Geウェーハを原子層堆積(ALD)チャンバーにロードしました。 ZrO 2 2.5 nm、4 nm、および9 nmの厚さの膜は、TDMAZrおよびH 2 を使用して250°Cで堆積されました。 それぞれZrとOの前駆体としてのO。厚さ100nmのTaNゲート電極を反応性スパッタリングによって堆積させた。ゲート電極形成後、ソース/ドレイン(S / D)領域にBF 2 が埋め込まれました。 + 1×10 15 の用量で cm −2 そして20keVのエネルギー。リフトオフプロセスにより、合計15nmのニッケル(Ni)S / D接点が形成されました。最後に、350、450、500°Cで30秒間のRTAを実行しました。

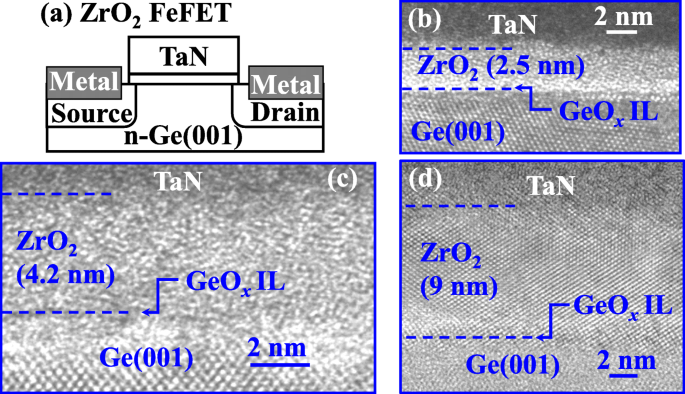

図1aに、製造されたトランジスタの概略図を示します。図1b–dは、TaN / ZrO 2 の透過型電子顕微鏡(TEM)画像を示しています。 2.5、4、および9nmの厚さのZrO 2 を含む/ Geサンプル 、 それぞれ。すべてのサンプルは、500°Cで30秒間RTAを受けました。 2.5 nmZrO 2 アニーリング後、サンプルは絶縁膜のままです。 4 nmのサンプルでは、いくつかのナノ結晶が観察されますが、ZrO 2 アモルファス層であり続けます。 9 nm ZrO 2 では完全な結晶化が発生しますが、 映画。特に、GeO x の界面層(IL) ZrO 2 の間に存在します TEM画像で観察するには薄すぎるが、Geチャネル領域。

a 製造されたTaN / ZrO 2 の概略図 / GeFeFET。 b 、 c 、および d TaN / ZrO 2 のHRTEM画像 / Geスタックと異なるZrO 2 厚さ。サンプルは500°Cで30秒間RTAを受けました

結果と考察

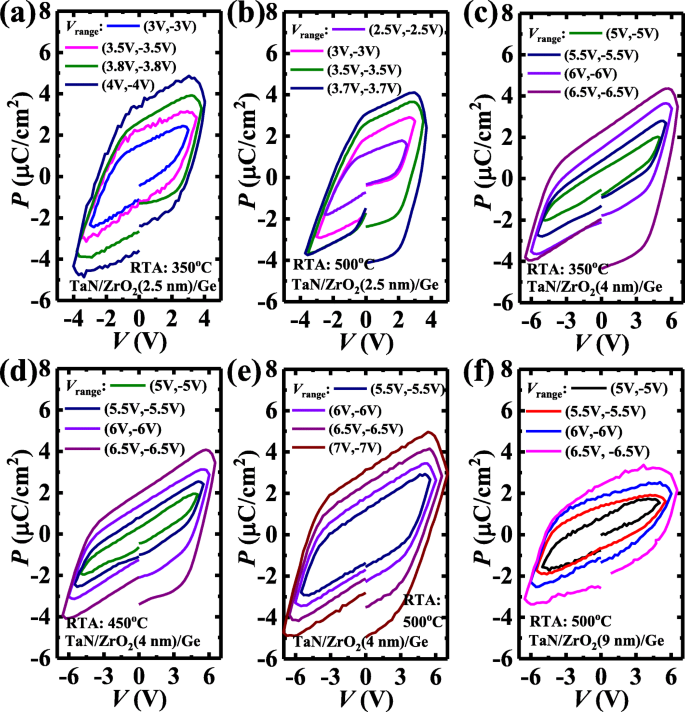

図2は、 P を示しています。 対電圧( V )TaN / ZrO 2 の曲線 異なるZrO 2 の/ Geコンデンサ 厚さと異なるアニーリング温度。異なる色の実線は、さまざまな掃引電圧範囲( V )のマイナーループを表しています。 範囲 )。測定周波数は1kHzです。 2.5nmおよび4nm ZrO 2 デバイスは、350°CでのRTA後に安定した強誘電性を示すことができます。図3は、残りの P をプロットしたものです。 ( P r )スイープ V の関数として さまざまな温度でアニールされたコンデンサの範囲曲線。

測定された P 対 V TaN / ZrO 2 の特性 異なるZrO 2 の/ Geコンデンサ 厚さとさまざまなアニーリング温度

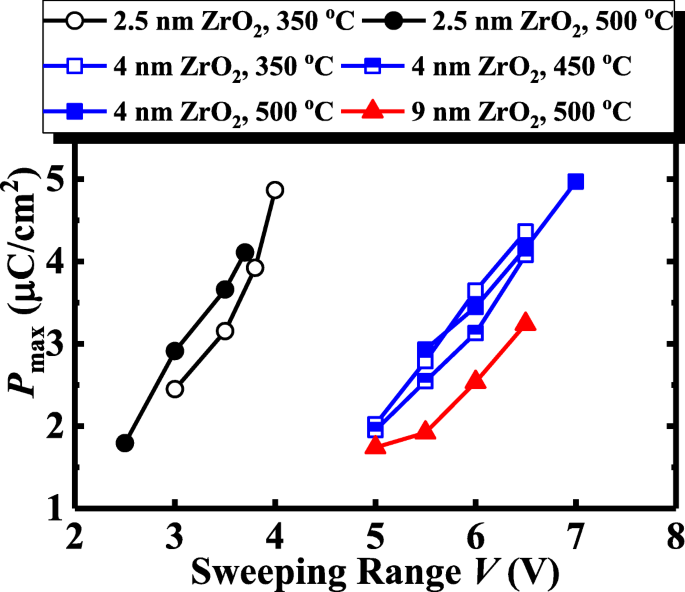

P の比較 max V の関数として 範囲 TaN / ZrO 2 の場合 異なるZrO 2 の/ Geコンデンサ 厚さとさまざまなアニーリング温度

図3は、 P の比較を示しています。 max V の関数として 範囲 TaN / ZrO 2 の場合 異なるZrO 2 の/ Geコンデンサ 厚さとさまざまなRTA温度。 4 nm ZrO 2 の場合 デバイスでは、アニーリング温度が350から450°Cに上昇すると、 V が大きくなります。 範囲 固定の P を取得するには max 。これは、アニーリング温度が高いほど、Ge / ZrO 2 の間に厚い界面層(IL)が生成されるためです。 およびZrO 2 / TaNインターフェースにより、統一された静電容量の等価厚さ(CET)が大きくなります。 2.5 nm ZrO 2 の場合 コンデンサの場合、500°Cのアニーリングを行ったサンプルの V は低くなります。 範囲 同じ P の350°Cアニーリングサンプルよりも max 。 RTA温度が高くなると、ILは厚くなりますが、一部のZrO 2 界面での脱酸素と相互拡散によって消費されました。非常に薄いZrO 2 の場合 デバイス、後者が支配的です。 2.5nmのZrO 2 との比較 コンデンサ、はるかに大きい V 範囲 同様の P を達成するには max 。ただし、9 nm ZrO 2 コンデンサはより高い V を示しません 範囲 4nmデバイスと比較して。これは、結晶ZrO 2 によるものです。 κがはるかに高い アモルファス膜よりも価値が高く、9nmデバイスのCETが大幅に低下します。

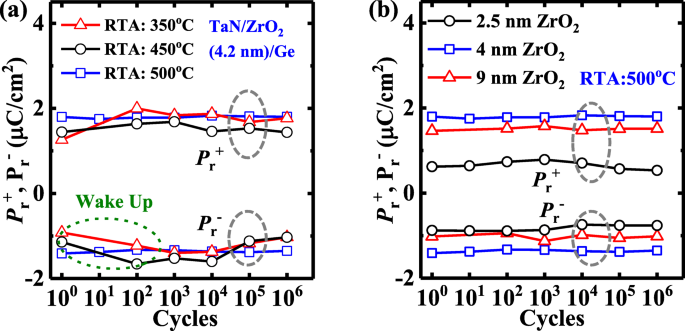

図4aは、正と負の P の抽出された進化を示しています。 r 、4 nmの場合、それぞれ\({P} _ {\ mathrm {r}} ^ {+} \)および\({P} _ {\ mathrm {r}} ^ {-} \)で示されます-厚いZrO 2 10 6 を超えるさまざまな温度でのRTAを備えたコンデンサ 1kHzで測定された掃引サイクル。 350°Cおよび450°Cでアニールされたデバイスは、明らかなウェイクアップ効果を示します。 4 nm ZrO 2 では、ウェイクアップやインプリントは観察されません。 強誘電体コンデンサは500°Cでアニーリングされました。図4bは、 P を比較しています。 r 異なるZrO 2 を持つデバイスのスイープサイクルの関数として 厚さ。 4 nmZrO 2 強誘電体コンデンサは、 P の安定性を向上させます r 10 6 の間の2.5nmおよび9nmデバイスと比較した耐久性 耐久性テスト。

a P r 対4nm ZrO 2 のmsパルス掃引サイクル数 RTA温度が異なるコンデンサ。 b P r 対ZrO 2 のmsパルス掃引サイクル数 500°Cでアニーリングした後のコンデンサ

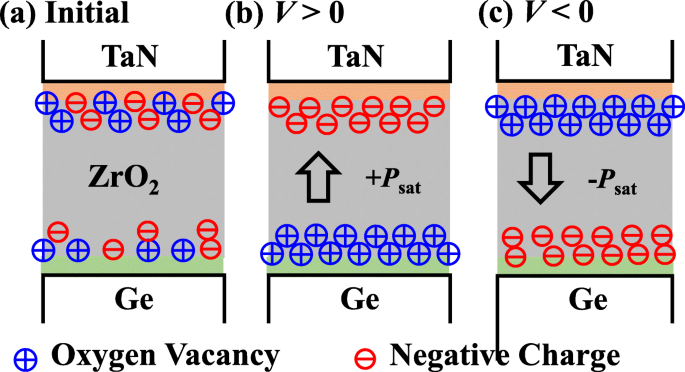

スイッチング P アモルファスZrO 2 で観察されます 静電容量、およびメカニズムは報告されたドープされたポリ-HfO 2 のメカニズムとは異なる必要があると推測されます 強誘電性フィルム。強誘電性挙動の根底にあるメカニズムは、酸素空孔双極子に関連していることを提案します。 TaN金属が堆積すると、Ta脱酸素剤層がZrO 2 内の酸素空孔濃度を増加させることはよく知られています。 [10]。酸素空孔はZrO 2 にも現れます / Geインターフェース。図5に、切り替え可能な P の概略図を示します。 TaN / ZrO 2 で / Geは、正と負の双極子を形成するための酸素空孔と負電荷の移動に起因します。 ZrO 2 の負電荷が推測されます Al 2 と同様のZr空孔[11]に関連しています。 O 3 映画[12]。電圧駆動の酸素空孔の移動は、抵抗変化型メモリデバイスで広く実証されています[13、14]。特に、これは、電圧駆動の酸素空孔が支配的な3端子不揮発性トランジスタの最初のデモンストレーションです。

切り替え可能な P のメカニズムの概略図 ZrO 2 で コンデンサ。これは、電圧駆動の酸素空孔と負電荷が移動して双極子を形成することに起因します

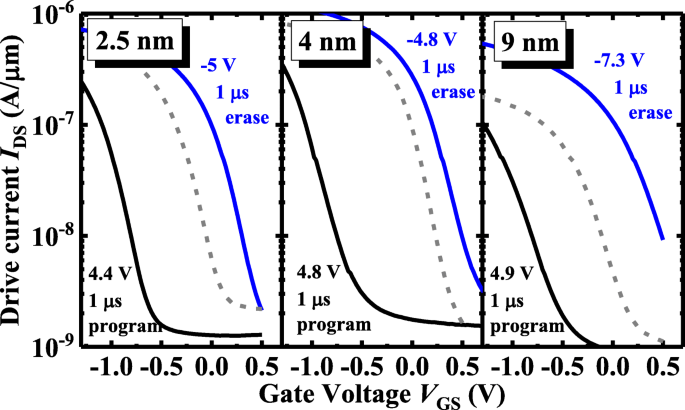

P-V ヒステリシスにより、ZrO 2 が有効になります 組み込みNVM(eNVM)アプリケーション用の大きくて安定したMWを取得するためのFeFET。図6は、測定された I を示しています。 DS - V GS 2.5、4、および9nmのZrO 2 の曲線 1μsのプログラム/消去(P / E)条件での2つの偏光状態のFeFET。トランジスタは500°Cでアニーリングされました。プログラム(消去)動作は、ZrO 2 のゲートに正(負)の電圧パルスを印加することによって実現されます。 FeFET、しきい値電圧( V )を上げる(下げる) TH )。 V TH V として定義されます GS 100 nA・W / Lで、MWは V の最大変化として定義されます。 TH 。さまざまなZrO 2 を備えたすべてのFeFET 厚さは、1μsのP / Eパルスで1Vを超えるMWを持ちます。同様のMWを達成するには、9 nm ZrO 2 に対してより高い消去電圧が必要です。 他の2つのトランジスタと比較したFeFET。より大きなマグニチュードが V を消去することがわかります GS I-V のほぼ等しいシフトを取得するには プログラム V と比較した初期曲線との相対 GS 。 P に寄与する酸素空孔が推測されます 主にTaNとZrO 2 の間の反応から生じます 、図5aのデバイスの初期状態のように。正の V として GS (プログラム)が適用されると、酸素空孔が拡散し、ZrO 2 の近くの層に蓄積します。 / Ge界面(図5b)。酸素空孔双極子の分布は初期状態とはかなり異なります。したがって、 I-V を簡単にシフトできます。 より高い| V へのカーブ TH |正の V GS 。ただし、負の V として GS (消去)が適用されると、酸素空孔の逆拡散により、ゲートスタックが元の状態に戻ります(図5c)。したがって、負の消去の大きさ V GS I-V の同等のシフトを達成するには、増やす必要があります ポジティブプログラム V GS 。

測定された I DS - V GS 2.5、4、および9nmの厚さのZrO 2 の曲線 1μsのP / Eパルスを使用した初期および2つの偏光状態のFeFET

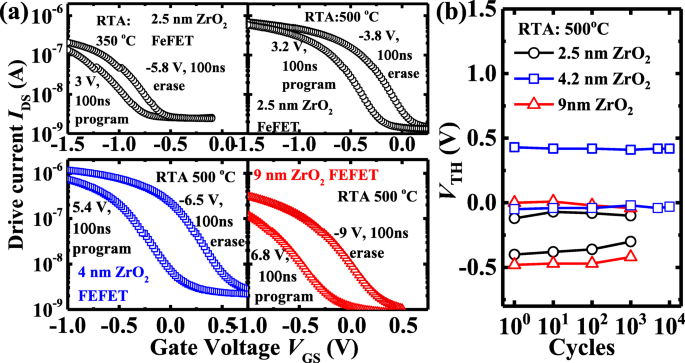

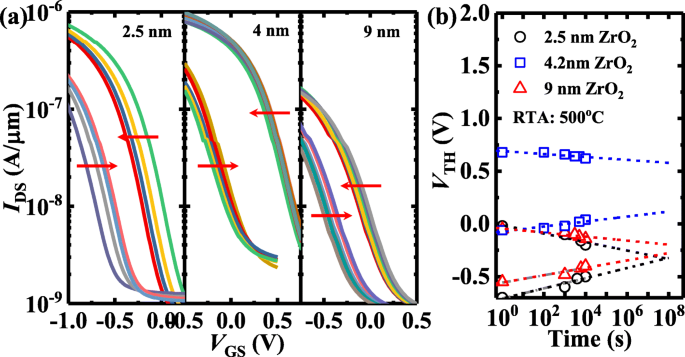

P / Eパルス幅が100nsに減少すると、ZrO 2 図7aに示すように、FeFETは依然として適切なMWを示しています。特に、2.5 nmZrO 2 のトランジスタ 350°Cでアニールすると、0.28 VのMWが達成されます。図7bは、さまざまなZrO 2 を使用したFeFETのMW対サイクル数をプロットしたものです。 100nsのP / Eパルス条件での厚さ。 4 nmZrO 2 デバイスは、2.5nmおよび9nmのZrO 2 と比較して、大幅に改善された耐久性能を実現します。 明らかなウェイクアップ効果と10 3 以内の疲労を示すFeFET サイクル。

a 私 DS - V GS 2.5、4、および9nmの厚さのZrO 2 の曲線 100nsのP / Eパルスによる2つの偏光状態のFeFET。デバイスは500°CでRTAを受けました。 b 4 nmZrO 2 のFeFET 2.5および9nm ZrO 2 と比較して耐久性が向上しています トランジスタ

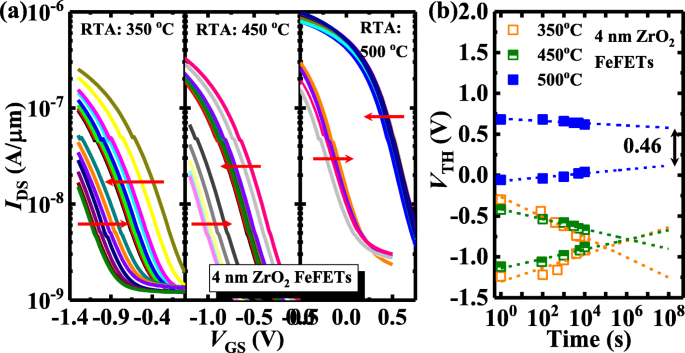

最後に、ZrO 2 の保持テスト FeFETの特性を示し、図1および2に示します。図8aは、 I の進化を示しています。 DS - V GS 4 nmZrO 2 の2つの偏光状態の曲線 FeFETは、350、450、および500°CでRTAを受けました。電荷トラップは、時間の経過とともにデバイスの削減につながります。図8bに示すように、RTA温度を上げると、デバイスの保持性能を向上させることができます。 〜0.46 VのMWは、10年以上維持されると推定されます。図9は、さまざまなZrO 2 を使用したFeFETの保持特性を比較しています。 厚さ。 4 nmZrO 2 デバイスは、2.5および9nmの厚さのZrO 2 を備えたトランジスタと比較して、保持性能が向上しています。 。

a I の進化 DS - V GS 4 nmZrO 2 の2つの偏光状態の曲線 異なるRTA温度のFeFET。 b 4 nmZrO 2 500°Cでアニールされたデバイスは、低温でRTAを備えたトランジスタと比較してはるかに優れた保持性能を備えています

a I の進化 DS - V GS 2.5、4、および9nmの厚さのZrO 2 の2つの偏光状態の曲線 FeFETは500°CでRTAを受けました。 b 4 nmZrO 2 デバイスは、2.5および9nmの厚さのZrO 2 を備えたトランジスタと比較して、保持性能が向上しています。

結論

要約すると、アモルファスZrO 2 強誘電体コンデンサは実験的に実証されており、強誘電性は、酸素空孔と負電荷によって形成される電圧駆動双極子の移動によるものと推測されます。 2.5 nm、4 nm、および9nmのZrO 2 を備えたFeFET 1μsのP / EパルスでMWが1Vを超える。改善された疲労および保持特性は、4nmの厚さのZrO 2 で得られます。 2.5nmおよび9nm ZrO 2 のデバイスと比較したFeFET 。保持テストは、4 nm ZrO 2 トランジスタは、推定された10年の分子量を約0.46Vに保ちます。

データと資料の可用性

この記事の結論を裏付けるデータセットは、記事に含まれています。

略語

- RTA:

-

急速熱アニーリング

- IL:

-

界面層

- TaN:

-

窒化タンタル

- FeFET:

-

強誘電性電界効果トランジスタ

- TDMAZr:

-

テトラキス(ジメチルアミド)ジルコニウム

- Ge:

-

ゲルマニウム

- ZrO 2 :

-

二酸化ジルコニウム

- ALD:

-

原子層堆積

- HF:

-

フッ化水素酸

- BF 2 + :

-

フッ化ホウ素イオン

- MW:

-

メモリウィンドウ

- NVM:

-

不揮発性メモリ

- P r :

-

残留分極

- TEM:

-

透過型電子顕微鏡

- Ni:

-

ニッケル

- P max :

-

最大分極

- RTA:

-

リペイドサーマルアニーリング

- V 範囲 :

-

掃引電圧範囲

ナノマテリアル