CMOSゲート回路

これまで、トランジスタロジック回路の分析は TTL に限定されていました。 設計パラダイム。これにより、バイポーラトランジスタが使用され、フローティング入力の一般的な戦略は「高」(V cc に接続)と同等になります。 )入力(およびそれに対応して、「オープンコレクタ」出力ステージの許容値)は維持されます。ただし、これが論理ゲートを構築できる唯一の方法ではありません。

電界効果トランジスタ

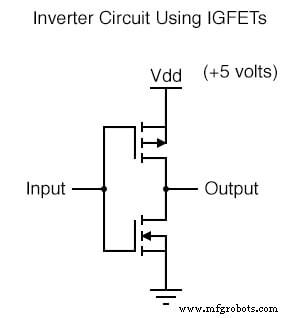

電界効果トランジスタ、特に絶縁ゲートの種類は、ゲート回路の設計に使用できます。 IGFETは、電流制御デバイスではなく電圧制御デバイスであるため、非常に単純な回路設計を可能にする傾向があります。たとえば、PチャネルとNチャネルのIGFETを使用して構築された次のインバータ回路を考えてみましょう。

「V dd 」に注意してください プラス電源端子の「」ラベル。このラベルは、「V cc 」と同じ規則に従います。 TTL回路の「」:これは、グランドを基準にして、電界効果トランジスタのドレインに印加される定電圧を表します。

ゲート回路の電界効果トランジスタ

低入力

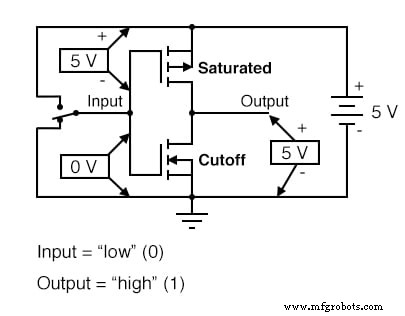

このゲート回路を電源と入力スイッチに接続して、その動作を調べてみましょう。これらのIGFETトランジスタはEタイプ(エンハンスメントモード)であるため、通常オフであることに注意してください。 デバイス。

正しい極性のゲートとドレイン間(実際にはゲートと基板間)に印加された電圧を使用して、それらを バイアスします。 。

上部のトランジスタはPチャネルIGFETです。チャネル(基板)をゲート(基板に対してゲートが負)よりも正にすると、チャネルが拡張され、ソースとドレインの間に電流が流れます。

したがって、上の図では、上部のトランジスタがオンになっています。ゲートと基板(ソース)間の電圧がゼロの下部トランジスタは、通常モードです:オフ 。

したがって、これら2つのトランジスタの動作は、ゲート回路の出力端子がV dd にしっかりと接続されるようになります。 アースへの非常に高い抵抗接続。これにより、入力の「低」(0)状態に対して出力が「高」(1)になります。

高入力

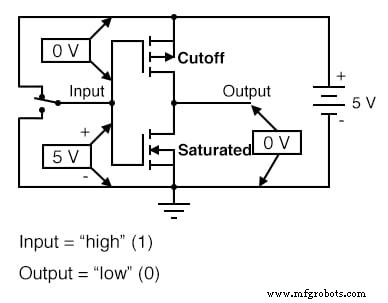

次に、入力スイッチを別の位置に移動して、何が起こるかを確認します。

これで、下側のトランジスタ(Nチャネル)が飽和状態になります。これは、ゲートと基板(チャネル)の間に正しい極性の電圧が印加されてオンになるためです(ゲートでは正、チャネルでは負)。ゲートと基板の間にゼロ電圧が印加されている上部トランジスタは、通常モードです:オフ 。

したがって、このゲート回路の出力は「ロー」(0)になります。明らかに、この回路はインバーター、またはゲートではない動作を示します。

相補型金属酸化物半導体(CMOS)

バイポーラトランジスタの代わりに電界効果トランジスタを使用することで、インバータゲートの設計が大幅に簡素化されました。このゲートの出力は、最も単純なTTL回路の場合のようにフロートしないことに注意してください。これは、負荷電流のソースとシンクの両方が可能な自然な「トーテムポール」構成になっています。

このゲート回路のエレガントなデザインの鍵は、補完的なです。 PチャネルとNチャネルの両方のIGFETの使用。 IGFETはより一般的にMOSFET( M )として知られているため etal- O xide- S 半導体 F ield E 効果 T トランジスタ)、この回路はPチャネルトランジスタとNチャネルトランジスタの両方を一緒に使用します。このようなゲート回路に与えられる一般的な分類は CMOS : C 例示的な M etal O xide S 半導体。

CMOSゲート:課題と解決策

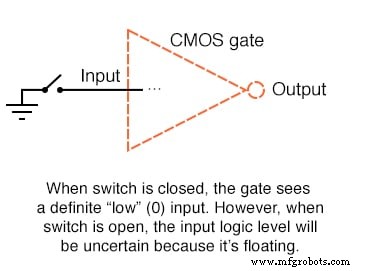

CMOS回路は、電界効果トランジスタに固有の非線形性に悩まされることはありません。デジタル回路として、それらのトランジスタは常に飽和のいずれかで動作するからです。 またはカットオフ モードであり、アクティブではありません モード。ただし、それらの入力は、静電(静電気)源によって生成される高電圧に敏感であり、フローティングのままにすると、スプリアス電圧源によって「高」(1)または「低」(0)状態にアクティブ化されることもあります。

>このため、どのような状況でもCMOS論理ゲート入力をフロートさせることはお勧めできません。これは、フローティング入力が「高」(1)論理レベルとして安全に解釈されたTTLゲートの動作とは大きく異なることに注意してください。

フローティング入力に関するCMOSの問題

これは、CMOS論理ゲートへの入力が単投スイッチによって駆動される場合に問題を引き起こす可能性があります。この場合、1つの状態で入力がいずれかのV dd にしっかりと接続されます。 またはグランドで、他の状態では入力がフローティングになっています(何にも接続されていません):

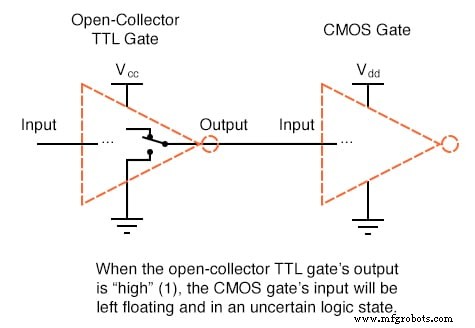

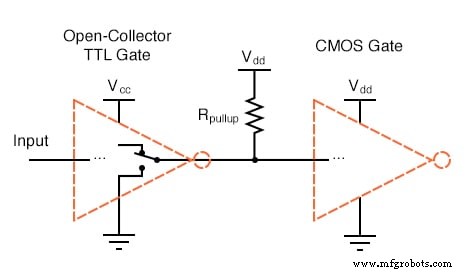

また、この問題は、CMOSゲート入力がオープンコレクターによって駆動されている場合に発生します。 TTLゲート。このようなTTLゲートの出力は「ハイ」になるとフロートするため(1)、CMOSゲート入力は不確実な状態のままになります。

フローティング入力の解決策

プルアップ抵抗

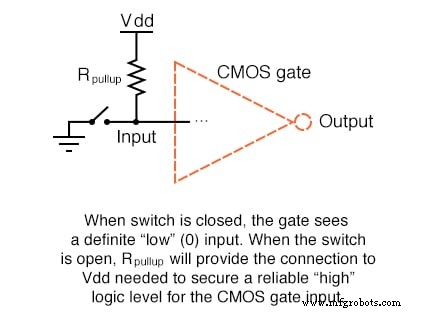

幸い、このジレンマには簡単な解決策があります。これは、CMOSロジック回路で頻繁に使用されるものです。単投スイッチ(または両方が不可能な他の種類のゲート出力)の場合はいつでも ソーシングおよびシンク電流)は、いずれかのV dd に接続された抵抗であるCMOS入力を駆動するために使用されています。 または、グランドを使用して、駆動デバイスの出力がフローティング状態の状態に安定したロジックレベルを提供することができます。

この抵抗の値は重要ではありません。通常、10kΩで十分です。フローティング信号ソースの場合に「ハイ」(1)ロジックレベルを提供するために使用される場合、この抵抗はプルアップ抵抗として知られています。 :

プルダウン抵抗

このような抵抗を使用して、信号ソースがフローティングの場合に「ロー」(0)ロジックレベルを提供する場合、これはプルダウン抵抗と呼ばれます。 。繰り返しますが、プルダウン抵抗の値は重要ではありません:

オープンコレクタTTL出力は常にシンクし、ソース、電流、プルアップはしないため このような出力をCMOSゲート入力に接続する場合は、抵抗が必要です。

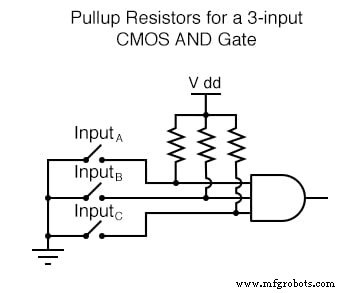

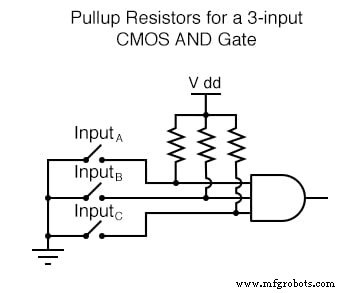

複数のプルダウン抵抗とプルダウン抵抗

前の例で使用されたCMOSゲートはすべてインバーター(単一入力)でしたが、プルアップ抵抗とプルダウン抵抗の同じ原理が複数入力CMOSゲートに適用されます。もちろん、ゲート入力ごとに個別のプルアップ抵抗またはプルダウン抵抗が必要になります。

これにより、次の質問が発生します。AND、NAND、OR、NORなどの複数入力CMOSゲートをどのように設計するのでしょうか。当然のことながら、この質問への回答は、TTL相当のCMOSインバーターと非常によく似た設計の単純さを示しています。

CMOSNANDゲート

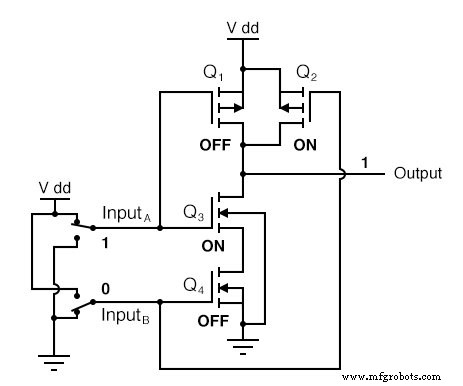

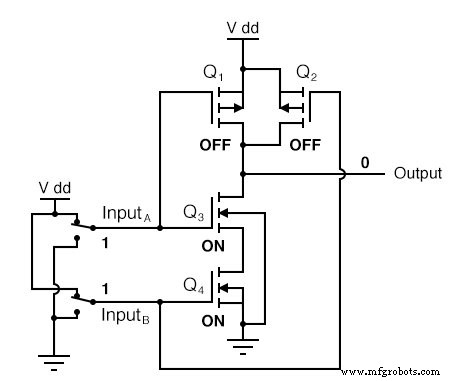

たとえば、CMOSNANDゲートの概略図は次のとおりです。

トランジスタQ 1 およびQ 3 インバータ回路の直列接続された相補ペアに似ています。両方とも同じ入力信号(入力A)によって制御され、入力が「ハイ」のときに上部トランジスタがオフになり、下部トランジスタがオンになります(1)。その逆も同様です。

トランジスタQ 2 にも注目してください。 およびQ 4 同様に、同じ入力信号(入力B)によって制御され、同じ入力ロジックレベルで同じオン/オフ動作を示す方法もあります。両方のペアの上位トランジスタ(Q 1 およびQ 2 )ソース端子とドレイン端子を並列にし、下部トランジスタ(Q 3 およびQ 4 )は直列接続されています。

これが意味するのは、どちらかの場合、出力が「ハイ」(1)になるということです。 上部のトランジスタは飽和し、両方の場合にのみ「ロー」(0)になります 低いトランジスタは飽和します。

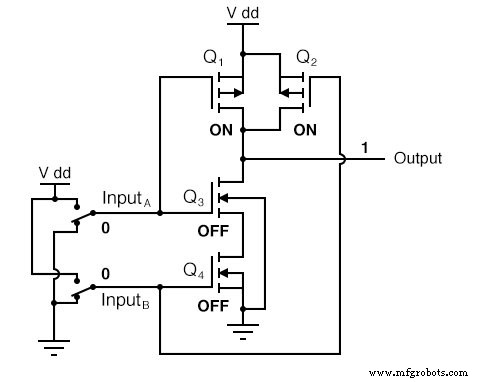

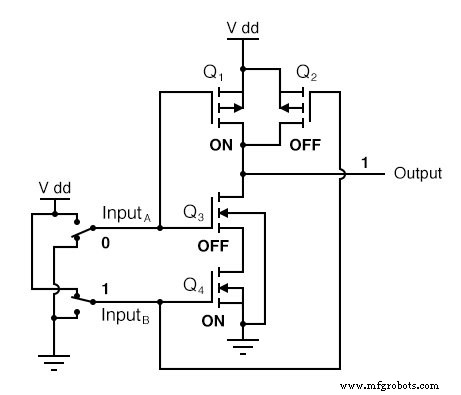

すべてのロジック入力のCMOS回路動作

次の一連の図は、入力論理レベル(00、01、10、および11)の4つの可能性すべてに対するこのNANDゲートの動作を示しています。

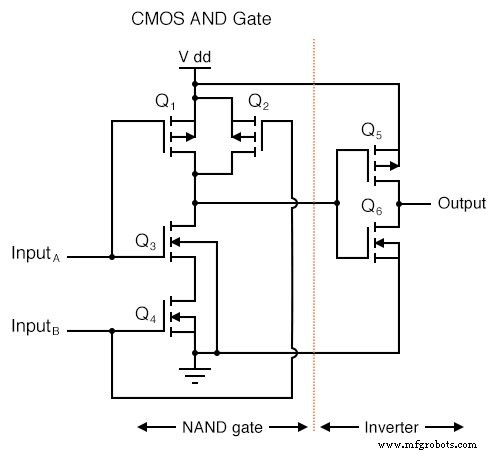

CMOSANDゲート

TTL NANDゲートと同様に、CMOSNANDゲート回路をANDゲートの作成の開始点として使用できます。追加する必要があるのは、出力信号を反転するためのトランジスタの別のステージだけです。

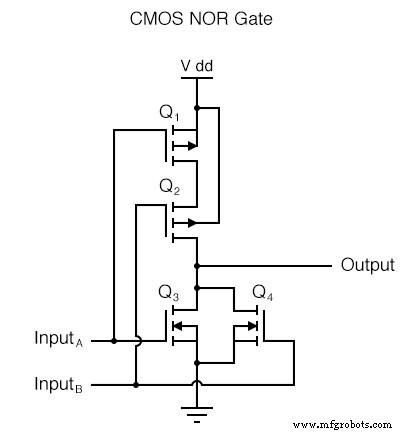

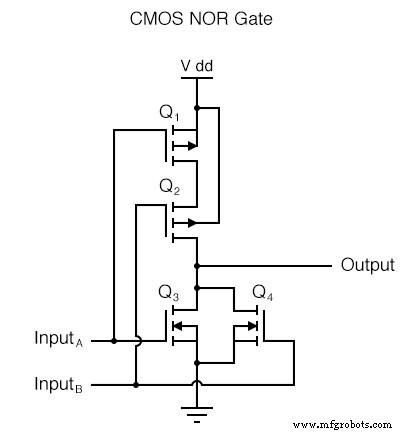

CMOSNORゲート

CMOS NORゲート回路は、トランジスタの配置が異なることを除けば、NANDゲートと同じように4つのMOSFETを使用します。 2つの並列ソーシングの代わりに (上)V dd に接続されたトランジスタ および2つの直列接続されたシンキング (下の)トランジスタがグランドに接続されている場合、NORゲートは次のように2つの直列接続されたソーシングトランジスタと2つの並列接続されたシンクトランジスタを使用します。

NANDゲートと同様に、トランジスタQ 1 およびQ 3 トランジスタQ 2 と同様に、相補ペアとして機能します およびQ 4 。各ペアは、単一の入力信号によって制御されます。 どちらかの場合 入力A または 入力Bは「ハイ」(1)で、下位トランジスタの少なくとも1つ(Q 3 またはQ 4 )が飽和状態になるため、出力が「低」(0)になります。

両方の場合のみ 入力が「ロー」(0)の場合、両方の下部トランジスタがカットオフモードになり、両方の上部トランジスタが飽和状態になり、出力が「ハイ」(1)になるために必要な条件になります。もちろん、この動作はNORロジック関数を定義します。

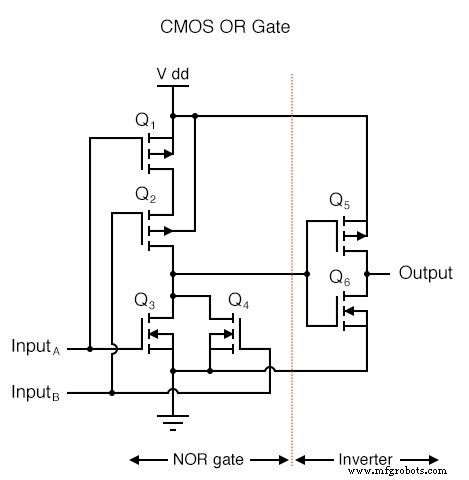

CMOSORゲート

OR機能は、出力にインバータステージを追加して、基本的なNORゲートから構築できます。

TTLとCMOS:長所と短所

TTLテクノロジを使用して構築できるゲートはCMOSで複製できるように見えるので、なぜこれら2つの論理設計の「ファミリ」がまだ共存しているのでしょうか。答えは、TTLとCMOSの両方に独自の利点があるということです。

TTLとCMOSの比較リストの何よりもまず、消費電力の問題です。このパフォーマンスの尺度では、CMOSが無敵の勝利者です。 CMOSゲート回路の相補型PチャネルおよびNチャネルMOSFETペアは、(理想的には)同時に導通することはないため、V dd から回路に流れる電流はほとんどまたはまったくありません。 負荷に電流を供給するために必要な電流を除いて、電源装置。一方、TTLは、それを構成するバイポーラトランジスタのバイアス要件のため、常にいくらかの電流が流れていないと機能できません。

ただし、この利点には注意が必要です。 TTLゲートの消費電力は、その動作状態に関係なく一定のままですが、CMOSゲートは、入力信号の周波数が高くなるにつれて、より多くの電力を消費します。 CMOSゲートが静的な(変化しない)状態で動作している場合、(理想的には)ゼロ電力を消費します。

ただし、CMOSゲート回路は、出力状態が「ロー」から「ハイ」に、またはその逆に切り替わるたびに過渡電流を流します。したがって、CMOSゲートがモードを切り替える頻度が高いほど、V dd から電流が流れることが多くなります。 供給、したがってより高い周波数でより大きな電力損失。

CMOSの利点

また、MOSFETは電流制御ではなく電圧制御のデバイスであるため、CMOSゲートはTTLゲートよりも駆動ゲート出力から引き出される電流がはるかに少なくなります。これは、1つのゲートがTTL入力よりもはるかに多くのCMOS入力を駆動できることを意味します。 1つのゲート出力が駆動できるゲート入力の数の測定は、ファンアウトと呼ばれます。 。

CMOSゲート設計がTTLよりも優れているもう1つの利点は、電源電圧の許容範囲がはるかに広いことです。一方、TTLゲートは電源(V cc )に制限されています )4.75〜5.25ボルトの電圧、CMOSゲートは通常、3〜15ボルトの任意の電圧で動作できます!

電源電圧のこの不一致の背後にある理由は、MOSFETとバイポーラ接合トランジスタのそれぞれのバイアス要件です。 MOSFETは(基板に関して)ゲート電圧によってのみ制御されますが、BJTは電流制御 デバイス。

TTLゲート回路の抵抗は、5ボルトの安定化電源を想定した適切なバイアス電流に対して正確に計算されます。その電源電圧に大きな変動があると、トランジスタのバイアス電流が不正確になり、信頼性の低い(予測できない)動作が発生します。

電源電圧の変動がCMOSゲートに与える唯一の影響は、「高」(1)状態の電圧定義です。 15ボルトの電源電圧(V dd )で動作するCMOSゲートの場合 )、「ハイ」と見なされるには、入力信号が15ボルトに近い必要があります(1)。 「低」(0)信号の電圧しきい値は同じままです:0ボルト近く。

CMOSのデメリット

CMOSの決定的な欠点の1つは、TTLと比較して速度が遅いことです。 CMOSゲートの入力容量は、BJTではなくMOSFETを使用しているため、同等のTTLゲートの入力容量よりもはるかに大きいため、CMOSゲートは信号遷移(低から高)への応答が遅くなります。またはその逆)TTLゲートよりも、他のすべての要素は同じです。

回路抵抗とゲートの入力容量によって形成されるRC時定数は、デジタル論理レベルの高速の立ち上がり時間と立ち下がり時間を妨げる傾向があり、それによって高周波性能が低下します。

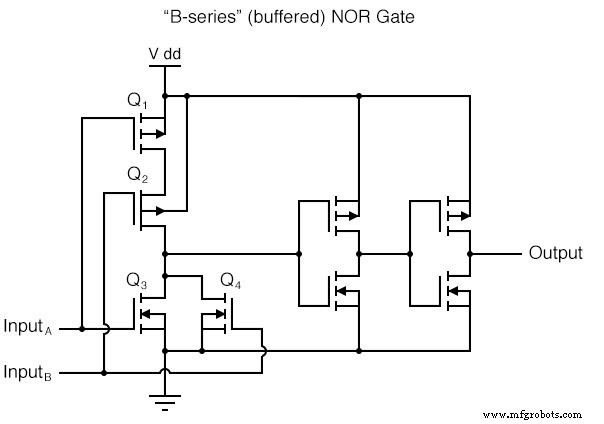

短所と戦うための戦略

CMOSゲート回路のこの固有の欠点を最小限に抑えるための戦略は、出力信号を追加のトランジスタステージで「バッファリング」して、デバイスの全体的な電圧ゲインを上げることです。これにより、ある論理状態から別の論理状態にゆっくりと変化する入力電圧に対して、より高速に遷移する出力電圧(高から低または低から高)が提供されます。

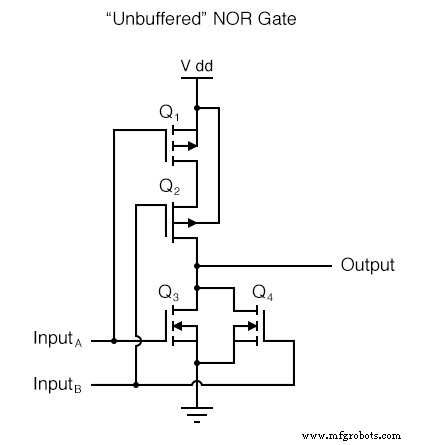

「バッファリングされていない」NORゲートと「バッファリングされた」または Bシリーズのこの例を考えてみましょう。 、NORゲート:

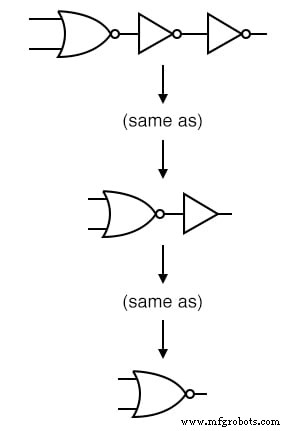

本質的に、Bシリーズの設計強化により、単純なNOR回路の出力に2つのインバーターが追加されます。 2つのカスケードされたインバーターは単にキャンセルするので、これはデジタルロジックに関する限り目的を果たしません:

ただし、これらのインバータステージを回路に追加すると、全体的な電圧ゲインが増加し、出力が入力状態の変化に対してより敏感になり、CMOSゲートの入力容量によって引き起こされる固有の速度低下を克服することができます。

レビュー:

- CMOS論理ゲートは、バイポーラ接合トランジスタではなく、IGFET(MOSFET)トランジスタで構成されています。

- CMOSゲート入力は静電気に敏感です。それらは高電圧によって損傷を受ける可能性があり、フローティングのままにすると任意の論理レベルになる可能性があります。

- プルアップ およびプルダウン 抵抗は、電流のソースまたはシンクのみが可能な信号ソースによって駆動される場合に、CMOSゲート入力がフローティングになるのを防ぐために使用されます。

- CMOSゲートは、同等のTTLゲートよりもはるかに少ない電力を消費しますが、それらの電力損失は信号周波数とともに増加しますが、TTLゲートの電力損失は、広範囲の動作条件にわたってほぼ一定です。

- MOSFETは電流制御ではなく電圧制御のデバイスであるため、CMOSゲート入力はTTL入力よりもはるかに少ない電流を消費します。

- CMOSゲートは、TTLよりもはるかに広い範囲の電源電圧で動作できます。TTLの場合は4.75〜5.25ボルトであるのに対し、通常は3〜15ボルトです。

- CMOSゲートは、MOSFETゲートによって引き起こされる入力容量のために、TTLゲートよりもはるかに低い最大動作周波数を持つ傾向があります。

- Bシリーズ CMOSゲートには「バッファリングされた」出力があり、入力から出力への電圧ゲインを増加させ、入力信号の変化に対する出力応答を高速化します。これは、MOSFETの入力容量とそれによって生じるRC時定数によるCMOSゲートの固有の速度低下を克服するのに役立ちます。

関連するワークシート:

-

絶縁ゲート電界効果トランジスタワークシート

-

CMOS論理ゲートワークシート

産業技術