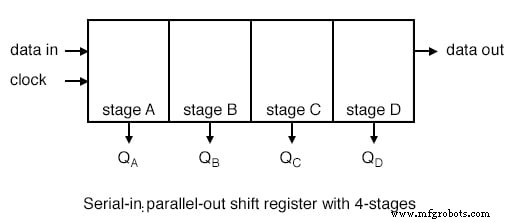

シフトレジスタ:シリアル入力、パラレル出力(SIPO)変換

シリアル入力、パラレル出力のシフトレジスタは、データを内部ストレージ要素にシフトし、シリアル出力、データ出力、ピンでデータをシフトアウトするという点で、シリアル入力、シリアル出力のシフトレジスタに似ています。

これは、すべての内部ステージを出力として使用できるようにするという点で異なります。したがって、シリアル入力、パラレル出力のシフトレジスタは、データをシリアル形式からパラレル形式に変換します。

シリアル入力、パラレル出力のシフトレジスタの使用例

以下のデータ入力時に、4つのデータビットが1本のワイヤを介して4つのクロックパルスでシフトインされると、データは4つの出力Q A で同時に使用可能になります。 Q D へ 4番目のクロックパルスの後。

シリアル入力、パラレル出力のシフトレジスタの実際のアプリケーションは、データを単一のワイヤのシリアル形式から複数のワイヤの並列形式に変換することです。

4つの出力( Q A )で4つのLED(発光ダイオード)を照らしてみましょう Q B Q C Q D 。

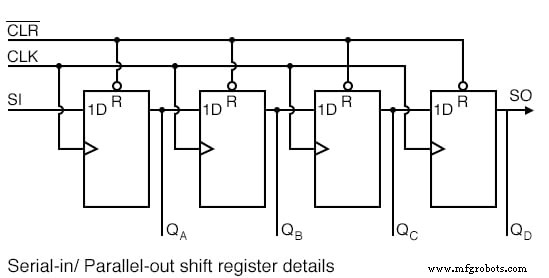

シリアル入力、パラレル出力のシフトレジスタに関する上記の詳細は非常に単純です。これは、各ステージ出力にタップが追加されたシリアル入力、シリアル出力のシフトレジスタのように見えます。

シリアルデータは SI にシフトインします (シリアル入力)。ステージ数に等しいクロック数の後、最初のデータビットがSO(Q D )に表示されます。 )上図。

通常、SOピンはありません。最終段階(Q D 上記)はSOとして機能し、存在する場合は次のパッケージにカスケードされます。

シリアル入力、パラレル出力とシリアル入力、シリアル出力シフトレジスタ

シリアル入力、パラレル出力のシフトレジスタがシリアル入力、シリアル出力のシフトレジスタに非常に似ている場合、なぜメーカーはわざわざ両方のタイプを提供するのですか?

シリアル入力、パラレル出力のシフトレジスタを提供しないのはなぜですか?

答えは、8ビット以下である限り、実際にはシリアル入力、パラレル出力のシフトレジスタのみを提供するということです。

シリアル入力、シリアル出力のシフトレジスタは、18〜64ビットの8ビット長よりも大きいことに注意してください。

多くの出力ピンを必要とする64ビットのシリアル入力、パラレル出力のシフトレジスタを提供することは実用的ではありません。上記のシフトレジスタについては、以下の波形を参照してください。

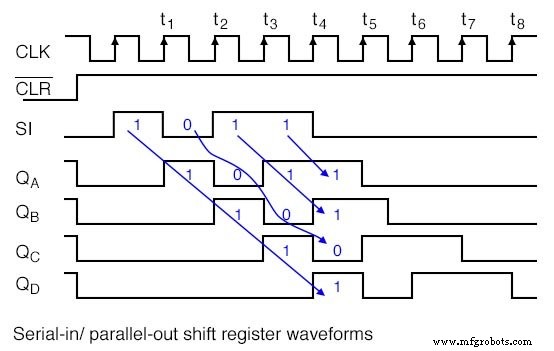

シフトレジスタは、 CLR ’によってデータの前にクリアされています 、アクティブロー信号。シフトレジスタ内のすべてのタイプDフリップフロップをクリアします。

シリアルデータに注意してください 1011 SI で提示されたパターン 入力。このデータはクロック CLK と同期されます 。

これは、別のシフトレジスタのようなもの、たとえば、パラレルイン、シリアルアウトのシフトレジスタ(ここには示されていません)からシフトインされる場合に当てはまります。

t1 の最初の時計 、データ 1 SI D からシフト Q へ 最初のシフトレジスタステージの。 t2 の後 この最初のデータビットは Q B にあります 。

t3 の後 Q C にあります 。 t4 の後 Q D にあります 。 4つのクロックパルスが最初のデータビットを最後のステージまでシフトしました Q D 。

2番目のデータビットは 0 Q C にあります 4番目の時計の後。 3番目のデータビットは 1 Q B にあります 。 4番目のデータは別の 1 Q A にあります 。

したがって、シリアルデータ入力パターン 1011 ( Q D Q C Q B Q A )。 4つの出力で利用できるようになりました。

クロック t 4 の直後から4つの出力で使用可能になります t 5 の直前まで 。

この並列データは、これら2つの時間の間に使用または保存する必要があります。そうしないと、Q D がシフトアウトされるために失われます。 次の時計のステージ t 5 t 8 へ 上記のように。

シリアルイン、パラレルアウトデバイス

Texas Instrumentsの厚意により、集積回路として利用可能なシリアル入力、パラレル出力のシフトレジスタを詳しく見てみましょう。

完全なデバイスデータシートについては、リンクをたどってください。

- SN74ALS164Aシリアル入力/パラレル出力8ビットシフトレジスタ

- SN74AHC594シリアル入力/パラレル出力8ビットシフトレジスタと出力レジスタ

- SN74AHC595シリアル入力/パラレル出力8ビットシフトレジスタと出力レジスタ

- CD4094シリアル入力/パラレル出力8ビットシフトレジスタと出力レジスタ

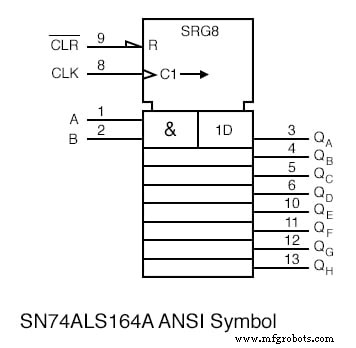

74ALS164Aは、2つのシリアル入力 A を除いて、前の図とほぼ同じです。 および B 。

他の入力を有効にするには、未使用の入力をHighにプルする必要があります。上記のすべての段階を示しているわけではありません。

ただし、すべての出力は、ピン番号とともに、以下のANSI記号に示されています。

CLK 上記のANSIシンボルの制御セクションへの入力には、2つの内部機能 C1 があります。 、プレフィックスが 1 のすべてのものの制御 。

これは、 1D でのデータのクロックインになります 。 2番目の関数であるスラッシュ(/)の後の矢印は、シフトレジスタ内のデータを右(下)にシフトします。

8つの出力は、制御セクションの下の8つのレジスターの右側にあります。 A&B に対応するために、最初のステージは他のステージよりも幅が広くなっています。 入力。

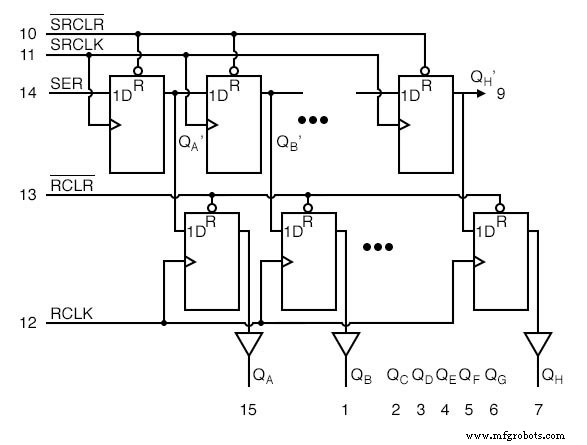

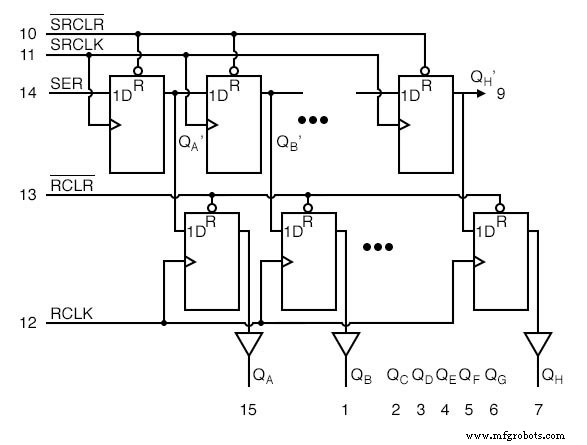

上記の内部論理図は、74AHC594のTI(Texas Instruments)データシートを基にしています。一番上の行のタイプ「D」FFは、シリアル入力、パラレル出力のシフトレジスタで構成されています。

このセクションは、前述のデバイスと同様に機能します。出力( Q A ’Q B ’ Q H へ ’ )デバイスのシフトレジスタの半分は、下半分のタイプ「D」のFFに並列に給電します。 Q H ’ (ピン9)は、オプションのカスケードデバイスパッケージにシフトアウトされます。

RCLKの単一の正のクロックエッジは、 D からデータを転送します Q へ 低いFFの。すべての8ビットは出力レジスタと並列に転送されます (ストレージ要素のコレクション)。

出力レジスタの目的は、新しいデータが上位シフトレジスタセクションにシフトされている間、一定のデータ出力を維持することです。

これは、出力がリレー、バルブ、モーター、ソレノイド、ホーン、またはブザーを駆動する場合に必要です。シフト中のちらつきが問題にならない限り、LEDを駆動する場合はこの機能は必要ない場合があります。

74AHC594には、シフトレジスタ( SRCLK )用に個別のクロックがあることに注意してください。 )および出力レジスタ( RCLK )。また、シフターは SRCLR によってクリアされる場合があります そして、 RCLR による出力レジスタ 。

特にリレーやモーターなどを駆動する場合は、電源投入時に出力を既知の状態にすることが望ましいです。以下の波形は、データのシフトとラッチを示しています。

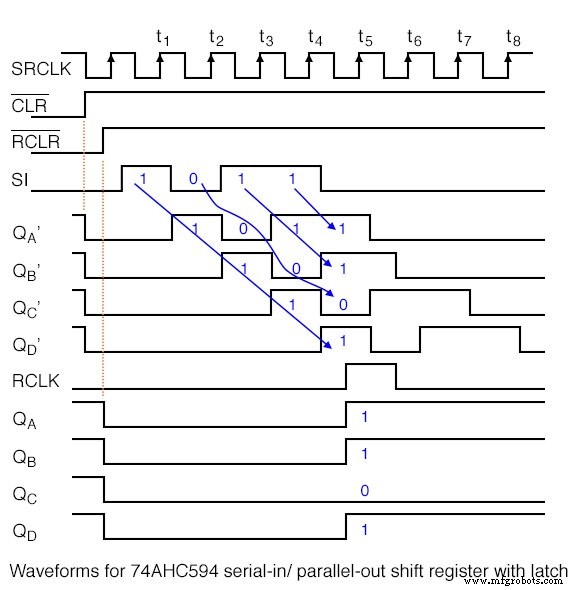

上記の波形は、4ビットのデータが74AHC594の最初の4ステージにシフトされ、次に出力レジスタにパラレル転送されることを示しています。

実際には、74AHC594は8ビットのシフトレジスタであり、8ビットのデータをシフトインするのに8クロックかかります。これは、通常の動作モードです。

ただし、ここで示す4ビットはスペースを節約し、動作を適切に示しています。

t 0 の半クロック前にシフトレジスタをクリアします。 SRCLR ’=0 。 SRCLR ’ シフトする前にハイに戻す必要があります。

t 0 の直前 出力レジスタは RCLR ’=0 によってクリアされます 。それもリリースされます( RCLR ’=1 。

シリアルデータ 1011 クロック間のSIピンに表示されます t 0 および t 4 。クロック t 1 によってシフトインされます t 2 t 3 t 4 内部シフトステージに表示される Q A ’Q B ’Q C ’Q D ’ 。

このデータは、 t 4 の間のこれらの段階に存在します および t 5 。 t 5 の後 目的のデータ( 1011 )これらの内部シフターステージでは使用できなくなります。

t 4 の間 および t 5 ポジティブゴーイング RCLK を適用します データの転送 1011 出力を登録するには Q A Q B Q C Q D 。

このデータは、より多くのデータとしてここで凍結されます( 0 s)後続の SRCLK 中にシフトインします s( t 5 t 8 へ )。別の RCLK が実行されるまで、ここでのデータの変更はありません。 適用されます。

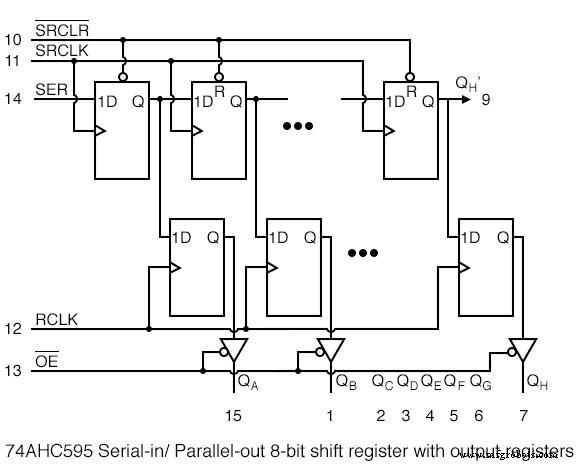

74AHC595は、 RCLR 'を除いて、「594」と同じです。 OE ’に置き換えられます 8つの出力レジスタビットのそれぞれの出力でトライステートバッファを有効にします。

出力レジスタをクリアすることはできませんが、 OE ’=1 によって出力が切断される可能性があります 。

これにより、外部のプルアップまたはプルダウン抵抗により、システムの電源投入時にリレー、ソレノイド、またはバルブドライバーを既知の状態に強制することができます。

システムの電源がオンになり、たとえばマイクロプロセッサがデータをシフトして「595」にラッチすると、出力イネーブルがアサートされる可能性があります( OE ’=0 )有効なデータを使用してリレー、ソレノイド、およびバルブを駆動しますが、それ以前は駆動しません。

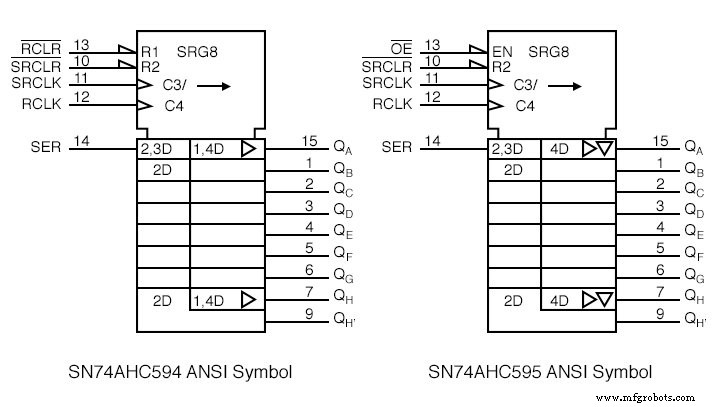

上記は、これらのデバイスに提案されているANSIシンボルです。 C3 データをシリアル入力にクロックインします(外部 SER ) 3 で示されるように 2,3D のプレフィックス 。

C3 / の後の矢印 シフトレジスタの右(下)にシフトすることを示します。コントロールセクションの下の「595シンボル」の左に8段階あります。

2 2,3D のプレフィックス および 2D これらのステージは R2 によってリセットできることを示します (外部の SRCLR ’ 。

1 1,4D のプレフィックス ‘594 R1 (外部の RCLR ’ )シフトレジスタセクションの右側にある出力レジスタをリセットする場合があります。

‘595 、 EN があります 外部の OE ’ 出力レジスタをリセットできません。ただし、 EN トライステート(逆三角形)出力バッファを有効にします。

両方の ‘594 の右向きの三角形 および ‘595 内部バッファリングを示します。両方の ‘594 および ‘595 4 で示されるように、出力レジスタはC4によってクロックされます。 1,4D および 4D それぞれ。

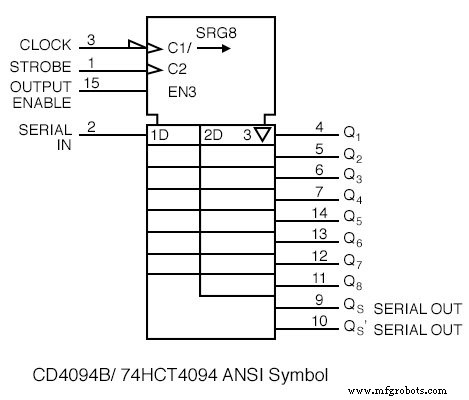

CD4094Bは、3〜15Vの DC 以前の74AHC594デバイスに代わる対応可能なラッチシフトレジスタ。

時計 、 C 1、 SERIAL IN でデータをシフトインします 1 によって暗示されるように 1D のプレフィックス 。

C1 の/(右矢印)で示されるように、これは右シフトシフトレジスタ(シンボル本体の左半分)のクロックでもあります。 /(矢印)時計 入力。

ストロボ 、 C2 シンボル本体の右側にある8ビット出力レジスタのクロックです。 2 2D C2 は出力レジスタのクロックです。

出力ラッチの逆三角形は、出力がトライスタットであり、 EN3 によって有効になっていることを示します。 。

3 逆三角形と 3 の前 EN3 の 有効化( EN )と同様に、省略されることがよくあります。 )トライステート出力を制御すると理解されています。 Q S および Q S ’ シフトレジスタステージの非ラッチ出力です。

Q S SERIAL IN にカスケードできます 後続のデバイスの。

実用的なアプリケーション

シリアル入力、パラレル出力のシフトレジスタの実際のアプリケーションは、マイクロプロセッサからリモートパネルインジケータにデータを出力することです。

または、シリアル形式のデータを受け入れる別のリモート出力デバイス。

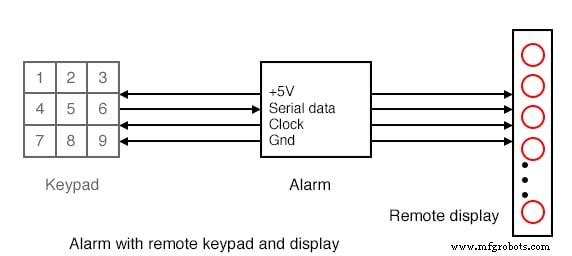

「リモートキーパッド付きアラーム」の図は、リモートディスプレイを追加して、パラレルイン、シリアルアウトのセクションからここに繰り返されています。

したがって、たとえば、メインのアラームボックスに接続されているアラームループのステータスを表示できます。

アラームが開いているウィンドウを検出すると、シリアルデータをリモートディスプレイに送信して通知することができます。

キーパッドとディスプレイの両方が、メインのアラームボックスとは別に、同じリモートエンクロージャー内に含まれている可能性があります。ただし、このセクションでは表示パネルのみを見ていきます。

ディスプレイがアラームと同じボード上にある場合は、電源とアース用の2本のワイヤーに加えて、8本のLEDに8本のワイヤーを配線するだけで済みます。

これらの8本のワイヤは、リモートパネルへの長期的な使用ではあまり望ましくありません。シフトレジスタを使用すると、クロック、シリアルデータ、ストロボ、電源、およびアースの5本のワイヤを実行するだけで済みます。

パネルがメインボードからわずか数インチ離れている場合でも、信頼性を向上させるために、接続ケーブルの配線数を減らすことが望ましい場合があります。

また、マイクロプロセッサで使用可能なピンのほとんどを使い果たし、出力数を増やすためにシリアル技術を使用する必要がある場合もあります。

デジタル-アナログコンバータなどの一部の集積回路出力デバイスには、マイクロプロセッサからデータを受信するためのシリアル入力、パラレル出力のシフトレジスタが含まれています。

ここに示されている手法は、これらのパーツに適用できます。

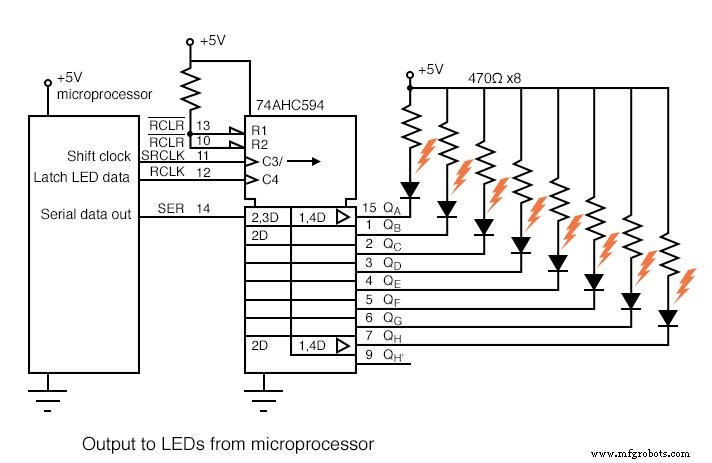

出力レジスタを備えた74AHC594シリアル入力、パラレル出力シフトレジスタを選択しました。ただし、追加のピン RCLK が必要です。 、シフトインされたデータを出力ピンに並列ロードします。

この余分なピンは、データがシフトインしている間に出力が変化するのを防ぎます。これは、LEDにとってはそれほど問題ではありません。ただし、リレー、バルブ、モーターなどを駆動する場合は問題になります。

マイクロプロセッサ内で実行されるコードは、出力される8ビットのデータから始まります。 「シリアルデータ出力」ピンに1ビットが出力され、 SER を駆動します。 リモート74AHC594の。

次に、マイクロプロセッサは「シフトクロック」でローからハイへの遷移を生成し、 SRCLK を駆動します ‘595シフトレジスタの。

この正のクロックは、 SER のデータビットをシフトします 最初のシフトレジスタステージの「D」から「Q」へ。

これは Q A には影響しません シフトレジスタと出力ピンの間に内部8ビット出力レジスタがあるため、この時点でLED( Q A Q H へ 。

最後に、「シフトクロック」はマイクロプロセッサによってローに引き戻されます。これで、1ビットの「595」へのシフトが完了しました。

上記の手順をさらに7回繰り返して、マイクロプロセッサから74AHC594シリアル入力、パラレル出力シフトレジスタへの8ビットのデータのシフトを完了します。

内部の「595シフトレジスタ」内の8ビットのデータを出力に転送するには、マイクロプロセッサが RCLK でローからハイへの遷移を生成する必要があります。 、出力レジスタクロック。

これにより、新しいデータがLEDに適用されます。 RCLK 次の8ビットのデータ転送を見越してLowに引き戻す必要があります。

‘595の出力に存在するデータは、上記の2つの段落のプロセスが新しい8ビットのデータに対して繰り返されるまで残ります。

特に、LEDに影響を与えることなく、新しいデータを ‘595内部シフトレジスタにシフトできます。 LEDは、 RCLK を適用した場合にのみ新しいデータで更新されます。 立ち上がりエッジ。

8つ以上のLEDを駆動する必要がある場合はどうなりますか?別の74AHC594 SER をカスケードするだけです Q H に固定します ’ 既存のシフターの。

SRCLK と並列 および RCLK ピン。マイクロプロセッサは、 RCLK を生成する前に、16クロックで16ビットのデータを転送する必要があります。 両方のデバイスに給電します。

私たちが示すディスクリートLEDインジケーターは、7セグメントLEDである可能性があります。ただし、7セグメント数桁を駆動できるLSI(Large Scale Integration)デバイスがあります。

このデバイスは、マイクロプロセッサからシリアル形式のデータを受け入れ、LEDを多重化することにより、ピンよりも多くのLEDセグメントを駆動します。

関連するワークシート:

- シフトレジスタワークシート

産業技術