高密度 FDR 相互接続スイッチ ボードの設計と実装

現在、高速シリアル伝送を応用した高性能コンピュータ相互接続ネットワークの伝送速度は、初代SDR(Single Data Rate、2.5Gb/s)から第4世代のFDR(Fourteen Data Rate、14Gb/s)へと発展しています。 s)、DDR (ダブル データ レート、5Gb/s)、および QDR (クアッド データ レート、10Gb/s)。インターネットの形成に不可欠な相互接続やスイッチボード、インターフェイスカードを備えた PCB (Printed Circuit Board) の設計は、FDR の高速および高周波分野に参入しました。 FDR 信号の立ち上がり時間が 10ps に大幅に短縮されたため、減衰、クロストーク、反射、電磁干渉など、信号の完全性に関する一連の問題が、機能の実装と信頼性の高い動作の可能性を判断するための重要な機能になりました。 . 複数のポート、複数のチャネル、複数の電力カテゴリ、および高エネルギー消費を含む FDR 相互接続チップの機能に基づいて、スループット レートを向上させるために、複数の相互接続チップを単一の相互接続ボードに統合することが常に必要です。一方、限られたスペースのボードでは、コンポーネントのレイアウトと熱放散、高密度でのルーティング、ボードの背面を横切る長距離伝送、あらゆる種類の信号の完全性など、いくつかの要件を満たす必要があります。一方、PCB 設計期間、PCB 製造技術の制限、コスト管理など、いくつかの要素を考慮する必要があります。したがって、設計の実装とシミュレーションの検証は非常に困難です。この記事では、FDR 相互接続とスイッチ ボードの PCB 設計例に基づいて、あらゆる種類の信号の完全性の問題を解決するために、基板材料の選択、スタック アップ設計、ルーティング規則、および干渉防止設計に関するいくつかの最適化方法を紹介します。 FDR 高速 PCB 設計のプロセス。

減衰特性と基板材料の選択

FDR 高周波信号の場合、信号の完全性に関する問題は伝送ラインの損失です。 FDR 信号が相互接続チャネルに沿って送信端末から受信端末に伝送される場合、高周波の減衰が低周波の減衰よりもはるかに大きいため、受信端末に到達する信号波形に深刻な変形が生じます。変形は、主に 2 つの側面に分類されます。信号の電圧振幅が大幅に減少し、信号の立ち上がりエッジに悪い劣化が発生しています。前者は信号の伝送距離を制限し、後者はコード間の干渉につながります。伝送線路損失 A は、導体損失 Acond の合計と見なすことができます。 および誘電損失 Adiel 式 (1) に示すように:A =Adiel + 条件 .

導体損失とは、信号パスとリターン パスの間の銅導体上の直列抵抗によって生じる損失を指します。高周波の状況では、表皮効果により、周囲の銅導体の表面に電流が流れます。銅導体の等価直列抵抗の増加に伴い、式 (2) に示すように、周波数の平方根に正比例する周波数の増加に伴って導体損失が増加します。  .

.

誘電損失は、基板材料の媒質によって発生する損失を指し、主に材料の属性によって決定され、導体幅などの幾何学的構造とは関係なく、周波数に正比例し、式 (3) で示されます。  .

.

式(2)より、線幅を大きくすることで導体損失を低減することができます。ただし、実際の PCB 設計では、ピン、ボード、信号層の数、およびインピーダンス間の間隔の制限の結果として、導体の幅を無制限に広くすることはできません。 FDR 設計で一般的に適用される導体幅/間隔/幅は、通常 7mil/7mil/7mil または 8mil/10mil/8mil です。導体幅が同じ場合、導体損失は材質に関係なく導体長に正比例します。したがって、全体の伝送損失を減らすには、誘電損失のみを考慮する必要があります。式 (3) に基づくと、誘電損失は散逸率に比例し、小さな散逸率の適用は誘電損失の低減に役立ち、全体的な伝送の損失につながります。

表 1 に、伝送速度が 14Gb/s、導体幅 8mil、インピーダンス 50Ω の場合に、式 (1)、(2)、(3) に従って計算された 3 つの通常の高速基板材料の属性パラメーターと損失値を示します。

| ボード素材のパラメータ | FR4 | Nelco4000-13SI | メグトロン6 |

| [email protected] | 0.02 | 0.008 | 0.004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| Acond @7GHz/インチ | 0.24 | 0.240 | 0.240 |

| Aディール @7GHz/インチ | 0.65 | 0.230 | 0.120 |

| [email protected]/in | 0.89 | 0.470 | 0.360 |

| [email protected]/30in | 27.00 | 14.000 | 11.000 |

| 相対コスト | 1.00 | 3.500 | 8.000 |

伝送速度が 14Gb/s で伝送長が 30 インチの場合、Nelco4000-13SI の全体的な伝送損失は約 14dB であり、一般的な FDR チップが耐えられる電圧スイング減衰は 20dB から25dB。したがって、このタイプの基板材料は、伝送距離が 30 インチ未満の FDR 相互接続スイッチ基板設計に適用できます。ただし、FR4 の全体的な伝送減衰量は約 27dB であり、長距離設計の FDR 設計には FR4 を適用できませんが、伝送距離が短い FDR 相互接続インターフェイス カードでは、コストを削減するために FR4 を選択することができます。全体の伝送減衰量が最も小さいMegtron6はコストが最も高く、FDRへの適用はシステム構築費用の増加につながります。結論として、高周波 PCB では基板材料が基本であり、基板材料の選択が信号の伝送長を決定します。

レイアウトとスタックの設計

PCB 設計では、回路基板の構造とスタックを最初に考慮する必要があります。通常、回路基板のパターンと形状は決定されており、スタック数の決定は、信号周波数、回路基板のピン密度、PCB 製造コスト、製造期間、および信頼性要件によって決まります。 FDR 相互接続スイッチ ボードは高い周波数と密度を持ち、多層ボードの適用は干渉を減らすために必要なステップです。さらに、スタック数の決定が重要です。

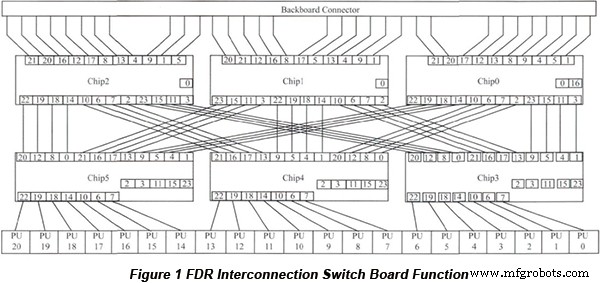

FDR 相互接続チップには 24 個のポートがあり、各ポートは相互結合の操作方法で 8 つの Tx チャネルと 8 つの Rx チャネルを備えています。 6 つの相互接続チップと 3 つのダウンリンク チップが FDR 相互接続ボードによって適用され、バックボード コネクタを介して 32 ポートにアクセスします。 3 つのアップリンク チップは、QSFP (Quad Small Form-factor Pluggable) 光ファイバーを介して 21 ポートにアクセスします。図 1 に示すように、アップリンク チップとダウンリンク チップは 4 つのポートを介して相互に接続されます。

FDR は、面積 50mmx50mm、1157 ピン、間隔 1.0mm の BGA (Ball Grid Array) パッケージを特徴としており、Tx と Rx のポートの P/N ピンは 3 つの同心円に従って配置されています。理論的には、3 つの信号層を適用して、すべてのポートのすべてのピンを BGA から引き出すことができます。次の 2 つの要素を考慮すると、2 つの信号層を使用して、同心円のピンのグループにアクセスできます。

a.間隔の制限により、差動ラインの幅/間隔/幅は 4mil/4mil/4mil であり、BGA からは 8mil/10mil/8mil に拡張され、差動ライン ペア間の距離は少なくとも50ミル。したがって、1 対の差動ラインは 2mm の幅を占有する必要があり、48 対の信号が最大密度のエッジに沿って配置されます。したがって、この方法を実装することは困難です。

b. BGA ピン間の間隔は 1mm です。同心円信号のグループにアクセスするために信号層が適用される場合、BGA の下の差動ライン ペア間の間隔はわずか 14mil であり、必要な 50mil にはほど遠いものです。さらに、並列ルーティングの最大長はわずか 20 mm であり、クロストークが発生します。

上記のマイナス要因を回避するために、2 つの信号層を適用して同心円信号のグループにアクセスし、各信号層の差動信号を 50mil 間隔に従って BGA から引き出す必要があります。したがって、すべての差動信号を BGA から引き出すには、FDR 相互接続ボードで少なくとも 6 層が必要です。基板の接続性と配線量、および交換結合コンデンサ用の十分な基板表面を考慮して、8 つの内部信号と 22 層スタックが適用されます。

クロストークの解析と低減対策

クロストークは、高速および高密度の回路設計に関して最初に考慮する事項です。オフェンシブラインの電圧と電流が変化すると、オフェンスラインとビクティムラインの間に相互容量と相互インダクタンスを介して電磁結合が発生します。ビクティム ラインに沿って送信端子に向かって流れるクロストークは近端クロストークと呼ばれ、ビクティム ラインに沿って受信端子に向かって流れるクロストークは遠端クロストークと呼ばれます。一般的に言えば、ビクティム ラインの全体的なノイズ電圧は、信号電圧の 5% 未満に制御する必要があります。他のノイズ源と犠牲ラインの両側の攻撃ラインを考慮して、シングル エッジの攻撃ラインのクロストーク バジェットを 1% 以内に制御するのが最善です。

クロストークの低減に関する重要なポイントは次のとおりです。

a.

オフェンシブラインとビクティムラインの間隔を広げ、平行配線長を短くする。

b.統合されたグランドは、信号のリターン パスとして適用されます。経験則によると、50Ω のストリップ ラインの場合、間隔がライン幅の 3 倍の場合、近端クロストークは約 0.5% です。 50Ω のマイクロストリップ ラインの場合、間隔がライン幅の 3 倍の場合、近端クロストークは約 1% です。誘導結合の影響が容量結合よりも大きいため、ストリップラインまたは完全に埋め込まれたマイクロストリップラインの遠端クロストークはほぼゼロであり、マイクロストリップ伝送ラインの遠端クロストーク極性は負であり、その大きさは比較的大きい.

• インターバル ルーティング

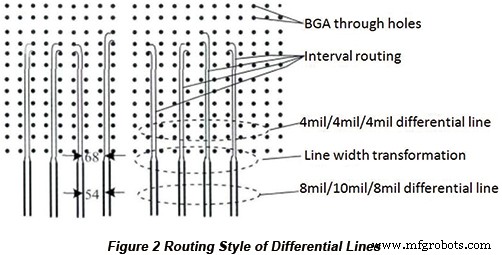

この設計では、高速差動ラインの差動インピーダンスは 100Ω です。 Si9000 フィールド ソルバーに基づいて、線幅/間隔/線幅は 8mil/10mil/8mil と計算されます。線路幅が広いほど減衰量は小さく、10mil の間隔は 100Ω の差動インピーダンスを維持するためです。このタイプの差動ラインは、BGA チップ領域の外側に適用されます。クロストークを減らすために、差動ラインの 2 つのペア間の間隔は 80mil 以上です。 The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

産業技術