PCB EMC 設計で初めての成功を保証する

PCB(プリント回路基板)は、電子製品に適切に実装できるコンポーネントのプラットフォームとして、コンポーネント間の電気的接続として重要な役割を果たし、電子デバイスまたは機器のベースを占めています。そのため、その性能や品質はそのままエレクトロニクス製品に直結します。マイクロエレクトロニクス技術の急速な発展に伴い、多数の電子製品が連携して動作する傾向があり、それらの間の干渉がますます増加しています。さらに、PCB 密度の増加は、PCB 設計の品質が干渉の程度と干渉耐性を決定する上で重要な役割を果たすという事実につながります。その結果、最適な性能を得るために回路が必要な場合、コンポーネントの選択と回路設計だけでなく、優れたコンポーネントのレイアウトと配線も PCB EMC (電磁両立性) 設計に貢献します。

EMC とは、周囲のデバイスまたはシステムに許容できない電磁干渉を生成することを拒否しながら、電磁環境で正常に動作できるデバイスまたはシステムの機能を指します。電磁干渉は、主に非常に高い動作周波数または許容できないレイアウトまたはルーティングに要約される複数の理由により形成されます。避けることのできない高い無線周波数 (RF) の背景の下で、設計者は、EMC を考慮して PCB 設計を実装する際に、コンポーネントのレイアウト、配線、電源および接地の設計に焦点を当てる必要があります。さらに、レイヤー数が異なる PCB の場合、最適なパフォーマンスを実現するには、さまざまな設計要素を考慮する必要があります。

干渉源

• 差動モード電流とコモンモード電流

を。ディファレンシャルモード伝送とコモンモード伝送

どの回路にもコモンモード (CM) 電流とディファレンシャルモード (DM) 電流が含まれています。どちらも RF 送信の範囲を決定します。実際のところ、それらの間には巨大な絶滅が存在します。いくつかのリードまたはトレースとリファレンス リターン ソースが与えられると、いずれかのタイプの電流が利用可能になります。一般的に言えば、DM 信号はデータまたは有用な情報を運びます。しかしコモンモードは、DM 電流の悪影響として EMC に最も問題を引き起こします。 DM伝送は通常、ラインからラインへの伝送として定義され、CM伝送は通常、ラインからグランドへの伝送として定義されます。閉ループによって生成される最大電界強度は、次の式で計算できます  . E は最大電界強度 (μV/m) を指します。 r は、閉ループと測定アンテナの間の距離 (m) を指します。 f は周波数 (MHz) を表します。私はです 電流(mA)を指します。 A はループの面積 (cm²) を指します。

. E は最大電界強度 (μV/m) を指します。 r は、閉ループと測定アンテナの間の距離 (m) を指します。 f は周波数 (MHz) を表します。私はです 電流(mA)を指します。 A はループの面積 (cm²) を指します。

上記の式に基づいて、電界強度がループ面積に正比例することが明確に示されています。 DM 送信レベル (TL) を下げるには、ソース電流の削減とは別に、ループ領域を縮小する必要があります。

電圧降下による CM 放射により、部分接地電圧が基準接地電圧よりも高くなります。有力な接地系統に接続されたケーブルは、CM 放射の構成要素であるアンテナと見なされます。遠方界成分は式で表すことができます  、K は透過係数を指します。 I は CM 電流 (A) を指します。 l はケーブルの長さ (m) を表します。 f は伝送周波数 (MHz) を指します。 r は距離 (m) を表します。

、K は透過係数を指します。 I は CM 電流 (A) を指します。 l はケーブルの長さ (m) を表します。 f は伝送周波数 (MHz) を指します。 r は距離 (m) を表します。

この式は、電界強度がケーブル長に正比例することを明確に示しています。 CM 伝送の減少は、CM 電流の減少とケーブル長の短縮に依存します。

b. CMとDMの変換

DM と CM は、インピーダンスの異なる 2 つの信号線が利用できる場合、相互に変換できます。インピーダンスは主に、物理トレースと相関するリードまたは櫛形のコンデンサとインダクタによって決定されます。大多数の PCB のトレースでは、CM と DM の発生を回避できるように、寄生容量と寄生インダクタンスを最小限に抑える必要があります。したがって、環境に敏感な回路は、各導体のリードまたは櫛形の容量が寄生容量と同等になるように、特定の方法でバランスを取る必要があります。

c. CM と DM の干渉を停止する一般的な方法

CM および DM 電流と RF 干渉を停止するための基本的なガイドラインは、電流容量のオフセットまたは電流容量の最小化にあります。トレースに電流が流れると磁力線が発生し、電界が発生します。どちらのフィールドも RF エネルギーを放射できます。磁力線が相殺されるか、最小限に抑えられると、RF エネルギーが存在しなくなり、最終的に干渉が停止します。準拠できる特定の措置または規則については、この記事の後半で説明します。

•クロストーク

PCB 設計の重要な要素として、プロセス全体の各リンクでクロストークを慎重に考慮する必要があります。クロストークとは、電磁干渉の影響を受けやすいトレース、リード、ケーブル束、コンポーネント、またはその他の電子コンポーネント間の不要な電磁結合を指します。

主要な EMI (電磁干渉) 伝送アプローチとして、クロストークはトレース間の干渉を引き起こす傾向があります。クロストークは、容量結合とインダクタンス結合に分類できます。前者は通常、トレースが他のトレースまたは基準面の上に配置されているという事実に由来します。後者は通常、互いに物理的に近似しているトレースから派生します。平行トレースに関しては、クロストークには前方と後方の 2 つのモードがあります。 PCB の場合、後方クロストークは前方クロストークよりも検討する価値があります。回路では、電源と干渉するトレースの間のインピーダンスが大きいほど、クロストーク レベルが高くなります。インダクタンス クロストークは、トレースと伝送線路またはリードの間に端から端までの距離を追加するか、またはトレースと基準面の間の距離を最小限に抑えることで制御できます。

• デジタル信号スペクトル分析

を。デジタル信号

デジタル信号の属性は方形波であり、方形波信号は基本波と多数の高調波サインから構成されています。フーリエ変換を適用して、デジタル信号の周波数範囲の波形をキャプチャできます。したがって、パルス繰り返し周期が短いほど、繰り返し周波数が高くなり、高調波周波数も高くなります。理論的には、方形波の立ち上がり時間はゼロであるため、高調波成分は無限大です。ただし、立ち上がりエッジと立ち下がりエッジの両方を持つ台形波形です。

b.パルスの時間領域と周波数領域の変換 (フーリエ変換)

フーリエ変換により、矩形パルスがコサイン波またはサイン波に分解され、次の式に従います  .この式では、ADn 各コサイン波形の振幅を指します。 n は高調波の数を示します。 w は角周波数を表します。

.この式では、ADn 各コサイン波形の振幅を指します。 n は高調波の数を示します。 w は角周波数を表します。

• デカップリングと接地

を。デカップリング設計

インダクタとコンデンサで構成されるローパス フィルタは、高周波干渉信号をフィルタリングすることができます。ライン上の寄生インダクタンスは電源を減速させ、駆動デバイスの出力電流を低下させます。デカップリング コンデンサを適切に配置し、インダクタとコンデンサのエネルギー貯蔵機能を適用することで、オンとオフの瞬間にデバイスに電流を供給することができます。 DC ループでは、負荷変動によって電源ノイズが発生します。デカップリングコンデンサ構成により、負荷変動によるノイズの発生を抑えることができます。

b.接地設計

電子機器にとって、接地は干渉を制御するための重要な方法です。接地がシールド対策と正しく組み合わされている場合、ほとんどの干渉の問題は解決されます。

• コンポーネントのレイアウトとルーティング

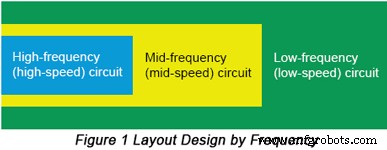

回路レイアウトは、電磁干渉の程度と干渉抵抗の強さを直接決定します。適切なレイアウトは、回路効率を高めるだけでなく、システム全体の EMC も改善します。単位回路の動作周波数が高くなればなるほど高速になり、信号スペクトルも多様化します。したがって、高周波成分の割合が高いほど、干渉が強くなります。周波数の観点からは、まず高周波回路、次に中周波回路、最後に低周波回路です。ただし、ロジック速度の観点からは、最初に高速回路、次に中速回路、最後に低速回路が続きます。その理論に従って、回路レイアウトは次の設計に従って実装する必要があります。

頻度や速度による分類とは別に、機能や種類も分類基準として使用できます。取るべき詳細な対策については、この記事の残りの部分ですぐに説明します。読み続けると、それらの詳細が得られます。

EMC の PCB 設計規則

回路の EMC 性能への損傷を要求する干渉源が掘り出されたので、EMC 懸念に対応する設計規則は、それらの源にケータリングするために作成されるべきです。 EMC の成功を達成するための PCB 設計ルールは次のとおりです。

• 表面レイアウト

を。 PCB サイズを考慮する必要があります。非常に大きなサイズの基板になると、インピーダンスが高くなり、耐ノイズ性が低下し、製造コストが上昇するため、トレースを長くする必要があります。サイズが非常に小さい基板になると、放熱に支障をきたしたり、隣接するトレース間でクロストークが発生しやすくなります。推奨される PCB サイズは、長さと幅の比率が 3:2 または 4:3 の長方形です。また、基板サイズが 200mm×150mm を超える場合は、基板の機械的強度を考慮する必要があります。したがって、PCB メーカーの基板寸法の制限を知っておくことが非常に重要です。たとえば、PCBCart は最小 6*6mm、最大 600*700mm の回路基板を印刷できます。詳細については、カスタム PCB 製造機能を確認してください。

b.コンポーネントのレイアウト設計では、パーティショニングを慎重に検討する必要があります。デジタル回路、アナログ回路、ノイズ源は基板上に独立して配置し、高周波回路は低周波回路から分離する必要があります。また、信号の強弱による成分分布や信号の伝達方向にも注意が必要です。

c.レイアウトは、各機能回路のコア コンポーネントを中心にして、コンポーネントが同じ方向に沿ってトリムおよびコンパクトに配置されるようにする必要があります。信号間のカップリングが形成されないようにするために、干渉の影響を受けやすいコンポーネントは隣接して配置しないでください。

d.センシティブな信号コンポーネントはパワー デバイスやハイ パワー デバイスから遠ざける必要があり、センシティブな信号ラインがハイ パワー デバイスを通過することは絶対に許されません。温度に敏感なコンポーネントは熱デバイスから離れた場所に配置し、温度に敏感なコンポーネントは温度が最も低い領域に配置する必要があります。

e.短絡の可能性を回避するために、電位差の大きいコンポーネント間の距離を大きくする必要があります。さらに、高出力コンポーネントは、テストで手が触れない場所に配置し、絶縁保護を通過するようにする必要があります。

f.スルー ホールは 0.5pF の分布容量をもたらすため、スルー ホールの削減は動作速度の向上に有益です。

• コンポーネントのレイアウト

を。ディスクリート コンポーネントと比較して、IC コンポーネントは、優れたパッケージング、少ないはんだ接合部、低い故障率などの利点により、優先的に選択する必要があります。さらに、信号によって生成される高周波部分を減らすことができるように、信号の傾きが比較的遅いデバイスを選択する必要があります。表面実装デバイスを適用すると、インピーダンスが減少し、EMC が改善され、トレース長が短縮されます。

b.コンポーネントは、同じ分類に基づいて配置する必要があります。互換性のないコンポーネントは個別に配置して、コンポーネントが空間で互いに干渉しないようにする必要があります。

c.重量が 15g を超えるコンポーネントは、サポートによって固定されるまではんだ付けを行ってはなりません。大きくて重く、多くの熱を発生するコンポーネントは、船上で組み立てるべきではありません。代わりに、完成した箱の底板に組み立てる必要があります。さらに、放熱を保証する必要があり、熱に敏感なコンポーネントは熱を発生するコンポーネントから遠ざける必要があります。

d.ポテンショメータ、調整可能なインダクタンスコイル、可変コンデンサ、マイクロスイッチなどの調整可能なコンポーネントに関しては、システム全体の構造要件を考慮する必要があります。これらのコンポーネントは、内側の調整が必要な場合は回路基板上に配置し、外側の調整が必要な場合はマシン ボードと互換性のある場所に配置する必要があります。

• ルーティング設計

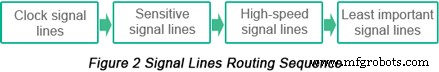

一般的なルーティング ルールは、次の順序に従います:

その一般的なルーティング ルールとは別に、無視してはならない詳細もあります。

を。放射干渉を最小限に抑えるために、多層 PCB は、内層を電源プレーンとグランド プレーンに定義してピックアップする必要があります。これにより、電源回路のインピーダンスを低減し、信号ライン用のグランド プレーンを生成してパブリック インピーダンス ノイズを抑えることができます。信号線と接地面間の分布容量を改善し、放射を止める重要な役割を果たします。多層 PCB の設計上の注意事項は、以下の PCB 層と EMC 設計のセクションに示されています。

b.電源ライン、接地ライン、および回路基板上のトレースによって、高周波信号に対して低インピーダンスを維持する必要があります。周波数が非常に高く保たれると、電力線、接地線、および回路基板のトレースはすべて、干渉の送受信の原因となる小さなアンテナになります。このような干渉を打ち負かすには、フィルタ コンデンサを追加するよりも、電源ライン、接地ライン、および回路基板のトレースが持つ高周波インピーダンスを減らすことが重要です。したがって、回路基板上のトレースは短く太く、均一に配置する必要があります。

c.

d. 電力線、接地線、プリント トレースは、信号線とリターン線によって形成されるループ エリアを最小限に抑えるために、短くてまっすぐになるように適切に配置する必要があります。

d.クロック ジェネレータはクロック デバイスのできるだけ近くに配置する必要があります。

e.

f.水晶振動子のシェルはグランドに接続する。

g. クロック ドメインは接地線で囲み、クロック線はできるだけ短くする必要があります。

g.

h.高周波信号の伝送と結合を減らすために、回路基板には90°の代わりに45°の角度の破線を適用する必要があります.

h. 1 層 PCB と 2 層 PCB には、電源との 1 点接続とグランドとの 1 点接続を適用する必要があります。

電源線も接地線もできるだけ太くする。

i.

j. I/O駆動回路は、回路基板の端にあるコネクタの近くに配置する必要がある。

j.キー ラインは太くする必要があり、両側に保護グランドを追加する必要があります。

k. 高速回線は短く、直線的であること。コンポーネントのピンはできるだけ短くする必要があります。これは、ピンのないマウント コンデンサを利用するデカップリング コンデンサに特に有効です。

l. A/D部品に関しては、デジタル部とアナログ部のアース線を交差させてはならない。

m.クロック、バス、およびチップ セレクト信号は、I/O ラインおよびコネクタから遠ざける必要があります。

いいえ。アナログ電圧入力ライン、基準電圧端子はデジタル回路の信号ライン、特にクロックから離す。

o.クロック ラインが I/O ラインに平行な場合よりも、I/O ラインに垂直な場合の方が干渉は小さくなります。また、クロック コンポーネントのピンは、I/O ケーブルから遠ざける必要があります。

p.

q.水晶振動子やノイズに敏感なデバイスの下にはトレースを配置しないでください。

微弱信号回路や低周波回路周辺ではカレントループを発生させてはならない。

r.信号によってループが生成されないようにする必要があります。ループを配置する必要がある場合は、できるだけ小さくする必要があります。

•トレースルーティング

を。

b.磁気干渉を避けるため、同じ出力で逆方向の電流信号を並列に配置する。プリントリードの不連続は極力少なくする必要があります。例えば

c.リードの角が90°を超えてリード幅が急激に変化してはならない。 EMI はクロック信号ラインで最も発生する傾向があり、クロック信号ラインはルーティングの過程で接地ループに近づける必要があります。

d.バスの運転手は、運転するバスの隣にいる必要があります。 PCBから離れた配線に関しては、ドライバをコネクタの隣に配置する必要があります。

e.通常、クロック リード、行ドライバー、またはバス ドライバーの信号ラインには大きな過渡電流が流れるため、プリント リードはできるだけ短くする必要があります。ディスクリート コンポーネントの場合、印刷されたリード幅は約 1.5mm に達することがあります。ただし、ICの場合、プリントリードの幅は0.2mmから1.0mmの間でなければならない.

f.大面積の銅箔は、サーマルデバイスや大電流が流れるリードの周囲に使用しないでください。製品が熱環境に長時間放置されると、銅箔の膨張や落下などの問題が発生する可能性があります。

g. 大面積の銅箔を使用する必要がある場合は、グリッドを利用することをお勧めします。これは、銅箔と基板の間の熱接着によって発生するガスの放出を排除するのに役立ちます。

g.パッド中央のビア開口部は、コンポーネント ピンの開口部よりも適切に大きくする必要があります。パッドが大きすぎると、ドライはんだが発生する傾向があります。

• 電源設計

不適切な電源設計は、大きなノイズの発生につながり、最終的に製品の性能を低下させます。電源が不安定になる主な要因は 2 つあります。

#1:高速スイッチングの状態では、過渡的な交換電流が大きすぎます。

#2:電流の戻りにインダクタンスが存在します。

その結果、PCB 設計では電源の完全性を十分に考慮する必要がありますが、それとは別に、次の規則も順守する必要があります。

を。電源デカップリング フィルタリング設計

IC チップ電源の 2 つの端子に 0.01μF ~ 0.1μF の静電容量を持つデカップリング コンデンサをブリッジすると、ボード全体のノイズとサージ電流を劇的に減らすことができます。電流補償が満たされている場合、デカップリング キャパシタンスは低いほど良いです。リード インダクタンスが低いため、マウント コンデンサを最適に使用する必要があります。

電力をフィルタリングする最も効果的な方法は、AC 電源ワイヤにフィルタを配置することです。リードの相互結合やループの発生を防ぐため、フィルタの入出力ラインは基板の両側から出し、リードはできるだけ短くしてください。

b.電源保護設計

電源保護設計は、過電流保護、不足電圧アラーム、ソフトスタート、過電圧保護をカバーしています。過電流保護は、ヒューズを適用することにより、PCB の電源セクションで実現できます。溶断の過程でヒューズが他のモジュールに影響を与えるのを防ぐために、入力電圧も静電容量を維持するように設計する必要があります。過電圧による偶発的なコンポーネントの損傷を防ぐには、配電線と接地電位の間に放電管やバリスタなどの保護デバイスを介して等電位を確立し、過電圧保護を実現する必要があります。

• グランドデザイン

電位基点と同電位の機器の場合、アース線は不定電位です。メーターを使用して接地線上のポイント間の電位を測定すると、比較的大きな差異が観察される場合があり、回路が動作しているときに最終的にエラーが発生します.

アース線による EMI の主な原因は、アース線のインピーダンスにあります。アース線に電流が流れると電圧が発生しますが、これがアースノイズです。このような電圧の駆動下では、グランド ワイヤにループ電流が発生し、その後、グランド ループ干渉が発生します。 2 つの回路が共通して同じアース線を使用する場合、公衆インピーダンス結合が発生します。

グランド ループ干渉のソリューションには、グランド ループの切断、グランド ループのインピーダンスの追加、および平衡回路の適用が含まれます。公共のインピーダンス結合を無効にする方法は、公共の接地線または並列一点接地のインピーダンスを減らすことです。アース線設計に関する具体的なルールは次のようになります。

を。デジタルグランドとアナロググランドの分離

回路基板上でアナログ回路とリニア回路の両方が利用できる場合、それらは互いに絶縁されている必要があります。低周波回路は、一点並列接地にもっと依存する必要があります。実際のルーティング プロセスで問題が発生した場合は、並列接地の前に部分的に直列接地を行うことができます。高周波回路は多点直列アースに依存する傾向があり、アース線は短く太くする必要があります。高周波部品の周辺には格子状の銅箔を大量に塗布する必要があります。

b.アース線はできるだけ太くする

耐ノイズ性を高めるために、基板の許容電流の 2 倍の電流が流れるように、接地線はできるだけ太くします。アース線を作るために銅の流し込みが適用される場合、死んだ銅は避けるべきです。また、同様の機能を持つ銅同士を太いリード線で接続することで、ノイズを抑えながらアース線の品質を確保することができます。

c.アース線によって形成される閉ループ回路

デジタル回路のみを含む回路基板の場合、接地回路を円形ループに設計することにより、耐ノイズ能力を高めることができます。

PCB 層と EMC 設計

• 適切な PCB レイヤー数

層数に関しては、単層 PCB、二層 PCB、多層 PCB です。

を。単層 PCB と 2 層 PCB は、中/低密度配線または低信頼性回路に適用できます。製造コストの懸念に基づいて、ほとんどの家電製品は単層 PCB または 2 層 PCB に依存しています。それにもかかわらず、どちらも構造の欠陥の結果として多くの EMI を生成し、外部干渉にも敏感です。

b.多層 PCB は、高密度ルーティングおよび高信頼性チップ回路に適用される傾向があります。したがって、高密度に配置された電子部品で信号周波数が高い場合は、少なくとも 4 層 PCB を選択する必要があります。多層 PCB 設計では、電源プレーンとグランド プレーンを特別に配置し、信号ラインとグランド ラインの間の距離を短くする必要があります。その結果、全信号のループ面積を大幅に削減することができます。 EMC の観点から見ると、多層 PCB は放射を効果的に低減し、干渉防止機能を向上させることができます。

• 単層 PCB 設計

単層 PCB は通常、数百 KHz の低周波数で動作します。高周波の多くの設計条件は、RF 回路リターンの欠如や、完全な閉鎖、明らかなラインスキン効果、または避けられない磁気とループ アンテナの問題。したがって、単層 PCB は、静電気、高速パルス、放射線、または伝導 RF などの RF 干渉に敏感になる傾向があります。単層 PCB 設計では、シグナル インテグリティと端子マッチングは考慮されません。まず、電源とアース線の設計、次にアース線の隣に配置する必要があるリスクの高い信号設計です。近いほど良い。最後に他のラインのデザインです。具体的な設計手段は次のとおりです。

a.

b. 電源線とアース線は、主要な回路信号ネットワークの電源ボックスの接地点に沿うようにする必要があります。

b.トレースはサブ機能に従ってルーティングする必要があり、設計要件は、敏感なコンポーネントと対応する I/O 端子およびコネクタで厳密に検討する必要があります。

c.

d.重要な信号ネットワークのすべてのコンポーネントを隣接して配置する必要があります。

プリント基板で複数の接地点が必要な場合は、それらの接地点が相互に接続されていることを確認し、接続方法の設計を含める。

e.他のライン ルーティングでは、RF 耐性の容量が大きいラインは、RF リターン パスをクリアしたミニ パスの設計方法を使用する必要があります。

• 2 層 / 多層 PCB 設計

を。主要な電源プレーンは、結合容量が発生する対応するグランド プレーンに隣接して配置する必要があります。重要な電源プレーンは、PCB デカップリング コンデンサと連携して、優れたフィルタリング効果を得て、電源プレーンのインピーダンス低減に役立ちます。

b.隣接するプレーンの主要な信号は、信号ループの拡大を停止し、強い放射を減らし、干渉感度を下げるために、分割ゾーンを通過することはできません。

c.クロック信号、高周波信号、高速信号などの重要な信号には、隣接するグランド プレーンが必要です。たとえば、グランド プレーンに隣接する信号プレーンは、信号のルーティングに最適なプレーンと見なすことができるため、信号ループ領域とシールド放射を縮小できます。

d. 20H ルールに適合するため、通常、電源プレーンはグランド プレーンより小さくする必要があります。

PCB の EMC 設計は、技術、知識、および経験の複雑さに由来します。この記事にリストされているすべての設計規則は、エンジニアが EMC 設計で最初の成功を収めるための基本的かつ概念的なガイドラインを提供することを目的としています。実際のところ、優れた EMC 設計では、エンジニアは基板設計を考慮してできるだけ多くの要素を考慮する必要があり、エンジニアはそれらが何であるか、およびそれらにどのように反応するかを知っている必要があります。

役立つリソース:

• EMI および EMC 自動化ツールの最も包括的な紹介

• 電子製品の EMC 性能の PCB レイアウトの影響

• EMC 改善のための PCB 分割設計ルール

• PCB 設計

• ラップトップ PCB の EMC を保証する 3 つの設計上の考慮事項

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1個からスタート

産業技術