負の静電容量デバイスおよび不揮発性メモリアプリケーション用のナノ結晶埋め込み型絶縁体(NEI)強誘電体FET

要約

低電圧ロジックと不揮発性メモリ( NVM)アプリケーション。斜方晶系ZrO 2 を含むNEI層の強誘電性 アモルファスAl 2 に埋め込まれたナノ結晶 O 3 分極電圧測定、ピエゾ応答力顕微鏡、および電気測定によって証明されます。 NEI負容量FET(NCFET)の温度依存性能と耐久性挙動を調査します。 3.6nmの厚さのFE / DEを備えたFeFETは、1 Vを超えるメモリウィンドウを実現し、FEの厚さを最終的にスケーリングして、フィンピッチが非常に小さい3次元FeFETを実現するための道を開きます。

背景

強誘電体ゲート絶縁体層(FeFET)を備えた電界効果トランジスタは、さまざまな集積回路アプリケーションでかなりの関心を集めています。 FeFETは、その固有の負の容量(NC)特性により、従来のMOSFETよりも急峻なスイッチング動作を実現でき、低電圧動作を可能にします[1]。さまざまなチャネル構造[2、3、4]および材料[5、6、7]は、サブ60 mV / decadeサブスレッショルドスイング(SS)を取得しています。また、電流-電圧のヒステリシス( I - V )残留分極による特性( P r )は、不揮発性メモリ(NVM)アプリケーションに使用できます[8]。 FeFETの材料開発は、最近、多結晶ドープHfO 2 に焦点を合わせています。 厚みのスケーラビリティが優れているため[9]、CMOSプロセスの互換性があります[2]。ただし、HfO 2 には依然として基本的な制限があります。 不要なゲートリーク電流を回避するための厚さスケーリング。これにより、FinFETが制限されます[2]。ナノクリスタルMOSとメモリデバイスの概念[10、11]に着想を得て、強誘電体(FE)ナノクリスタルが埋め込まれた絶縁誘電体(DE)層がこの作業で紹介されています。結果として得られた図1に示す新しいデバイス設計は、「ナノ結晶埋め込み絶縁体」(NEI)FeFETと呼ばれます。この設計の主な利点は、ゲートリークが少ない要件を満たす、より薄いユニファイドFE / DE層です。

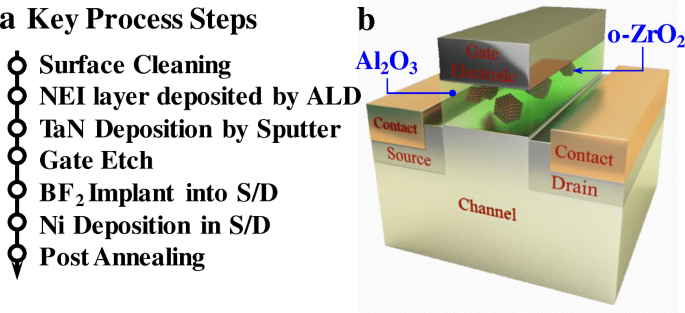

a NEI強誘電性電界効果トランジスタを製造するための主要なプロセスステップ。 b 製造されたNEIFeFETの3D概略図

この作業では、NEIFeFETが報告されます。異なる物理的厚さのNEI層の物理的特性と強誘電性が特徴づけられます。 NEIFeFETの電気的性能を低電圧ロジックおよびNVMアプリケーションについて調査します。

メソッド

NEIFeFET製造の主要なプロセスステップを図1aに示します。抵抗率が0.088〜0.14Ωcmの4インチn型Ge(001)ウェーハを出発基板として使用しました。希釈HFを使用したプレゲート洗浄後、Ge(001)ウェーハを原子層堆積(ALD)チャンバーにロードし、ZrO 2 を含むNEI層を堆積させました。 アモルファスAl 2 に埋め込まれたナノ結晶 O 3 マトリックス。この作業では、さまざまな厚さのNEI層を使用しました。 TaN金属ゲートは、反応性スパッタリングを使用してNEIFeFETに堆積されました。ゲートのパターニングとエッチングの後、BF 2 + イオンは、20keVのエネルギーと1×15cm -2 の線量でソース/ドレイン領域に注入されました。 。 30ナノメートルのニッケル(Ni)は、リフトオフプロセスを使用してソース/ドレイン領域に堆積されました。最後に、デバイスの製造はラピッドサーマルアニーリング(RTA)で完了しました。純粋な誘電体Al 2 を使用して金属酸化物半導体電界効果トランジスタ(MOSFET)を制御します。 O 3 ゲート絶縁層も作製しました。

図1bは、アモルファスDEゲート絶縁層に埋め込まれたFEナノ結晶を含む製造されたNEIFeFETの3D概略図を示しています。 FE材料の量は少ないですが、NCFETおよびNVMアプリケーションには十分です。絶縁性のDE材料は、低いゲートリークと低い動作電圧を実現するための鍵です。大きなバンドギャップエネルギーと高い誘電率(κ)の両方を備えている必要があります )。また、高強圧場( E )を提供する必要があります c )埋め込まれたFEナノ結晶の。

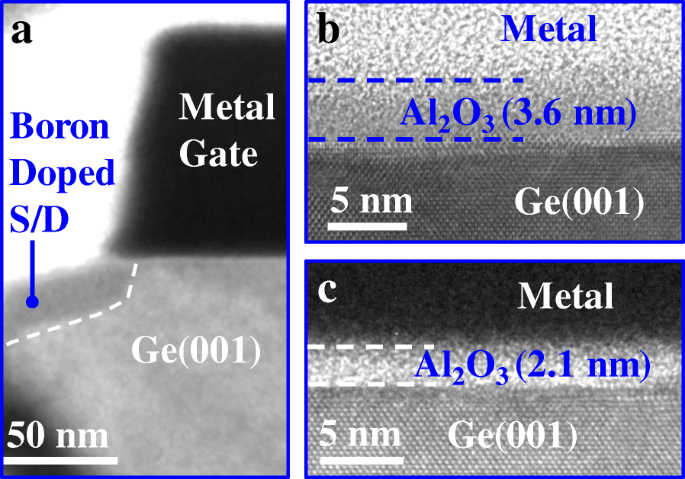

図2aの断面透過型電子顕微鏡(XTEM)画像は、製造されたFeFETのソース/ドレイン、チャネル、およびゲートエッジ領域を示しています。図2bとcは、この研究で研究されたNEI層の厚さがそれぞれ3.6nmと2.1nmであることを示しています。 GeO x の界面層に注意してください NEI層とGeの間に存在しますが、見えません。

a NEI-FeFETのゲート、チャネル、およびソース/ドレイン領域を示すXTEM画像。 b および c それぞれ3.6nmと2.1nmの厚さのNEI層を備えたFeFETのゲートスタックのXTEM画像

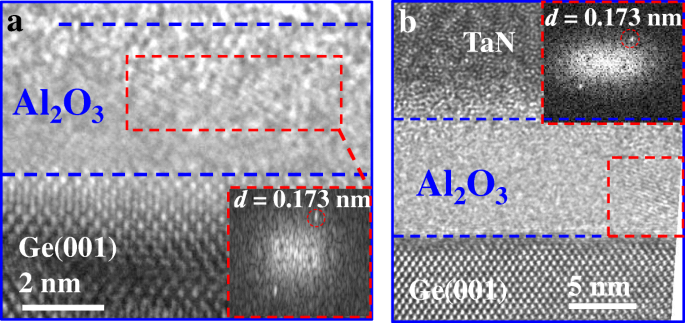

図3の高分解能TEM(HRTEM)画像は、ZrO 2 を示しています。 アモルファスAl 2 に埋め込まれたナノ結晶 O 3 3.6および6nmの厚さのNEIサンプルのGe(001)上。以前の研究では、NEI層のZrの原子百分率が0.5%未満であることを示しました[12]。回折パターンに基づいて、平面間の間隔 d ナノ結晶内は0.173nmと計算され、これは(111)配向の斜方晶ZrO 2 に対応します。 フェーズ[13]。

アモルファスAl 2 に埋め込まれたナノ結晶を示すHRTEM画像 O 3 厚さが a のサンプルの場合 3.6nmおよび b 6nm。挿入図は、平面間の間隔 d を示しています ナノ結晶の0.173nmは、o-ZrO 2 に対応します。 (111)フェーズ

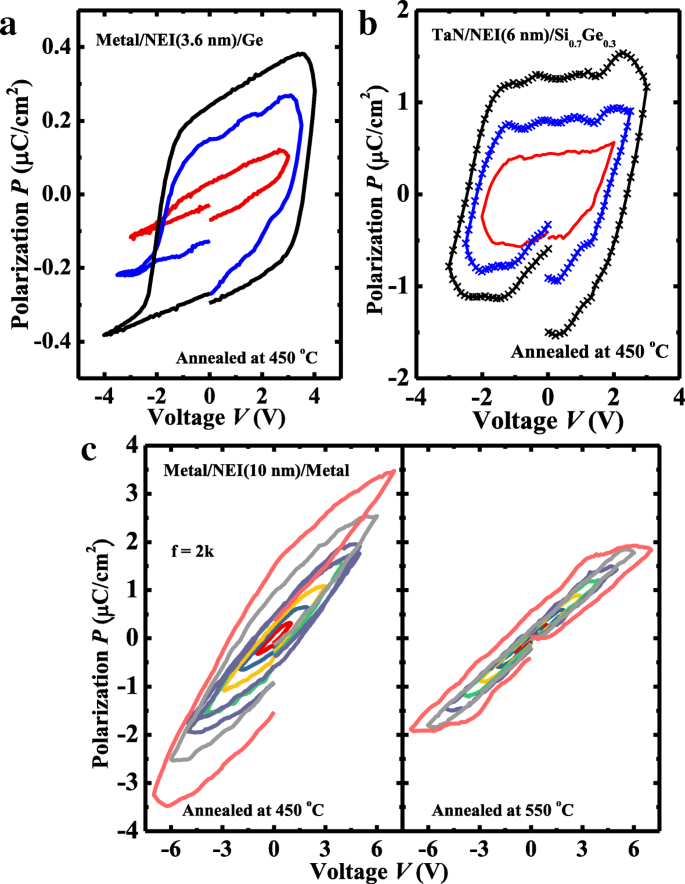

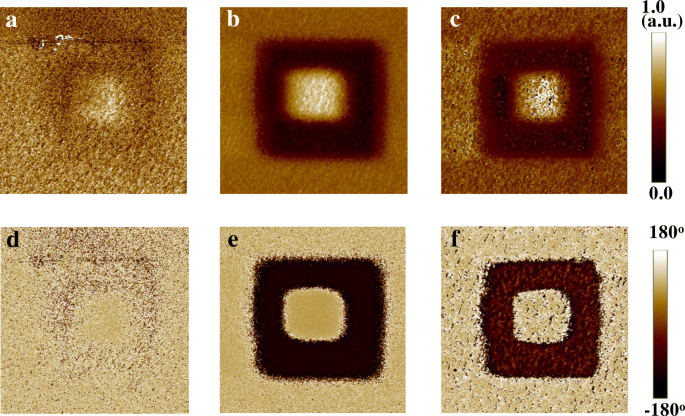

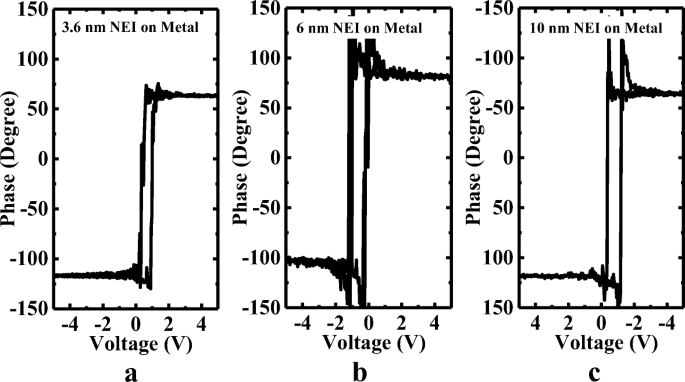

分極対電圧( P - V )およびピエゾ応答力顕微鏡(PFM)測定は、さまざまな厚さのNEIサンプルで実行されました。 NEI層の強誘電性を特徴づけるために、 P - V TaN / NEI(3.6 nm)/ Ge、TaN / NEI(6 nm)/ Si 0.7 の曲線 Ge 0.3 、およびTaN / NEI(10 nm)/ TaNコンデンサをそれぞれ図4a、b、およびcに示します。 NEI層はより低い P を示します HfZrO 2 の報告値よりも (HZO)[14]、これはZrO 2 の体積比が原因です。 Al 2 のナノ結晶 O 3 マトリックスはかなり低いです。残留分極 P r NEIフィルムの割合は、フィルムの厚さが増すにつれて増加します。 P-V 図4cの曲線は、アニーリング温度が450から550°Cに上昇する間にNEI層の強誘電性が低下することを示しています。閉じられていない P-V の理由に注意してください。 ループは、リークが実際に存在するためです。電圧掃引範囲が減少するにつれて、ゼロ電界での結果として生じるオフセットが減少することが報告された[3、15、16]。図5a、b、およびcにそれぞれ示すように、3.6 nm、6 nm、および10 nmのNEIの振幅(上)および位相(下)の画像が測定されました。図6に示すように、TaNのNEIの表面に書かれた反対の極性を示すパターンは、膜厚の増加とより明確なコントラストを示します。

a – c 測定された P - V TaN / NEI(3.6 nm)/ Ge、TaN / NEI(6 nm)/ Si 0.7 の曲線 Ge 0.3 、およびTaN / NEI(10 nm)/ TaN、それぞれ

a – c TaNでの3.6、6、および10 nm NEIのPFM測定の振幅(上)および位相(下)画像

a – c TaNでそれぞれ3.6、6、および10 nmNEIの相変化特性。 NEI層の表面に反対の極性を書き込むことができることが観察されています

結果と考察

NEI NCFET

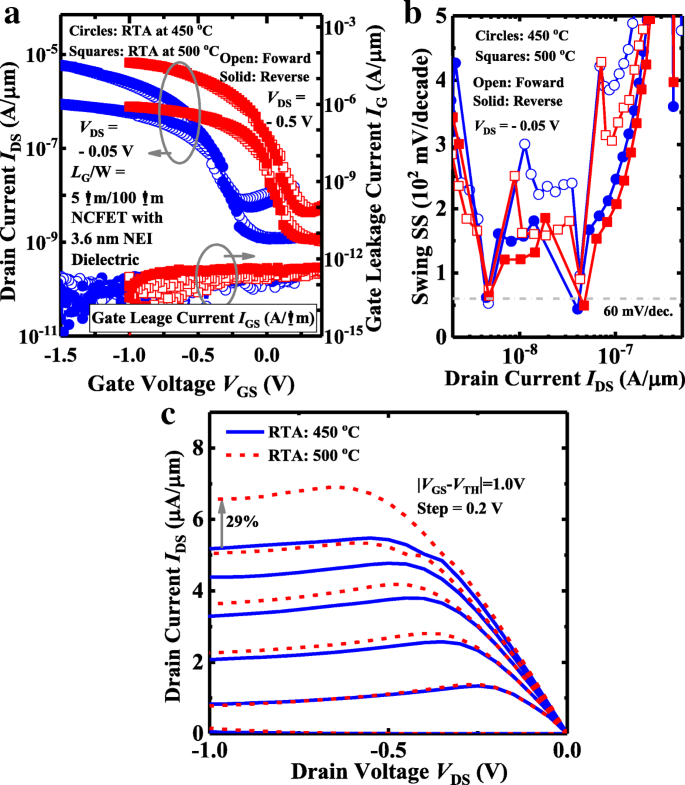

図7aは、測定された I を示しています。 DS - V GS 450°Cおよび500°CでアニールされたNEIの厚さが3.6nmのNEINCFETの曲線。 NCFETはほとんどヒステリシスを示さず、トランジスタの強誘電体容量とMOS容量が良好に一致していることを示しています。 NCFETは、時計回りに誘発されたNC効果を示します I-V ループ。これは、電荷トラップ/デトラップによる反時計回りのループとは対照的です[17]。ゲートリーク I G V の関数として GS 同じペアのデバイスの例は、Al 2 でのナノ結晶の形成を示しています。 O 3 ゲートリークは増加しません。図7bは、NCFETが順方向および逆方向のスイープで60 mV / decade未満の急勾配のSSポイントを達成することを示しています。 NEI NCFETのSS変動は、NC FinFET [2、18]でも観察され、さまざまな強誘電体ナノ結晶またはドメインによる分極スイッチングが原因である可能性があります。測定された I DS - V DS 図7cの同じデバイスのペアの曲線は、∣ V で GS − V TH ∣ =∣ V DS ∣ =1.0V、500°CでRTAを備えたNCFETは、29%大きい I を達成します DS 450°Cでアニールされたトランジスタと比較して。これは、チャネル内のキャリア移動度と接触抵抗特性が、アニーリング温度の上昇とともに改善される可能性があるという事実に起因します[19]。強誘電体層によって引き起こされる典型的な特性である負性微分抵抗(NDR)は、 I で観察されます。 DS - V DS さまざまな温度でアニールされたNCFETの曲線。

a 測定された I DS - V GS および私 G - V GS 450°Cおよび500°Cでアニールされた3.6nmNEIのNCFETの曲線。 b NEI NCFETには、 V に対してサブ60mV / decadeポイントがあります。 DS −0.05Vの値。 c 私 DS - V DS 明らかなNDR現象を示すNEINCFETの曲線。 500°CでアニールされたNCトランジスタは29%の I を達成します DS 1.0Vの供給電圧で450°CのRTAを備えたデバイスと比較して改善

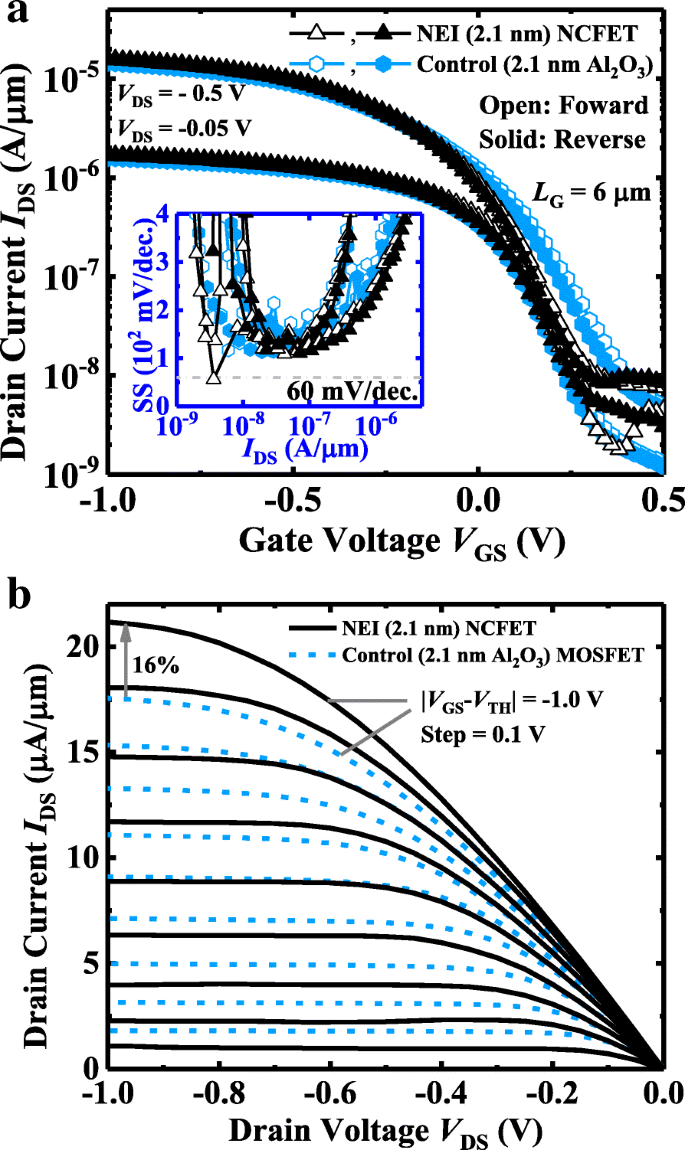

図8aは、測定された I を示しています。 DS - V GS NEINCFETと同じ絶縁体の厚さが2.1nmの制御MOSFETの曲線。デバイスには L があります G 6μmの。 NCFETはヒステリシスのない特性を示します。挿入図は、ポイントSSと I を示しています。 DS デバイスの曲線は、しきい値電圧まで、制御デバイスと比較して改善されたSSがNCFETで達成されることを示しています。図8bは、 I を示しています。 DS - V DS NEINCFETと制御MOSFETの曲線。 NCFETは、低い V に対してNDR現象を示します GS 。 NDR効果は、図8aに示すように、制御MOSFETと比較してNCFETの改善されたドレイン誘導障壁低下(DIBL)特性に対応します。 ∣ V で GS − V TH ∣ =∣ V DS ∣ =1.0 V、16% I DS 制御装置と比較してNCFETで強化が得られます。 2.1 nm NEIのNCFETは、3.6 nm NEIのトランジスタと比較してNDRの重要性が低く、[20]の結論と一致しています。

a 私 DS - V GS NEINCFETと純粋なAl 2 を使用した制御MOSFETの曲線 O 3 誘電。どちらのデバイスにも2.1nmのゲート絶縁体があります。挿入図は、NCFETのSSが制御デバイスよりもしきい値電圧まで急勾配であることを示しています。 b 測定された I DS - V DS NCFETと制御MOSFETの曲線。 NDRは、非常に低い V でNCFETに対して観察されます。 GS 。 ∣ V で GS − V TH ∣ =∣ V DS ∣ =1.0 V、NCFETは16%の I を達成します DS 制御装置と比較して改善

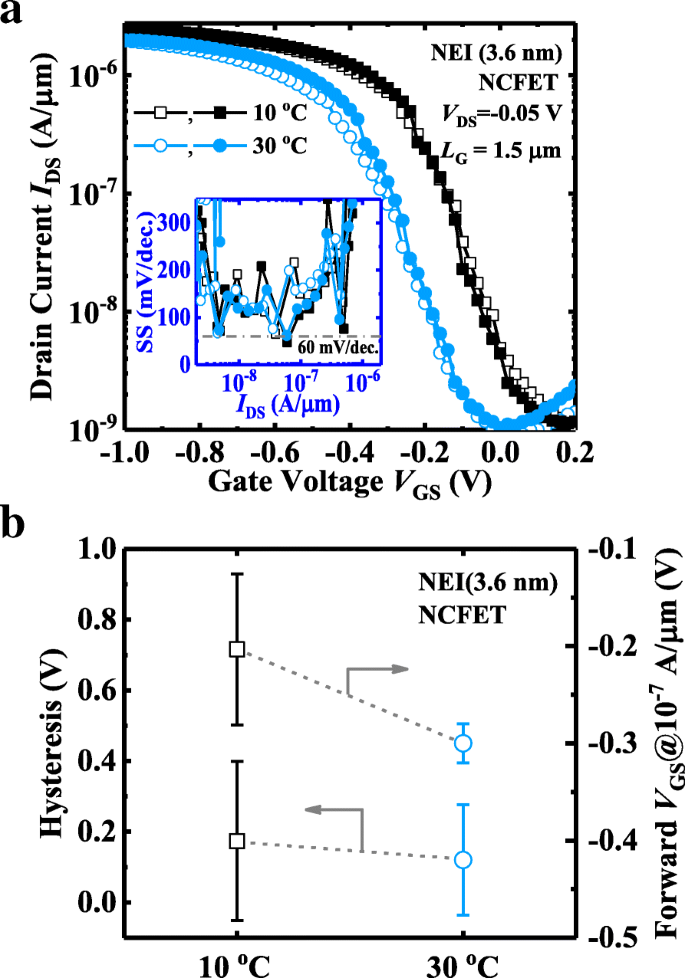

ここでは、厚さ3.6nmのNEIを備えたNCFETの温度依存性を調査します。図9aは I を示しています DS - V GS 10°Cおよび30°Cで測定された曲線。挿入図は、トランジスタのSS性能が高温で低下しないことを示しています。温度が上がると、 I - V 曲線がより負の V にシフトします GS 従来のMOSFETの傾向とは逆の強誘電性の支配的な効果によるものです。図9bは、温度によるヒステリシス電圧と順方向スイッチングしきい値電圧のシフトをまとめたものです。転送 V GS 温度が上昇すると、より負の値にシフトします。これは、 E の増加が原因である可能性があります。 c NEIの。

a 私 DS - V GS 10°Cおよび30°Cで測定されたNEI(3.6 nm)NCFETの特性。予想通り、曲線は温度の上昇とともにより負の電圧へのシフトを示しています。挿入図は急なポイントSSを示しています。 b ヒステリシス(左)と前方 V の統計プロット GS @ 10 −7 3.6 nmNEI層を備えたNCFETのA /μm(右)。転送 V GS 温度の上昇とともに負の方向にシフトします

不揮発性メモリアプリケーション用のNEIFeFET

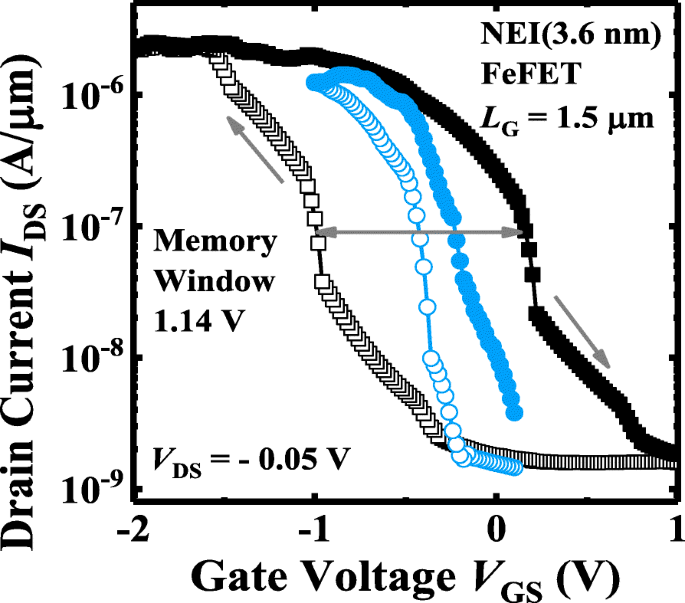

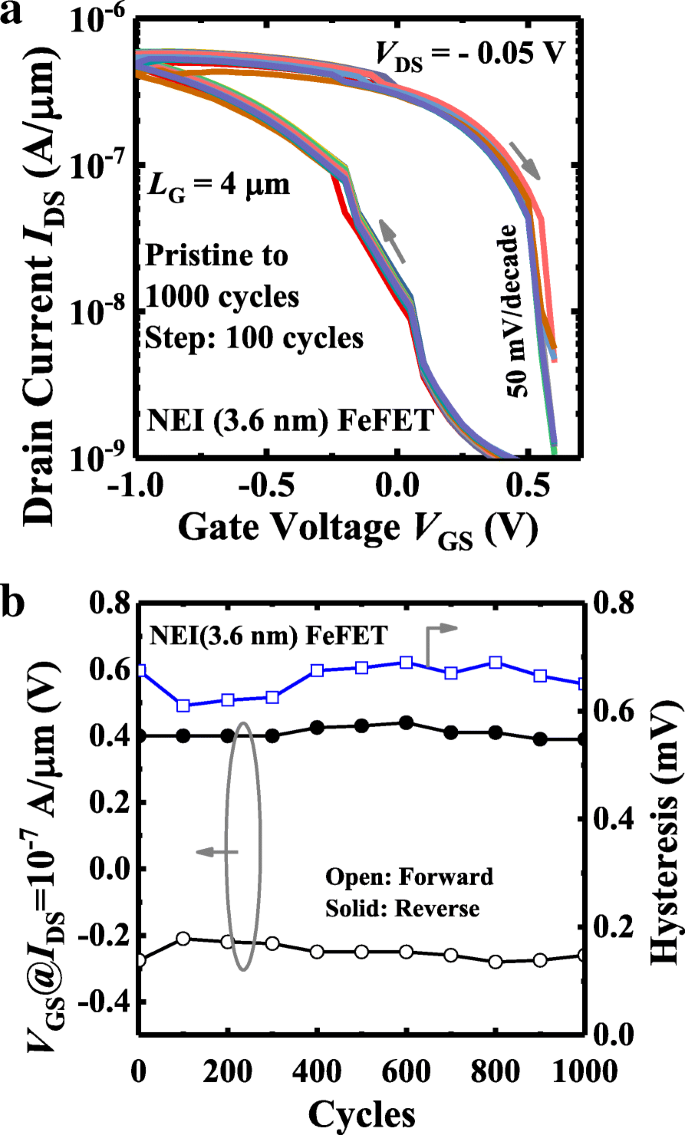

V の範囲を広げることによって GS スイープすると、NEI FeFETのヒステリシス電圧を上げて、読み取りおよび書き込み操作用の大きくて安定したメモリウィンドウ(MW)を実現できます。図10に示すように、NEIが3.6 nmのFeFETは、MWが V として0.2から1.14Vに増加することを示しています。 GS 掃引範囲は(0.1 V、− 0.1 V)から(1 V、− 2 V)まで変化します。別のFeFETメモリデバイスのDC掃引耐久性を図11aに示します。図11bは、DC掃引サイクル数の関数としてのヒステリシス特性を示しています。安定した I-V 〜0.65Vのヒステリシスウィンドウが見られます。

大きな V の場合 GS DC掃引範囲、1.14 VのMWがNEI(3.6 nm)FeFETで観察されます

a 測定された I DS - V GS 1000 DCスイープサイクルによるNEI(3.6 nm)FeFETの曲線。 b DC掃引耐久性測定は、NEIFeFETが1000サイクルを通じて安定したMWを持っていることを示しています

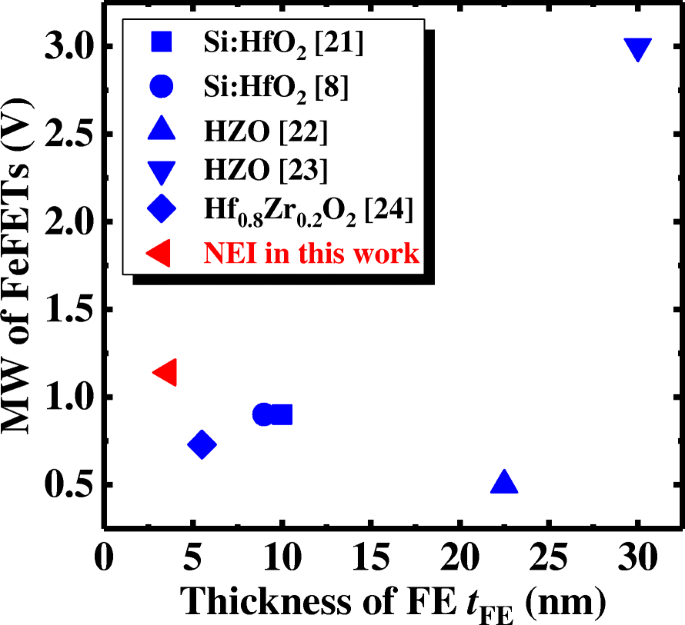

図12は、MWおよびFE層の厚さに関して、報告されたFeFETに対してNEIFeFETメモリデバイスのベンチマークを示しています[8、21–24]。この作業のNEIFeFETデバイスは、報告されている最も薄いFEの厚さ3.6 nmで、かなりの(> 1 V)MWを達成することに注意してください。ドープされたHfO 2 と比較して、より薄い厚さのNEIで安定したFE相を達成する方が簡単であると推測されます。 [28,29,30]。

MWおよび t に関して、報告されたFeFETに対するNEIFeFETメモリデバイスのベンチマーク FE 。最も薄いFEは、NEIFeFETメモリデバイスによって実現されます

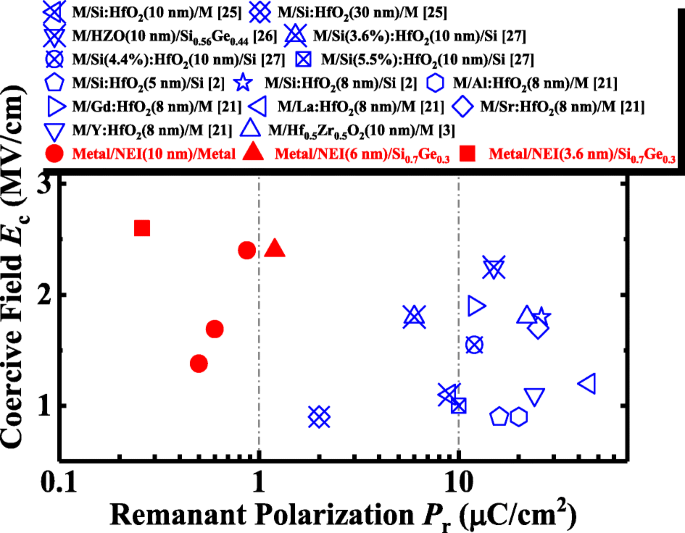

最後に、ZrO 2 によって提供されるNEIFeFETの利点 アモルファスゲート絶縁体に埋め込まれたナノ結晶について説明します。図13は、報告されたドープされたHfO 2 に対するNEI層のベンチマークです。 E に関する映画[2、3、21、25–27] c および P r 。 NEIははるかに低い P を達成できます r ドープされたHfO 2 と比較して 同様の E c 。私たちの実験では、 P r 1μC/ cm未満 2 FeFETで必要なMWを提供できます。過度の分極は、より大きな脱分極を引き起こし、保持特性を悪化させる可能性があります。これは[25]で報告されています。さらに、NEI層のFEプロパティとDEプロパティは、個別に調整できます。 P r FEナノ結晶の体積を増減することで増加/減少し、アモルファスマトリックスに他の元素を組み込むことでκが増加します(例:。 、LaAlO 3 )、FeFETのパフォーマンスを最適化するため。

報告されたドープされたHfO 2 に対するNEI層のベンチマーク E に関する映画 c および P r 。 NEIははるかに低い P を達成します r ドープされたHfO 2 と比較して 同様の E を維持しながら c。 [2、3、21、25、26、27]

結論

ZrO 2 を使用した新しいFeFET アモルファスAl 2 に埋め込まれたナノ結晶 O 3 ゲート絶縁層が報告されています。物理的分析によると、Al 2 のZrは0.5%未満です。 O 3 NCFETおよびNVMアプリケーションに十分な強誘電性を生成します。安定したNC効果は、さまざまな測定温度で観察されます。記録的な薄さ(総厚3.6 nm)のゲート絶縁体を使用した安定したFeFETメモリ動作が実証されています。安定したMWは、1000DC耐久サイクルにわたって達成されます。提案されたNEIFeFET設計は、FE / DEゲート絶縁体層の厚さを縮小して、フィンピッチが非常に小さいFinFETと互換性を持たせるための経路を提供します。

略語

- Al 2 O 3 :

-

酸化アルミニウム

- ALD:

-

原子層堆積

- BF 2 + :

-

フッ化ホウ素イオン

- DC:

-

直流

- Ec:

-

強圧的場

- FeFET:

-

強誘電性電界効果トランジスタ

- Ge:

-

ゲルマニウム

- GeO x :

-

酸化ゲルマニウム

- HF:

-

フッ化水素酸

- HRTEM:

-

高分解能透過型電子顕微鏡

- I DS :

-

電流を排出する

- MOSFET:

-

金属酸化物半導体電界効果トランジスタ

- MW:

-

メモリウィンドウ

- NC:

-

負の静電容量

- NDR:

-

負性微分抵抗

- NEI:

-

ナノ結晶埋め込み絶縁体

- Ni:

-

ニッケル

- Pr:

-

残留分極

- RTA:

-

ラピッドサーマルアニーリング

- SS:

-

サブスレッショルドスイング

- TaN:

-

窒化タンタル

- V GS :

-

ゲート電圧

- V TH :

-

しきい値電圧

- ZrO 2 :

-

二酸化ジルコニウム

ナノマテリアル

- センサーとプロセッサーは、産業用アプリケーション向けに統合されています

- 改善された診断および治療用途のための多機能金ナノ粒子:レビュー

- 合成および生物医学的応用のための蛍光ナノ材料の進歩と挑戦

- マイクロLEDおよびVCSEL用の高度な原子層堆積技術

- スーパーキャパシター用途向けのグラフェンおよびポリマー複合材料:レビュー

- スーパーキャパシター用途の電極としてのグラフェン/ WO3およびグラフェン/ CeOx構造の評価

- セレクタおよびメモリとしてのV / SiOx / AlOy / p ++ Siデバイスの二重機能

- Ge / Siチャネル形成とデバイス性能に及ぼすエッチング変動の影響

- 産業用冷凍および産業用冷却アプリケーション用のドライブ

- ボーリングおよびターニングアプリケーション用のスイング旋盤

- 医療機器用途の特殊金属