高速電圧パルス測定を特徴とするZrO2シード層を備えたHf0.5Zr0.5O2ベースのFeFETのメモリウィンドウと耐久性の改善

要約

HfO 2 金属/強誘電体/絶縁体/半導体(MFIS)ゲートスタックを備えたベースの強誘電性電界効果トランジスタ(FeFET)は、現在、高密度で高速な書き込み速度の不揮発性メモリの候補として検討されています。 HfO 2 の保持性能は MFISゲートスタックを備えたベースのFeFETは、実際のアプリケーションの要件を満たすことができ、そのメモリウィンドウ(MW)と耐久性に関する信頼性をさらに改善する必要があります。この作業では、ZrO 2 を使用する利点を調査します。 Hf 0.5 のMW、保持、および耐久性のシード層 Zr 0.5 O 2 高速電圧パルス測定を使用した、MFISゲートスタックを備えた(HZO)ベースのFeFET。 ZrO 2 を備えたHZOベースのFeFETであることがわかります。 シード層は、ZrO 2 を使用しないHZOベースのFeFETと比較して、初期および10年の外挿MWが大きく、耐久性能が向上しています。 シード層。結果は、直接結晶性のhigh-k / Siゲートスタックを使用すると、HfO 2 のMWと信頼性がさらに向上することを示しています。 ベースのFeFET。

背景

HfO 2 ベースの強誘電体薄膜は、相補型金属酸化膜半導体(CMOS)の互換性と拡張性により、強誘電体電界効果トランジスタ(FeFET)の有望なゲートスタック材料と見なされています。 FeFETで使用できる数種類のゲートスタック構造の中で、金属/強誘電体/絶縁体/半導体(MFIS)は、現在のMOSデバイスアーキテクチャに準拠し、最新のhigh-k金属ゲートとよく一致するため、より実用的な構成になります。 (HKMG)プロセス。したがって、埋め込まれた不揮発性メモリ、負の静電容量電界効果トランジスタ、人工ニューロン、シナプス、およびロジックインメモリデバイスでのアプリケーション向けに、MFISゲートスタック構造を備えたFeFETを設計および製造するために多大な努力が払われてきました[1,2,3,4 、5,6,7,8]。

これまで、MFISゲートスタック構造を備えた高密度で高速な書き込み速度のFeFETは、HKMGプロセスを使用して正常に製造されてきました[9、10]。高い積分密度と速い書き込み速度に加えて、大きなメモリウィンドウ(MW)と保持と耐久性に関する高い信頼性も、不揮発性メモリアプリケーションにFeFETを採用するために重要です[11、12、13、14]。シリコンへの大きなバンドオフセット、高い強圧場、およびHfO 2 の中程度の誘電率のため ベースの強誘電体薄膜、HfO 2 MFISゲートスタック構造を備えたベースのFeFETは、信頼性の高い保持特性(10年の外挿)を示します[15、16、17]。ただし、HfO 2 ベースの薄膜は、1×10 9 以上の中程度の耐久性を示します スイッチングサイクル[14、18]、HfO 2 MFISゲートスタック構造を備えたベースのFeFETの耐久性は、1×10 4 の範囲でかなり制限されています。 〜1×10 7 スイッチングサイクル[17、19、20、21、22、23]。理論的には、high-k絶縁体層を使用すると、MFISゲートスタック内の電界が減少し、バンドの曲がりが緩和され、HfO 2 の耐久性とMWが向上すると予想されます。 ベースのFeFET [12、14]。実験的に、アリ等。極薄絶縁体層のk値を大きくすることを確認しました(つまり、SiO 2 の代わりにSiONを使用します )HfO 2 の分子量だけでなく耐久性も効果的に向上させることができます ベースのFeFET [13]。以前の研究[24]で、結晶性ZrO 2 の挿入を報告しました。 MFISゲートスタックのhigh-k層は、結晶品質を改善し、Hf 0.5 の単斜晶相の形成を抑制する可能性があります。 Zr 0.5 O 2 (HZO)薄膜。これは、DC電圧掃引法によって特徴付けられる2.8Vの大きな分子量につながります。

この作業では、結晶性ZrO 2 がある場合とない場合のHZOベースのFeFETのMW、保持、および耐久性の特性評価について報告します。 高速の正および負の電圧パルス測定を使用して層をシードします。さらに、結晶性ZrO 2 を採用する利点 MWのシード層と耐久性について説明します。

メソッド

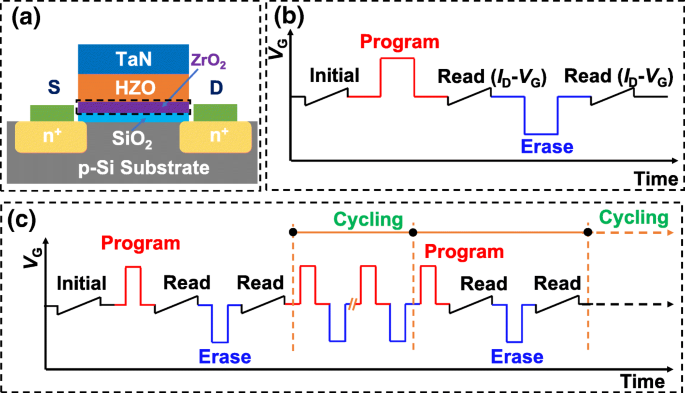

ZrO 2 がある場合とない場合のnチャネルFeFET [24]で説明されているように、シード層はゲートラストプロセスを使用して製造されました。 ZrO 2 シード層とHZO層は両方とも300 o の成長温度で成長しました 原子層堆積(ALD)によるC。製造されたFeFETの概略図を図1aに示します。そのチャネル幅( W )と長さ( L )はそれぞれ80および7μmでした。一方、TaN / HZO / TaNおよびTaN / HZO / ZrO 2 / TaNコンデンサも、HZO薄膜の強誘電特性を評価するために製造されました。分極-電圧( P-V )コンデンサのヒステリシスループはRadiant Technologies RT66A強誘電体テストシステムを使用して測定され、FeFETのデバイス特性はパルスジェネレータユニット(B1525A)を備えたAgilentB1500A半導体デバイスアナライザによって測定されました[20]。 MWと耐久性の測定に使用される2つの主要なテストシーケンスを図1bとcに示します。 MWおよび保持測定では、プログラム/消去(P / E)パルスが最初にFeFETのゲートに適用され、 I を使用してさまざまな時間間隔で読み取り操作が実行されました。 D – V G スイープ( V D =0.1 V) V を感知する TH 。通常、 V TH は、10 -7 のドレイン電流に対応するゲート電圧として決定されます。 A∙W / L [25]、MWは V の差として定義されます TH プログラムされた状態と消去された状態の間の値。持久力測定では、MWは特定の数の交互のP / Eパルスの後に測定されました。

a 製造されたFeFETの概略図。追加の結晶性ZrO 2 シードレイヤーは黒いグリッド線でマークされています。 b 、 c MWおよび耐久性の測定に使用されるテストシーケンス

結果と考察

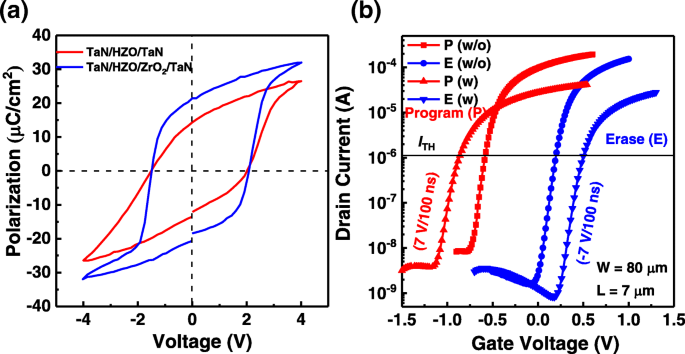

図2aは、 P–V を示しています。 TaN / HZO / TaNおよびTaN / HZO / ZrO 2 のヒステリシスループ / TaNコンデンサ。驚くべきことに、TaN / HZO / ZrO 2 / TaNコンデンサは、TaN / HZO / TaNコンデンサよりも優れた強誘電特性を備えており、報告されている結果[26]と一致しており、結晶性ZrO 2 シード層は確かに結晶品質を改善し、HZO薄膜の単斜晶相の形成を抑制することができます[24]。図2bは、 I を示しています。 D – V G 追加の結晶性ZrO 2 がある場合とない場合のHZOベースのFeFETの曲線 P / Eパルス後のシード層。赤い記号の線は I を表します D – V G 7 V / 100nsのプログラムパルスを適用した後の曲線。青い記号線は I を表します。 D – V G − 7 V / 100nsの消去パルスを適用した後の曲線。 I D – V G 両方のFeFETの曲線は反時計回りのスイッチング特性を示しており、現在のFeFETのMWは、電荷のトラップと注入ではなく、HZO層の分極スイッチングに由来していることを示唆しています。それにもかかわらず、追加の結晶性ZrO 2 を備えたHZOベースのFeFET シード層は1.4Vの改善されたMWを示し、結晶性ZrO 2 を追加しないHZOベースのFeFETの約1.8倍(0.8 V)です。 シード層。さらに、得られた1.4 VのMWは、これまでに報告された最良の結果に匹敵します[9、11、14、17、21、22、23、27]。

a P–V TaN / HZO / TaNおよびTaN / HZO / ZrO 2 のヒステリシスループ / TaNMFM構造は4Vおよび5kHzの周波数で測定されました。 b 私 D – V G ZrO 2 がある場合(w)とない場合(w / o)のHZOベースのFeFETの曲線 プログラムパルス(+ 7 V / 100 ns)および消去パルス(− 7 V / 100 ns)後のシードレイヤー

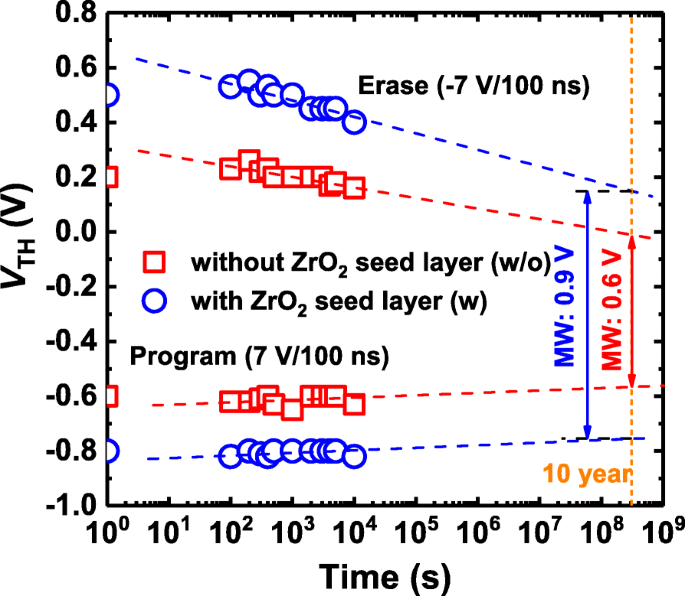

追加の結晶性ZrO 2 がある場合とない場合のHZOベースのFeFETの保持に関する信頼性 シード層も評価されました。図3は、 V を示しています。 TH 室温で7V / 100nsのプログラムパルスと–7V / 100nsの消去パルスを印加した後の保持特性。 V であることは明らかです TH 値は、対数の時間スケールに対してほぼ線形です。追加の結晶性ZrO 2 を使用したHZOベースのFeFETの10年後の外挿MW シード層は0.9Vであり、結晶性ZrO 2 を追加しないHZOベースのFeFETのシード層(0.6 V)よりも大きくなっています。 シード層。 ZrO 2 の厚い静電容量相当の厚さ(CET) (1.5 nm)/ SiO 2 (2.6 nm)ゲート絶縁体層は、ゲートスタック内の脱分極場の強化につながります[13、15]。SiO 2 の厚さがあれば、保持特性のさらなる改善が期待できます。 レイヤーが縮小されます。

ZrO 2 がある場合とない場合のHZOベースのFeFETの保持特性 シードレイヤー

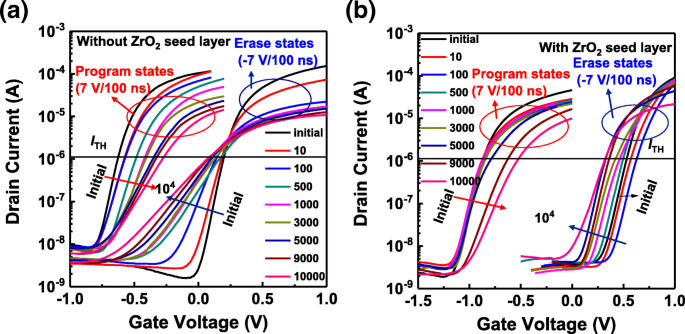

図4は、 I の進化を示しています D – V G ±7V / 100nsの交互のP / Eサイクル後の曲線。追加の結晶性ZrO 2 のないFeFETの場合 シード層、 I での大幅なシフトと傾斜の劣化の両方 D – V G 曲線は、P / Eサイクリングの初期段階、および I から観察されます。 D – V G 消去された状態の曲線は、プログラムの状態と比較して、より多くの勾配の低下を示します。追加の結晶性ZrO 2 を備えたFeFETの場合 シード層、ただし I D – V G 消去された状態の曲線は、P / Eサイクリングの初期段階で、「ウェイクアップ」効果に起因する明らかな正のシフトを示します[13、28、29、30、31、32]。 Iの明らかなシフトはありません。 D – V G プログラム状態の曲線は、1×10 3 まで観察されます。 サイクル。さらに、結晶性ZrO 2 が追加されたFeFETの場合 シード層、 I D – V G 消去された状態とプログラムされた状態の両方の曲線は、1×10 3 までわずかな勾配の低下しか示しません。 サイクル。

I の進化 D – V G HZOベースのFeFETの曲線 a なしおよび b ZrO 2 を使用 P / Eサイクリングのシードレイヤー

以前の報告[12、28、33]によると、 I の平行シフト D – V G 曲線は、ゲートスタックにトラップされた電荷が徐々に蓄積するのに対し、 I では勾配が低下するためです。 D – V G 曲線は、インターフェイストラップの生成の結果です。トラップされた電荷は電気的手段によってトラップ解除できますが、インターフェイストラップの生成は元に戻せないため、インターフェイストラップの生成を最小限に抑えることは、耐久性を向上させるために非常に重要です[28]。 P / Eサイクリングによって生成されたインターフェーストラップ(Δ N それ )式を使用して記述できます。 (1)[34、35]:

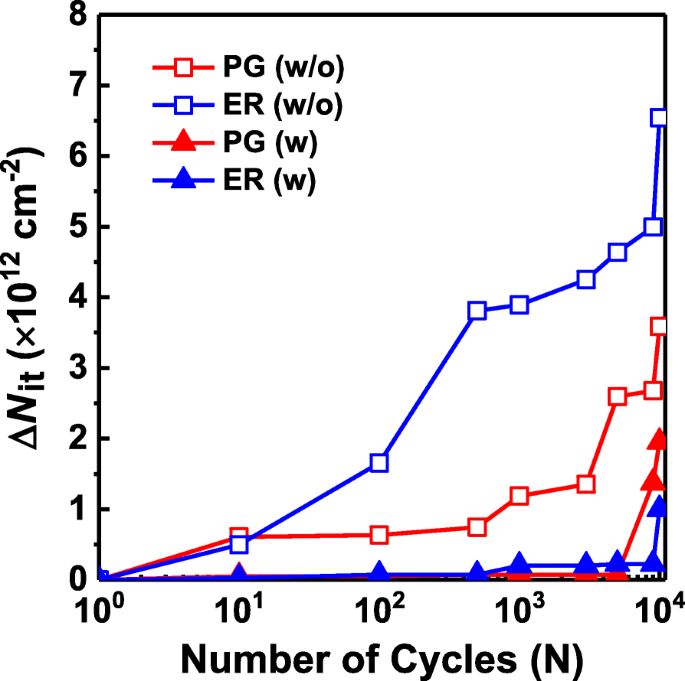

$$ \ Delta \ mathrm {SS} =\ frac {\ Delta {N} _ {it} kT \ ln 10} {C_ {FI} {\ varnothing} _F} $$(1)ここで、ΔSSはサブスレッショルドスイングの変化、 k はボルツマン定数、 T は絶対温度、 C FI はゲートスタックの総容量であり、∅ F フェルミポテンシャルです。 Δ N それ 追加の結晶性ZrO 2 がある場合とない場合のHZOベースのFeFETのP / Eサイクルの関数として シード層を図5に示します。明らかに、結晶性ZrO 2 を追加しないFeFETの場合 シード層、Δ N それ P / Eサイクリングの初期段階から明らかに増加し、Δ N それ 消去された状態の場合は、プログラムの状態の場合よりもはるかに大きくなります。ただし、Δ N それ 追加の結晶性ZrO 2 を備えたFeFETの場合 シード層は1×10 3 までほとんど変化しません サイクルであり、結晶性ZrO 2 を追加しないFeFETの場合よりも常に小さくなります。 シード層。追加のZrO 2 を挿入するため シード層はゲートスタック内の電界を低減するため、バンドの曲がりが弱くなり、界面トラップの生成が軽減されます[12、14]。

∆ N の進化 それ P / Eサイクリング付き

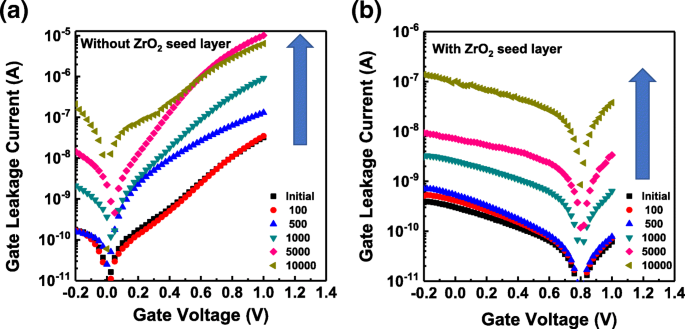

図6に、ゲートリーク電流特性( I )の変化を示します。 G – V G 曲線)ZrO 2 がある場合とない場合のHZOベースのFeFETの P / Eサイクリングを伴うシード層。追加の結晶性ZrO 2 のないFeFETの場合 シード層では、ゲートリーク電流はP / Eサイクリングの初期段階から劇的に増加します。ただし、追加の結晶性ZrO 2 を使用したFeFETのゲートリーク電流 シード層は5×10 2 までほとんど変化しません サイクルであり、結晶性ZrO 2 を追加しないFeFETの場合よりも常に小さくなります。 シード層。ゲートリーク電流の増加は、生成されたインターフェーストラップに関連している可能性があると報告されています[28]。追加の結晶性ZrO 2 を使用したFeFETのサイクリングによるゲートリーク電流の減少 シード層は、インターフェイストラップの生成の抑制に起因すると考えられます。

ゲートリーク電流特性の変化( I G – V G 曲線)HZOベースのFeFETの a なしおよび b ZrO 2 を使用 P / Eサイクリングのシードレイヤー

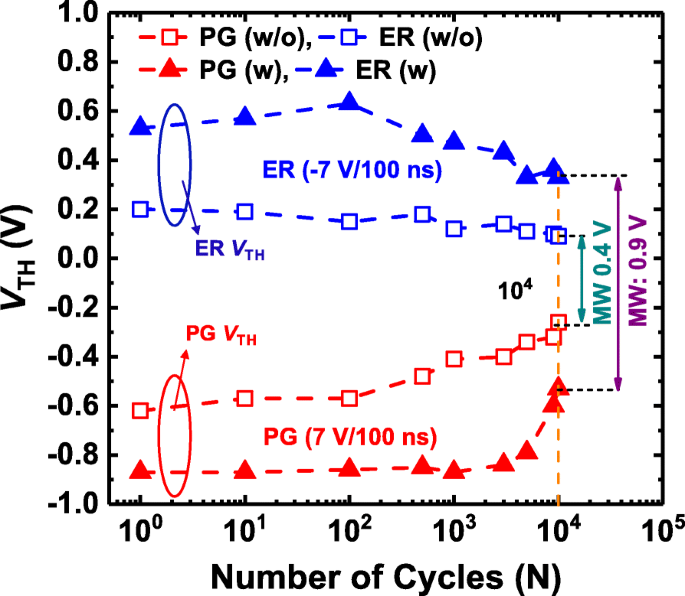

V TH I から抽出されたプログラム状態と消去状態の値 D – V G 追加の結晶性ZrO 2 がある場合とない場合のHZOベースのFeFETの曲線 シード層を図7に示します。追加の結晶性ZrO 2 を備えたHZOベースのFeFET シード層は、結晶性ZrO 2 を追加せずに、HZOベースのFeFETよりも常に大きなMWを示します。 シード層。さらに、追加の結晶性ZrO 2 を含まないHZOベースのFeFETの分子量 シード層はP / Eサイクリングの初期段階から明らかに減少しますが、HZOベースのFeFETと追加の結晶性ZrO 2 シード層は1×10 3 までわずかに減少します サイクル。 P / Eサイクリング数がさらに増えると、結晶性ZrO 2 が追加されたHZOベースのFeFET シード層も、 I の傾斜に明らかな劣化を示しています D – V G インターフェイストラップの生成が強化されたため、曲線と分子量。ただし、結晶性ZrO 2 が追加されたHZOベースのFeFETの分子量 シード層はまだ0.9Vより大きく1×10 4 サイクル。これは、追加の結晶性ZrO 2 を含まないHZOベースのFeFETの約2.3倍(0.4 V)です。 シード層。前に説明したように、より飽和した分極状態を得るために必要な電界の減少は、おそらく耐久性の改善の原因です。

V の進化 TH P / Eサイクリング付き

結論

TaN / HZO / SiO 2 を使用したHZOベースのFeFETのMW、および保持と耐久性に関する信頼性 / SiおよびTaN / HZO / ZrO 2 / SiO 2 / Si MFISゲートスタックは、高速電圧パルス測定によって特徴づけられました。結果は、追加の結晶性ZrO 2 を備えたHZOベースのFeFETを示しています。 シード層は、1.4Vの大きな初期メモリウィンドウと0.9Vの推定10年保持を示します。これは、追加の結晶性ZrO 2 > シード層。さらに、結晶性ZrO 2 を挿入することにより、HZOベースのFeFETの耐久性に関する信頼性を向上させることができます。 HZO層とSiO 2 の間のシード層 / Si基板。 ZrO 2 を使用したHZOベースのFeFETのMWと耐久性の向上 シード層は主に、HZO層の結晶品質の向上と、より飽和した偏光状態を得るために必要な電界の減少による界面トラップの生成の抑制に関連しています。この作業に基づいて、直接結晶性のhigh-k / Siゲートスタックを採用することで、HfO 2 のMWと信頼性がさらに向上することが期待されます。 ベースのFeFETであるため、さらなる研究と開発が必要です。

データと資料の可用性

この記事の結論を裏付けるデータセットは、記事に含まれています。

略語

- CMOS:

-

相補型金属酸化膜半導体

- FeFET:

-

強誘電性電界効果トランジスタ

- FeFET:

-

強誘電性電界効果トランジスタ

- HKMG:

-

High-kメタルゲート

- HZO:

-

Hf 0.5 Zr 0.5 O 2

- I D :

-

電流を排出する

- L:

-

長さ

- MFIS:

-

金属/強誘電体/絶縁体/半導体

- MW:

-

メモリウィンドウ

- P / E:

-

プログラム/消去

- P–V :

-

分極-電圧

- SS :

-

サブスレッショルドスイング

- V G :

-

ゲート電圧

- V TH :

-

しきい値電圧

- W:

-

幅

- Δ N それ :

-

生成されたインターフェイストラップ

ナノマテリアル

- ST:低コストのSO-8パッケージに豊富なアナログとDMAを備えた8ビットMCU

- 高度な農薬活性を備えたスマートナノマテリアルおよびナノコンポジット

- コンプライアンスフリーのZrO2 / ZrO2 − x / ZrO2抵抗変化型メモリと制御可能な界面マルチステートスイッチング動作

- 窒化処理を施したHfO2ベースのRRAMの伝導メカニズムと耐久性の向上

- スパイラル型アンテナによるマイクロブリッジ構造のTHzマイクロボロメータの周波数変調と吸収改善

- GeSiSnナノアイランドと歪み層を備えた半導体膜の形態、構造、および光学特性

- ソース接点とドレイン接点の距離がわずか2nmの高性能長方形ゲートUチャネルFET

- 高PSRRのナノスケール低電力抵抗なし電圧リファレンス

- 短期/長期シナプス可塑性を備えた原子層堆積Hf0.5Zr0.5O2ベースのフレキシブルメモリスタ

- SiNxパッシベーション層にフッ素イオンを注入した高絶縁破壊電圧と低動的ON抵抗AlGaN / GaN HEMT

- オリゴチオフェン薄膜における相転移と単分子層型構造の形成:その場X線回折と電気的測定を組み合わせた探索