FinFET CuBEOLプロセスにおける金属間誘電体のプラズマ誘起損傷のテストパターン設計

要約

高度なCMOSCu BEOLテクノロジーによって実現される高密度相互接続により、金属層が近接して配置されます。高アスペクト比の金属線は、広範なプラズマエッチングプロセスを必要とし、金属間誘電体(IMD)層の信頼性に懸念を引き起こす可能性があります。この研究は、近接して配置された金属線間のIMDの完全性に対するプラズマ誘起帯電効果の影響を評価するために新しく提案されたテストパターンを示しています。プラズマ帯電強度とIMD層に見られる損傷との強い相関関係が見つかり、包括的に分析されます。

はじめに

テクノロジーがサブ100nmレジームに移行するにつれて、Cuベースのバックエンドオブライン(BEOL)プロセスが広く使用されてきました。密集した相互接続は、高アスペクト比のビアで構成され、金属線は一連のプラズマ強化エッチングプロセスによって可能になります[1,2,3]。高エネルギープラズマ処理は、トランジスタのゲート誘電体スタックに重大な劣化と潜在的な損傷をもたらす可能性があることはよく知られています。これは、プロセスによって引き起こされる充電イベント中の主な放電経路であると考えられています。ゲート誘電体の品質に関する信頼性の懸念を防ぐために、ICメーカーは通常、相互接続金属層のサイズと長さを制限する設計者の規則とガイドラインを提供します[4、5]。複雑な配線システムでは金属層の数が増えるため、プロセスに起因する充電中に金属間誘電体膜を通る放電経路を回避することは困難です。 BEOLプロセスにlow-k材料を導入することで[6、7]、悪化するRC遅延の問題が軽減され、絶縁フィルムは帯電応力の影響を受けやすくなります[8、9]。複雑なBEOL配線の実現に関与するコンパクトな相互接続構造に対するプラズマ帯電による応力に起因する損傷は、高度なCMOSICの歩留まりと信頼性に大きな影響を与える可能性があります。この研究では、以前に報告されたin situ PIDレコーダ[10、11、12]を組み込み、高度なCuBEOLプロセスで追加の放電経路が可能になったときにIMD損傷の可能性を監視するための新たに提案された差動テストパターンを使用します。ウェーハ全体のさまざまな場所にあるレコーダが報告したプラズマ帯電レベルは、新しいテストパターンを通じてIMDフィルムのプラズマ帯電損傷と相関させることができます。 IMD構造の応力による故障挙動は、これらのテストパターンを通じて簡単に明らかになります。これらのテストパターンは、新しい故障モードやIMDの信頼性に関する懸念を日常的に監視するための標準的なテスト構造で使用できます。

デバイスの構造と方法論

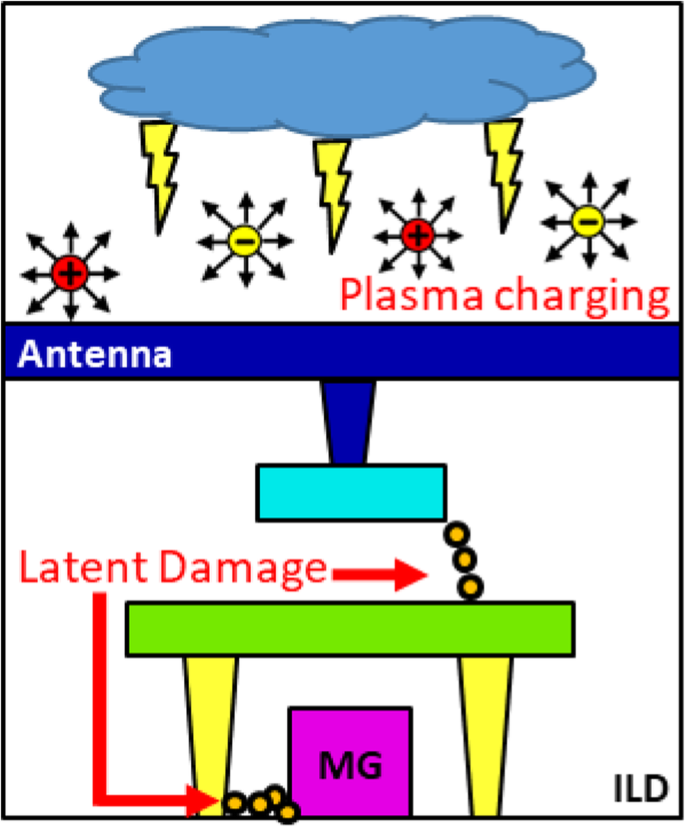

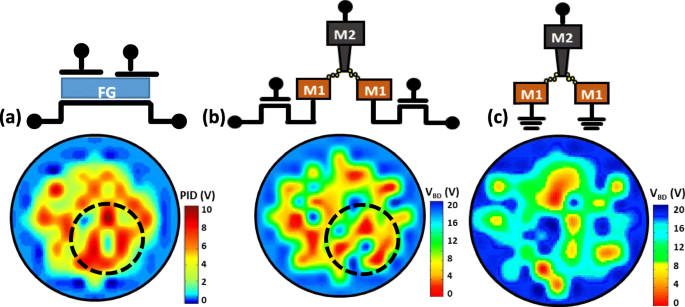

FinFET集積回路の故障解析結果は、図1に示すように、2つの近接して配置された絶縁相互接続構造間の金属間誘電体層内のトラップ状態の増加による潜在的な損傷が発生する可能性があることを示しています。事前に積極的にCMOSBEOLプロセスを削減し、大きな金属ワイヤに収集された電荷はアンテナとして機能し、IMDを介して金属、ビア/ゲート、および金属ワイヤを横切って放電し、これらの誘電体膜に高電界および/または大電流のストレスをもたらす可能性があります。各ダイの2つの差動テストパターンの隣にinsituPIDレコーダー[10、11、12]を配置することにより、12インチウェーハ全体の基準プラズマ帯電レベルを最初に確立できます。

密に詰まった相互接続パターン間の金属間誘電体層のプラズマ誘起損傷は、その分離の完全性の潜在的な劣化につながる可能性があります

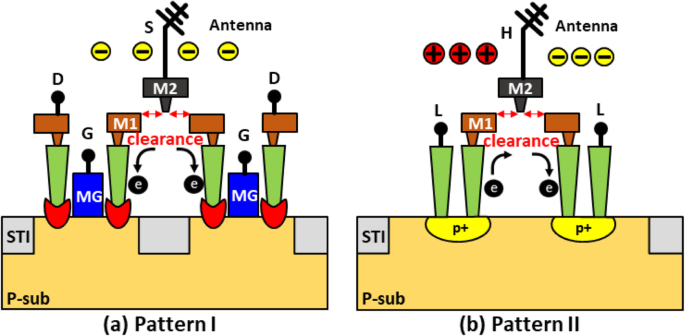

金属層間の誘電体層を通過するプラズマ充電電流を確実にするために、アンテナ構造を作成する前に、図2のテストパターンのM2ノードを分離します。プラズマ帯電応力中に潜在的な損傷を引き起こす可能性を高めることを目的とした2つの新しい差動テストパターン設計が提案され、図2a、bに示されています。タイプIパターンのデバイスは、対応するアンテナに電子が収集された場合にのみ、高電流ストレスが発生します。これは、放電電流が導電性経路上の直列のn + / p接合によって整流されるためです。一方、タイプIIパターンのデバイスは、両方向の応力Iにさらされます[13]。つまり、イオン帯電と電子帯電の両方がこの監視デバイスに登録されます。したがって、この研究のサンプルは、16nmテクノロジーノードの標準的なFinFET / CuBEOLプロセスによって作成されています。 PIDレコーダのアンテナ構造、および各ダイに配置されたタイプIおよびIIパターンのデバイスはすべて、大きな金属3構造で設計されています。どちらのタイプの監視デバイスも差動構成で設計されており、PID効果の障害読み取りにつながる可能性のあるミスアライメントノイズを強調し、その後最小限に抑えることができます。

プラズマによって引き起こされる潜在的な損傷の影響を強調するように設計された、新しく提案された差動テストパターンの図 a ネガティブで b 金属層間のクリアランスを14nmに設定する双方向応力

実験結果とディスカッション

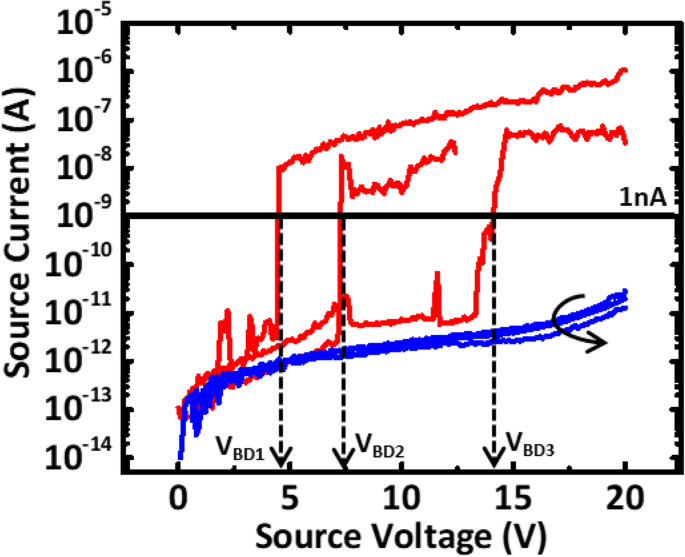

図3のデータは、金属2に0.7 V /秒の掃引速度で0〜20 Vの電圧掃引を適用し、テストパターンを使用していくつかの異なるデバイスの両側に絶縁破壊電圧とIMDリーク電流を印加することによって得られたものです。その後、取得して比較することができます。 82,000μm 2 の大型M3アンテナの製造中 、プラズマプロセスはアンテナの充電を誘発すると予想されます。蓄積された電荷は、抵抗が最も低い経路を通って放電すると予想されます。データによると、一部のサンプルは初期の絶縁破壊を示していますが、他のデバイスのIMDは比較的無傷で、リークが少ないままです。

82,000μm 2 の金属3アンテナに接続された差動テストパターンを備えたデバイスで測定された漏れ電流 。 V BD は、32nmのビア長で電流が1nAに達したときの電圧として定義されます

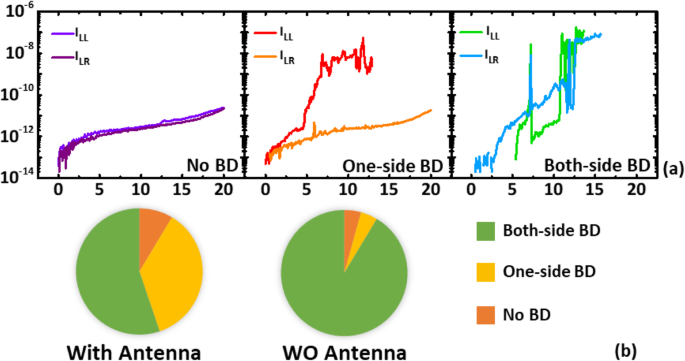

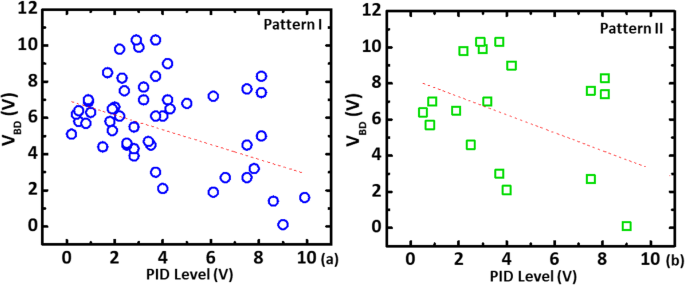

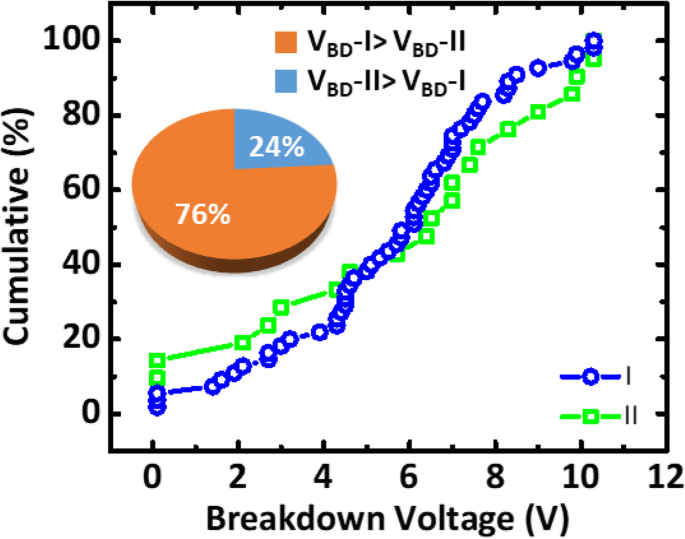

充電イベントでは、弱い側が支配的な放電経路に役立ち、左右の損傷レベルの不均衡がより顕著になると予想されます。したがって、 V が大きいデバイスのみ BD 左側と右側の違いは、プラズマ帯電に起因する可能性が高くなります。したがって、小さい V BD ペアのIMD内訳では、PIDストレスレベルに相関するレベルとして登録されます。図4aは、ウェーハ全体のさまざまなダイ上のサンプルに見られる3つの典型的な特性を示しています。これらのサンプルは、いずれかの側の内訳なし、片側の内訳、または両側の内訳グループとして分類できます。各グループの特定の特性を示すデバイスの部分は、図4bの円グラフに示されています。アンテナのないサンプルでは、片側破壊特性の変化がはるかに少ないことがわかりました。両側の対称的な動作は、プラズマ充電ストレスを経験していないほとんどのデバイスで見られます。これらはさらに、差動ペアの非対称特性のほとんどが、アンテナ構造が取り付けられているときの充電応力に起因することを示唆しています。

a ウェーハ全体のテストペアと b のさまざまなタイプの破壊特性 60を超えるダイのデバイスペアで特徴的なタイプの故障特性を示すサンプルの割合を比較する

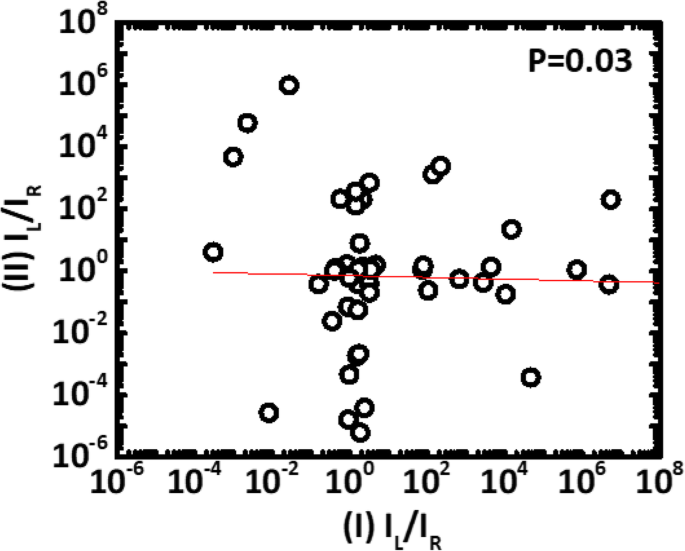

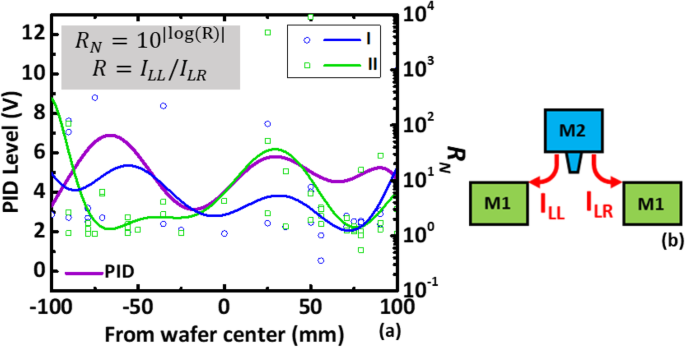

V を使用する BD 上記の方法で得られた、PIDレベルと V のウェーハマップ BD タイプIとタイプIIのパターンのデバイスからのものを図5で比較します。 V のウェーハマップ間の高い類似性 BD 両方のタイプの監視デバイスから、対応する基準充電レベルがPIDレコーダーから取得されます。図5aを参照してください。 PID電圧は、金属プロセス中の電子とイオンの両方の帯電イベントを記録すると考えられています[14]。ただし、ウェーハ全体のサンプルは、主にイオン帯電よりも多くの電子帯電を受けることがわかっています[14]。図5a、bのウェーハ間には地域的な相関関係が見られると考えられます。図5aとの明らかな類似性がないパターンIIからの図5cのウェーハマップは、双方向応力[15]が誘電体層に二次的影響をもたらす可能性があることを示唆しており、さらなる調査が必要です。図6で比較した新しいテストパターンと参照PIDレベルから測定されたブレークダウン電圧は、ダイのPIDレベルが高いほど、その V が低いことをさらに示しています。 BD 新しいテストパターン。さらに、 V 間の有意な負の相関 BD プラズマ充電レベルを確立できます。 IMD損傷に対する一方向および双方向の応力の影響を調査するには、 V BD タイプIとタイプIIのパターンで考案されたものから測定されたものを図7にまとめて比較します。 V BD ウェーハ全体の60ダイ上のデバイスから得られた分布は、デバイスが双方向の充電ストレスを経験した場合、より低い電圧でIMDブレークダウンを示す可能性が高いことを示しています。これは、IMD全体で極性が変化する際の非対称応力レベルによって説明できます[16]。さらに、誘電体層全体で10 Vで測定された応力誘起漏れ電流(SILC)は、IMD膜内のトラップ状態の増加のもう1つの指標です[17]。プロセス変動によるダイ間の変動の影響をさらに最小限に抑えるために、各ペアからの漏れ率を指標として使用して、IMDの損傷をさらに評価します。図8は、同じダイ上の2種類のデバイスのリーク電流比の間に本質的に相関関係がないことを示しています。つまり、金属1層とvia2層の間の不整合は、両方のパターンに最小限の影響しか与えません。流動比率 R 、 I として定義 LR / 私 LL は、これらのパターンのダイ間の変動からノイズを除去するためのより良い指標です。完全なバイアスのないデバイスでは、主な充電ストレスは右または左で発生しますが、これは完全にランダムである必要があります。ここでは、その分配媒体が1にない流動比率にいくつかのバイアス効果が見られます。プラズマ帯電効果による損傷のみが考慮されるようにするには、 R は、図9で説明されているように、正規化された電流比です。ウェーハ中心全体の分布プロットでは、 R N タイプIパターンのデバイスからは、PIDレコーダーからのプラズマストレスレベルがかなり近くなります。一方、 R N 双方向のストレスを受けやすいデバイスからの場合、記録されたPIDレベルでは完全に説明できません。これは、 R が大幅に高いことが原因である可能性があります N ウェーハ全体のイオン帯電イベントの追加の結果として、パターンIIのデバイスのレベル。

( a の分布を示す概略図とウェーハマップ )( b からのPID電圧とVBD )テストパターンIおよび( c )II、地域のプラズマ帯電レベルに起因する可能性のある、バックエンド誘電体層へのプラズマ誘発損傷による円で囲まれた領域内の地域効果を示しています

a のPIDレベルからのVBD間の相関 パターンIと b それぞれパターンIIサンプル[10,11,12]

V の累積分布の比較 BD ウェーハ全体の60のダイと、パターンIのブレークダウン電圧とパターンIIのブレークダウン電圧が高いサンプルの部分から

パターンIおよびIIの左側と右側の漏れ電流比は、これらのサンプルからの系統的なミスアライメントの影響がないことを示しています

a 対応するPIDレベルおよび b と比較した、ウェーハ中心全体のパターンIおよびIIサンプルからの正規化された電流比 左側の漏れ電流の定義( I LL )と右( I LR )

結論

IMDフィルムの完全性に対するプラズマ誘起帯電効果は、高度なFinFET CuBEOLプラットフォームで新たに提案された差動テストパターンを通じて調査されます。 IMD層の早期破壊とSILCの増加という形での損傷は、12インチウェーハ全体のプラズマ帯電レベルと直接相関していることがわかっています。

データと資料の可用性

該当なし。

ナノマテリアル