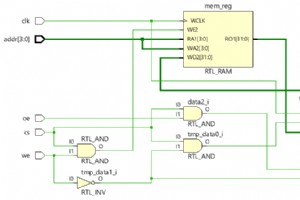

デザイン module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); reg

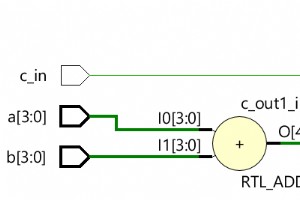

加算器は、2 つの数値の加算を実行するデジタル コンポーネントです。プロセッサの ALU 内の主要なコンポーネントであり、アドレス、テーブル インデックス、バッファ ポインタをインクリメントするために使用され、追加が必要な他の多くの場所で使用されます。 全加算器は、桁上げ入力を他の入力 2 進数と加算して、合計と桁上げ出力を生成します。 真理値表 A B シン カウト 合計 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 デザイン 4 ビッ

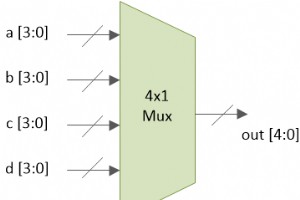

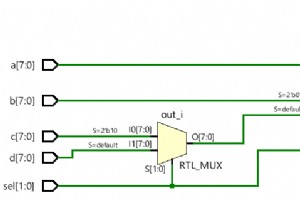

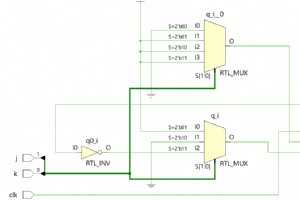

マルチプレクサまたはマルチプレクサとは? マルチプレクサまたは mux つまり、選択信号に基づいて、N 入力の 1 つから出力にデータを転送するデジタル要素です。以下に示すケースは、N が 4 に等しい場合です。たとえば、4 ビット マルチプレクサには、それぞれ 4 ビットの N 入力があり、選択信号を使用して各入力を出力に転送できます。 sel は 2 ビット入力で、4 つの値を持つことができます。選択行の各値により、入力の 1 つを出力ピン出力に送信できます。 sel a b c d out 0 3 7 1

デザイン module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if

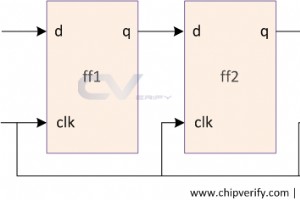

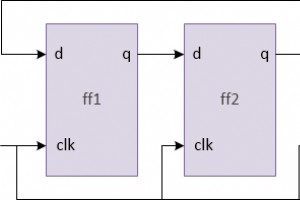

デジタル エレクトロニクスでは、シフト レジスタ 出力ピンが q であるフリップフロップのカスケードです。 1 つのフロップのデータ入力ピン (d) に接続されます。すべてのフロップは同じクロックで動作するため、シフト レジスタに格納されたビット配列は 1 桁シフトします。たとえば、5 ビットの右シフト レジスタの初期値が 10110 で、シフト レジスタへの入力が 0 に接続されている場合、次のパターンは 01011 になり、次のパターンは 00101 になります。 デザイン このシフト レジスタ デザインには 5 つの入力と 1 つの n ビット出力があり、デザインは paramet

デザイン module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int i =

デザイン module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else out

デザイン module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1)

デザイン module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) beg

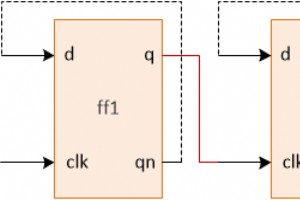

波紋 counter は、最初のフロップを除くすべてのフロップが前のフロップの出力によってクロックされる非同期カウンターです。 デザイン module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else

4 ビット カウンターは 4b0000 から 4h1111 までインクリメントを開始し、4b0000 にロールオーバーします。実行中のクロックが提供され、リセットがハイに保持されている限り、カウントを続けます。 ロールオーバーは、最終加算の最上位ビットが破棄されるときに発生します。カウンターが最大値の 4b1111 にあり、もう 1 つのカウント要求を受け取ると、カウンターは 5b10000 に到達しようとしますが、サポートできるのは 4 ビットのみであるため、MSB は破棄されて 0 になります。 0000 0001 0010 ... 1110 1111 rol

フリップフロップは、クロックの正または負のエッジで入力でデータをキャプチャします。注意すべき重要なことは、クロック エッジの後、次のクロック エッジまでにデータに何が起こっても、出力には反映されないということです。 ラッチ 一方、クロックのエッジでキャプチャするのではなく、イネーブル ピンがアサートされている限り、出力は入力に従います。 デザイン この例では、3 つの入力と 1 つの出力を持つラッチを作成します。入力 d rstn は 0 または 1 のデータを表します アクティブローリセットとenの略 イネーブルの略で、入力データを出力にラッチさせるために使用されます。リセットがアクティブ

デザイン module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule テストベンチ module tb; reg clk; reg rstn

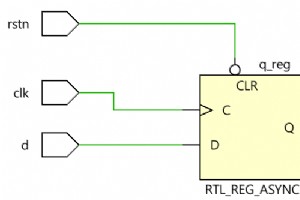

D フリップフロップ 入力ピン d に続く連続要素です クロックの特定のエッジで。 設計 #1:非同期アクティブ LOW リセット付き module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else q <= d; endmodule ハー

デザイン module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule ハードウェ

非常に単純な例を使用して開始することが常に最善であり、「Hello World !」以外に目的に最も適したものはありません。 // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some functionality module tb; // Initial block is another construct typi

Verilog には、ファイルを開く、ファイルに値を出力する、ファイルから値を読み取る、他の変数にロードする、ファイルを閉じることができるシステム タスクと関数があります。 ファイルの開閉 module tb; // Declare a variable to store the file handler integer fd; initial begin // Open a new file by the name my_file.txt // with write permissions, and store the file // handler poi

デフォルトのタイムスケール Verilog モジュールはモジュールの前にタイムスケールが定義されていることが期待されますが、シミュレータはデフォルトのタイムスケールを挿入する場合があります。システム タスク $printtimescale を使用して、Verilog エラボレートされた階層の任意のスコープで適用される実際のタイムスケールを出力できます。 スコープを引数として受け入れます。 module tb; initial begin // Print timescale of this module $printtimescale(tb); // $printtimesca

Verilog タイムスケール ディレクティブは、シミュレーションの時間単位と精度を指定します。 Verilog $timeformat システム関数は %t を指定します $display のような表示ステートメントでの形式指定子レポート スタイル と $strobe . 構文 $timeformat(<unit_number>, <precision>, <suffix_string>, <minimum field width>); ユニット番号 すべての `timescale の中で最小の時間精度です ソースコードで

Verilog 数学関数は、定数式の代わりに使用でき、両方の integer をサポートします そして本物 数学。 整数数学関数 関数 $clog2 log2 の上限を返します 指定された引数の。これは通常、特定のサイズのメモリをアドレス指定するために必要な最小幅を計算するために使用されます。 たとえば、デザインに 7 つの並列加算器がある場合、7 つの加算器すべてを表すために必要な最小ビット数は $clog2 です。 3 を生成する 7 の module des #(parameter NUM_UNITS = 7) // Use of this syste

Verilog