つまり、VHDL はデジタル回路の設計に使用されるコンピューター言語です。 私は「コンピューター言語」という用語を使用して、VHDL を Java や C++ などの他のより一般的なプログラミング言語と区別しています。しかし、VHDL はプログラミング言語ですか?はい、そうです。コンピューター プログラムを作成する際には役に立たないプログラミング言語です! VHDL は、イベント駆動型の並列プログラミング言語です。コンピュータの CPU で実行できるプログラムの作成には適していませんが、実際の CPU の作成には適しています。これはハードウェア記述言語です。つまり、デジタル ロジック

多くの場合、VHDL および FPGA ツールは非常に高価ですが、学生であれば無料で最先端のソフトウェアに簡単にアクセスできます。 VHDL を操作するためのシミュレーター、エディター、および IDE がいくつかあります。この記事では、VHDL エンジニアが使用する最も一般的な 2 つのプログラムをインストールする方法を説明します。 VHDL シミュレーター Siemens EDA (以前の Mentor Graphics) の ModelSim は、最も一般的な VHDL シミュレーターであり、最初の VHDL ジョブでは、ModelSim またはプログラムの QuestaSim フレーバ

新しいプログラミング言語を学ぶとき、私はいつも印刷方法を学ぶことから始めるのが好きです. 「Hello World!」の出力をマスターすると、環境が機能していることがわかります。また、言語の基本的なスケルトン、出力を生成するために必要な最小限のコードも示します。 VHDL はハードウェア記述言語ですが、どうすればテキストを出力できるのでしょうか? FPGA か何かに接続されたスクリーンと、その間にあるあらゆる種類のロジックが必要になりますが、それはまったく単純ではありません。これはすべて真実ですが、FPGA と ASIC のことはしばらく忘れて、VHDL 言語に注意を向けましょう。 このブ

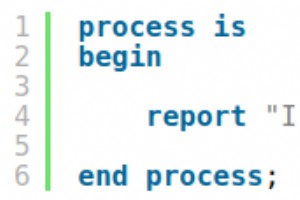

前のチュートリアルでは、プロセスをプログラム スレッドと見なすことができることを学びました。また、wait; ステートメントは、プログラムを無期限に一時停止させます。しかし、プログラムを永久以外の時間値まで待機させる方法はありますか? wait; を削除すると 完全にプログラムをコンパイルしようとすると、コンパイラは無限ループについて文句を言います。コンパイラが参照しているループは プロセス ループ です . VHDL のプロセス スレッドは決して終了せず、begin 間で継続的にループします。 と end process; ステートメント。 wait が必要です プロセス ループ内のどこか

前のチュートリアルでは、 wait for を使用して時間を遅らせる方法を学びました 声明。また、プロセス ループについても学びました。そのままにしておくと、プロセス「スレッド」がプロセス内で永久にループすることがわかりました。 しかし、プロセスの最初に一度だけ何かをしたい場合はどうすればよいでしょうか?そして、最後に他のコードをループしますか? loop を使用して、VHDL の最も単純な種類のループを作成できます。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 単純なループの構文は次のとおりです: loopend loop; このようなループは無期

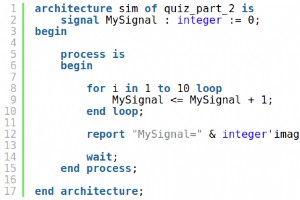

前のチュートリアルでは、loop を使用して無限ループを作成する方法を学びました。 声明。また、exit を使用してループから抜け出す方法も学びました。 声明。しかし、ループを特定の回数反復させたい場合はどうすればよいでしょうか? For ループは、これを実現する最も簡単な方法です。 For ループを使用すると、固定範囲の整数または列挙項目を反復処理できます。現在の反復に属するアイテムは、暗黙的に宣言された定数を介してループ内で使用できます。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 For ループの構文は次のとおりです。 for <c>

前のチュートリアルでは、For ループを使用して整数範囲を反復処理する方法を学びました。しかし、固定の整数範囲だけでなく、ループをより詳細に制御したい場合はどうすればよいでしょうか?これには While ループを使用できます。 While ループは、テスト対象の式が true と評価される限り、囲まれたコードを反復し続けます。 .したがって、While ループは、事前に必要な反復回数が正確にわからない状況に適しています。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 While ループの構文は次のとおりです。 while <condition>

これで、基本的な VHDL チュートリアル シリーズの最初の部分が完了しました。おめでとう!本物の VHDL の達人になるまであと数時間です。しかし、あなたは最初のステップを完了しました。それが今最も重要な部分です! 先に進む前に、このクイズで自分のスキルをテストしてください: このプロセスの何が問題になっていますか? 含まれています待機文なし セミコロンがありません「プロセスは」の後 プロセス入力がありません 正しい!違う! - 「i」の値は何回出力されますか? 無限数回の ゼロ 一度 正しい!違う! - このプロセスは何回「Haha!

前のチュートリアルでは、プロセスで変数を宣言する方法を学びました。変数は、プロセス内でアルゴリズムを作成するのに適していますが、外部からアクセスすることはできません。変数のスコープが 1 つのプロセス内にのみある場合、他のロジックとどのようにやり取りできるでしょうか?これに対する解決策は シグナル です . シグナルは architecture <architecture_name> of <entity_name> is の間で宣言されます 行と begin VHDL ファイルのステートメント。これは、アーキテクチャの宣言部分と呼ばれます。 このブログ投稿は、基本

前のチュートリアルでは、シグナルと変数の主な違いを学びました。シグナルは、1 つのプロセス内でしかアクセスできない変数よりも広い範囲を持っていることがわかりました。では、複数のプロセス間の通信にシグナルを使用するにはどうすればよいでしょうか? wait; の使い方はすでに学習済みです。 無限に待ち、wait for 特定の時間待機すること。 VHDL にはさらに 2 種類の待機ステートメントが存在します。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 Wait On ステートメントは、指定されたシグナルのいずれかが変化するまでプロセスを一時停止します:wa

前のチュートリアルでは、Wait until ステートメントで条件式を使用しました。この式により、2 つのカウンター シグナルが等しい場合にのみプロセスがトリガーされるようになりました。しかし、プロセス内のプログラムに、さまざまな入力に基づいてさまざまなアクションを実行させたい場合はどうでしょうか? If-Then-Elsif-Else ステートメントを使用して、プログラムに分岐を作成できます。変数の値または式の結果に応じて、プログラムは異なるパスを取ることができます。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 基本的な構文は次のとおりです: if

常に秘密度リストを使用する必要があります 生産モジュールでプロセスをトリガーします。機密リストは、プロセスが感知するすべてのシグナルをリストするプロセスへのパラメーターです。いずれかのシグナルが変化すると、プロセスが起動し、その中のコードが実行されます。 wait on の使い方はすでに学びました と wait until シグナルが変化したときにプロセスをウェイクアップするためのステートメント。しかし、正直なところ、これは私のほとんどのプロセスの書き方ではありません。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 VHDL コードを記述する場合、記述スタ

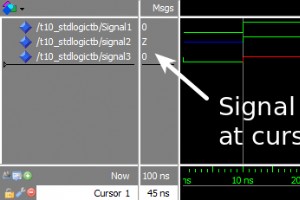

VHDL で使用される最も一般的な型は std_logic です .このタイプは、1 本の物理的なワイヤで伝送されるデジタル情報である 1 ビットと考えてください。 std_logic integer よりも、デザインのリソースをよりきめ細かく制御できます。 これまでのチュートリアルで使用してきたタイプです。 通常、デジタル インターフェイスのワイヤには 1 のいずれかの値が必要です。 または 0 .これらの 2 つの値は、ビット (2 進数) が持つことができる唯一の値です。しかし実際には、物理的なデジタル信号はさまざまな状態になる可能性があり、std_logic type はエミュレ

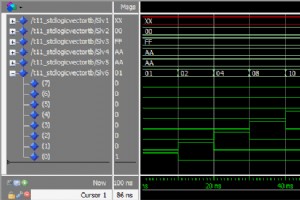

std_logic_vector タイプは、VHDL で信号バスを作成するために使用できます。 std_logic は VHDL で最も一般的に使用される型であり、std_logic_vector はその配列バージョンです。 std_logic は、1 本のワイヤで運べる値をモデル化するのに最適ですが、コンポーネントに出入りするワイヤのコレクションを実装するのはあまり実用的ではありません。 std_logic_vector 複合型です。つまり、サブ要素のコレクションです。 std_logic_vector のシグナルまたは変数 type には任意の数の std_logic を含めることができ

基本的な VHDL チュートリアル シリーズのチュートリアル 6 ~ 11 を完了した後、この VHDL クイズでコーディング スキルをテストしてください! ブログの投稿を読み、ビデオを見て、演習を行った場合は、クイズのほとんどの質問に答える資格があるはずです。クイズは意図的に少し難しいものになっています。答えがわからない場合は、推理力を使って最も可能性の高い答えを見つけてください。 各回答の後にある説明を読んでください。そこにはマイクロラーニングが含まれています。 このコードは何を出力しますか? MySignal=-2147483648 MySignal=0 MySi

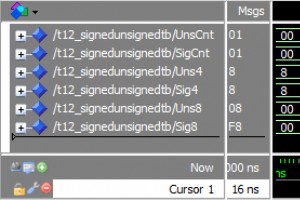

VHDL の符号付きおよび符号なしの型は、std_logic_vector 型と同様にビット ベクトルです。違いは、std_logic_vector はデータ バスの実装には優れていますが、算術演算の実行には役に立たないことです。 std_logic_vector 型に数値を追加しようとすると、ModelSim は次のコンパイル エラーを生成します:中置演算子 + の実行可能なエントリがありません。これは、ベクトルであるこのビットのコレクションを解釈する方法をコンパイラが認識していないためです。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 ベクトルを符号

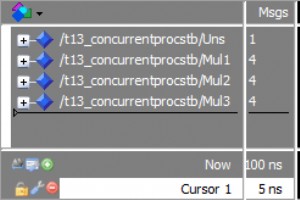

VHDL の並行ステートメントは、アーキテクチャ内のシグナル割り当てですが、通常のプロセス構造の外側にあります。同時実行ステートメントは、同時割り当てまたは同時プロセスとも呼ばれます。 コンカレント ステートメントを作成すると、実際には、明確に定義された特定の特性を持つプロセスが作成されます。並行ステートメントは常に、シグナル割り当て演算子の右側にあるすべてのシグナルがセンシティビティ リストにあるセンシティビティ リストを使用するプロセスと同等です。 これらの簡略表記プロセスは、1 つの信号を割り当てる単純なロジックを作成する場合に役立ちます。センシティビティ リストなどを含む完全なプロ

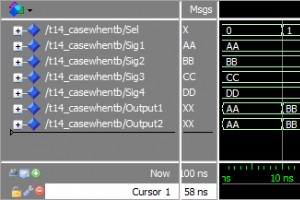

Case-When ステートメントにより、プログラムはシグナル、変数、または式の値に応じて、複数の異なるパスから 1 つを選択します。これは、複数の Elsif を持つ If-Then-Elsif-Else ステートメントのよりエレガントな代替手段です。 他のプログラミング言語にも同様の構造があり、switch などのキーワードを使用します。 、ケース 、または選択 .特に、Case-When ステートメントは、VHDL でマルチプレクサを実装するためによく使用されます。続きを読むか、ビデオを見て方法を確認してください! このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部

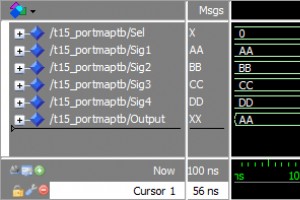

モジュールは、VHDL コードの自己完結型ユニットです。モジュールはエンティティを通じて外界と通信します . 港マップ モジュールのインスタンス化の一部であり、モジュールの入力と出力が接続されるローカル信号を宣言します。 このシリーズの以前のチュートリアルでは、すべてのコードをメインの VHDL ファイルに記述しましたが、通常はそうしません。シミュレーター用ではなく、FPGA または ASIC 設計で使用する目的でロジックを作成します。 シミュレータで実行するために作成された VHDL モジュールには、通常、入力信号も出力信号もありません。それは完全に自己完結型です。だからこそ、私たちのデ

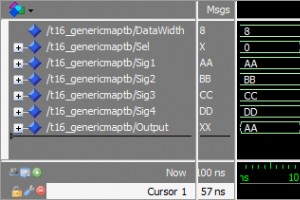

モジュールを作成することは、コードを再利用する優れた方法ですが、多くの場合、設計全体でより小さなバリエーションを持つ同じモジュールが必要になります。これがジェネリックとジェネリック マップの目的です。これにより、モジュールの特定の部分をコンパイル時に構成可能にすることができます。 定数は、同じ値を何度も入力することを避けたい場合に使用されます。これらは、コンパイル時に信号ベクトルのビット幅を定義するために使用でき、一般的な定数にもマッピングできます。定数は、コード内の任意の場所で信号と変数の代わりに使用できますが、それらの値はコンパイル後に変更できません。 このブログ投稿は、基本的な VH

VHDL