AXI モジュールにインターフェイスするためのロジックを初めて作成しなければならなかったとき、AXI インターフェイスの特殊性に少し悩まされました。通常のビジー/有効、フル/有効、またはエンプティ/有効の制御信号の代わりに、AXI インターフェイスは「ready」と「valid」という名前の 2 つの制御信号を使用します。私の欲求不満はすぐに畏敬の念に変わりました. AXI インターフェイスには、追加の制御信号を使用しないビルトイン フロー制御があります。ルールは簡単に理解できますが、FPGA に AXI インターフェイスを実装する際に考慮しなければならない落とし穴がいくつかあります。この記

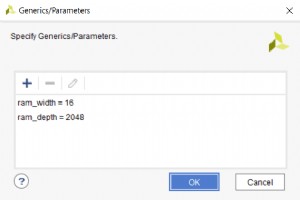

ブロック RAM に初期値を設定する便利な方法は、ASCII ファイルから 2 進数または 16 進数のリテラルを読み取ることです。これは、VHDL で ROM (読み取り専用メモリ) を作成する良い方法でもあります。結局のところ、FPGA では RAM と ROM は同じものであり、ROM は読み取り専用の RAM です。 この記事全体の例では、次の定数と RAM タイプが VHDL ファイルの宣言領域の先頭で宣言されていることを前提としています。 constant ram_depth : natural := 256;constant ram_width : natural := 32;

ファイルから信号値を読み取ることは、デバイス オン テスト (DUT) の刺激を生成する別の方法です。テストベンチのシーケンスとタイミングは、VHDL テストベンチによって 1 行ずつ読み込まれるスティミュラス ファイルにハードコードされています。これにより、テスト オブジェクトに供給したい波形のパターンを簡単に変更できます。 場合によっては、DUT に実行させたい非常に特殊なテスト パターンまたは一連のイベントがある場合があります。これを実現するには、ASCII ファイルで、各信号が持つべき信号値と、信号が変化する相対的なシミュレーション時間を指定します。このような戦略における VHDL

画像ファイルをビットマップ形式に変換すると、VHDL を使用して画像を読み取る最も簡単な方法になります。 BMP ラスター グラフィック イメージ ファイル形式のサポートは、Microsoft Windows オペレーティング システムに組み込まれています。これにより、BMP は VHDL テストベンチで使用する写真を保存するのに適した画像形式になります。 この記事では、BMP などのバイナリ イメージ ファイルを読み取り、そのデータをシミュレーターの動的メモリに格納する方法を学習します。画像をグレースケールに変換するための画像処理モジュールの例を使用します。これが被試験デバイス (DUT)

このビデオは、FPGA とプログラマブル ロジック テクノロジに関する紹介プレゼンテーションです。この 45 分間の講演は、2019 年 11 月 19 日にタイのバンコクで開催された 7 Peaks Software 主催のイベントで行いました。 プレゼンテーションのハイライトは次のとおりです。 05:07 FPGA を使用しているのは誰? 09:06 FPGA とは? 12:13 静的 RAM を使用して論理ゲートをエミュレートする方法 17:47 一般的な FPGA プリミティブ 19:51 最も安価で最も高価な FPGA 20:53 FPGA のフロアプラン 24:30 VHDL

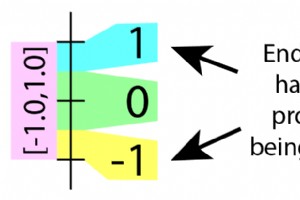

VHDL には疑似乱数ジェネレーターが組み込まれていますが、生成できるのは 0 から 1 の間の浮動小数点数のみです。幸いなことに、このジェネレーターから、必要な他の種類の乱数データ形式を派生させることができます。 real を生成する方法については、この記事を読み続けてください。 または integer 任意の範囲の値、およびランダム std_logic_vector シーケンスと time uniform IEEE MATH_REAL パッケージのプロシージャは、この記事で説明するアルゴリズムの基礎です。 uniform に注意してください ソフトウェアに依存して乱数を生成します。

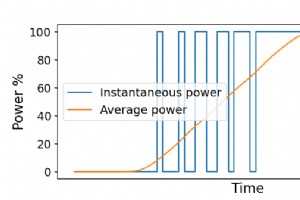

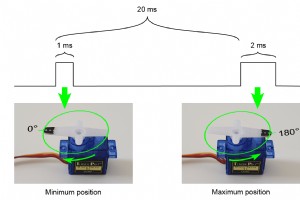

パルス幅変調 (PWM) は、純粋なデジタル FPGA ピンからアナログ電子機器を制御する効率的な方法です。アナログ電圧を安定化しようとする代わりに、PWM はアナログ デバイスへのフル パワーで供給電流をすばやくオン/オフします。この方法により、消費者向けデバイスに提供されるエネルギーの移動平均を正確に制御できます。 PWM の適切な候補となるユース ケースの例としては、オーディオ変調 (スピーカー)、光強度制御 (ランプまたは LED)、および誘導モーターがあります。後者には、サーボ モーター、コンピューター ファン、ポンプ、電気自動車用のブラシレス DC モーターなどが含まれます。

ここ数年で購入したガジェットの多くが、LED 点滅から LED 呼吸に移行していることに気付きました。ほとんどの電子ギズモにはステータス LED が含まれており、その動作によってデバイスの内部で何が起こっているかがわかります。 私の電動歯ブラシは、充電が必要になると LED を点滅させ、携帯電話はさまざまな理由で LED を使用して注意を喚起します。しかし、LED は昔のように点滅していません。これは、連続的に変化する強度を持つアナログ パルス効果のようなものです。 下の Gif アニメーションは、この効果を使用してバッテリーを充電していることを示す Logitech マウスを示しています

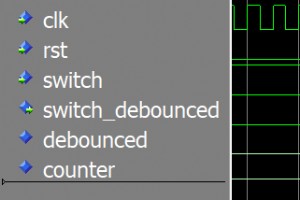

シミュレーションが完了したときに VHDL シミュレータを停止するにはどうすればよいですか?それにはいくつかの方法があります。この記事では、テストベンチの実行を成功させる最も一般的な方法を検討します。 ここに示す VHDL コードはユニバーサルであり、対応するすべての VHDL シミュレータで動作するはずです。 Tcl を含むメソッドについては、ModelSim および Vivado シミュレーターのコマンドをリストします。 ModelSim がインストールされている場合は、この記事から 4 つの異なるテストベンチを含むサンプル プロジェクトをダウンロードできます。以下のフォームにメール

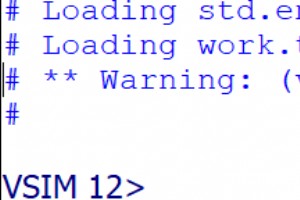

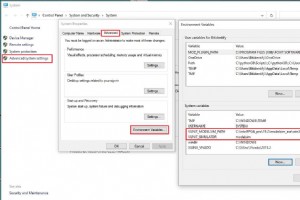

ほとんどの VHDL シミュレーターは、ツール コマンド言語 (Tcl) をスクリプト言語として使用します。シミュレータのコンソールにコマンドを入力すると、Tcl が使用されます。さらに、シミュレーターで実行され、VHDL コードと対話する Tcl を使用してスクリプトを作成できます。 この記事では、VHDL の代わりに Tcl を使用して VHDL モジュールが正しく動作することを検証するセルフチェック テストベンチを作成します。 こちらもご覧ください:Tcl を学ぶ必要がある理由Tcl を使用したインタラクティブなテストベンチ 以下のフォームを使用して、この記事と ModelS

ラジコン (RC) モデルのサーボは、一般的に愛好家の模型飛行機、車、およびボートで使用される小さなアクチュエータです。これらにより、オペレーターは無線リンクを介してリモートで車両を制御できます。 RC モデルは長い間存在しているため、事実上の標準インターフェイスはデジタル方式ではなくパルス幅変調 (PWM) です。 幸いなことに、FPGA が出力ピンに適用できる正確なタイミングで PWM を実装するのは簡単です。この記事では、PWM を使用するすべての RC サーボで動作する汎用サーボ コントローラーを作成します。 RC サーボの PWM 制御のしくみ PWM については以前のブログ

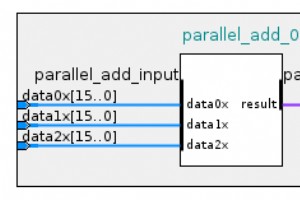

VHDL の generate ステートメントは、コードのブロックを、同一のシグナル、プロセス、およびインスタンスを持つクロージャーに自動的に複製できます。これは、連鎖プロセスまたはモジュール インスタンスを作成できるアーキテクチャ領域の for ループです。 プロセスまたはサブプログラムにのみ存在できる通常の for ループとは異なり、generate ステートメントは VHDL ファイルのアーキテクチャ領域に直接配置されます。ジェネリックと一緒に使用すると、設計間で再利用できるカスタマイズ可能な VHDL モジュールを設計するための強力なツールになります。 ステートメント構文の生成

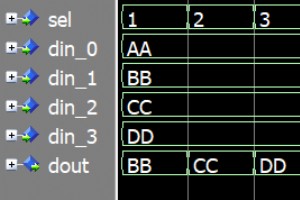

VHDL のテキスト文字列は、通常、固定長の文字配列に制限されています。 VHDL はハードウェアを記述し、一般的な長さの文字列には動的メモリが必要であるため、これは理にかなっています。 文字列の配列を定義するには、格納する最大数の文字列に対してコンパイル時にスペースを割り当てる必要があります。さらに悪いことに、文字列の最大長を決定し、すべての出現箇所をその文字数までパディングする必要があります。以下のコードは、そのような構造の使用例を示しています。 type arr_type is array (0 to 3) of string(1 to 10); signal arr : arr

このチュートリアルでは、Integrated Logic Analyzer (ILA) の使用について説明します および 仮想入出力 (VIO) ザイリンクス Vivado IDE で VHDL デザインをデバッグおよび監視するためのコア。 多くの場合、設計者はオンチップ検証を実行する必要があります。つまり、検証目的で FPGA デザインの内部信号の動作にアクセスできます。 1 つのオプションは、これらの信号を FPGA ピンに送り、それらを LED に接続して、その動作を視覚的に確認することです。このオプションは簡単で高速で、単純なケースではうまく機能しますが、柔軟性、拡張性、または現実

セーフティ クリティカルな FPGA アプリケーション用に VHDL を設計する場合、ベストエフォートでテストベンチを作成するだけでは十分ではありません。モジュールが意図したとおりに動作し、望ましくない副作用がないという証拠を提示する必要があります。 正式な検証手法は、要件をテストにマッピングして、VHDL モジュールが仕様に準拠していることを証明するのに役立ちます。これは、ヘルスケア アプリケーションを検証したり、空中 FPGA ソリューションの DO-254 認証を取得したりするためのツールです。 正式な検証を分かりやすく説明するために、VHDLwhiz は Michael Fin

VUnit は、現在利用可能な最も人気のあるオープンソース VHDL 検証フレームワークの 1 つです。 Python テスト スイート ランナーと専用の VHDL ライブラリを組み合わせて、テストベンチを自動化します。 この無料の VUnit チュートリアルを提供するために、VHDLwhiz は Ahmadmunthar Zaklouta の協力を得て、この記事の残りの部分の背後にいます。これには、コンピューターにダウンロードして実行できる単純な VUnit サンプル プロジェクトが含まれます。 アフマドに言葉を贈りましょう! このチュートリアルは、設計の検証プロセスで VUni

VUnit 検証フレームワークを介して Quartus IP コアを含む VHDL シミュレーションを実行したいと思ったことはありませんか? これは FPGA エンジニアの Konstantinos Paraskevopoulos 氏が念頭に置いていたことですが、適切なチュートリアルが見つかりませんでした。幸いなことに、彼は才能を発揮して方法を見つけ出し、このゲスト記事を通じて VHDLwhiz と共有してくれました。 . コンスタンティノスに贈ろう! VUnit でシステムをシミュレートするときに、Quartus IP カタログから定義済みの IP をデザインに組み込むことが望ましい

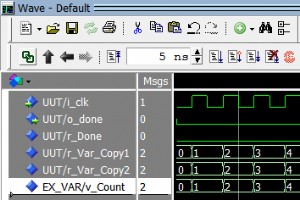

VHDL の変数は、C の変数と同様に機能します。それらの値は、変数が変更されたコード内の正確な位置で有効です。したがって、シグナルが変数 before の値を使用する場合、 割り当て、それは古い変数値を持ちます。シグナルが変数 after の値を使用する場合 新しい変数値を持つ代入。 変数のルール: 変数はプロセス内でのみ使用できます あるプロセスで作成された変数は、別のプロセスでは使用できません キーワード process の後に変数を定義する必要があります ただし、キーワード begin の前 変数は := を使用して割り当てられます 割り当て記号 割り当てられた変数は、割り当て

すべてのデジタル デザイナーは、FPGA または ASIC 内での演算の仕組みを理解する必要があります。そのための最初のステップは、符号付きおよび符号なしの信号タイプがどのように機能するかを理解することです。 numeric_std には符号付きと符号なしの型が存在します ieee ライブラリの一部であるパッケージ。数学演算を実行するために頻繁に使用される別のパッケージ ファイルがあることに注意してください:std_logic_arith .ただし、std_logic_arith は ieee がサポートする公式のパッケージ ファイルではないため、デジタル デザインでの使用は推奨されません。

VHDL の Record コンストラクトを使用すると、コードを簡素化できます。レコードは C の構造体に似ています .レコードは、新しい VHDL タイプを定義するために最もよく使用されます。この新しいタイプには、ユーザーが望む任意のシグナルのグループが含まれます。ほとんどの場合、これはインターフェイスを簡素化するために使用されます。これは、常に同じ信号の大きなリストを持つインターフェイスで非常に便利です。たとえば、オフチップ メモリへのインターフェイスが大きく、デザイン全体で何度も同じ信号を持つ場合があります。レコードを使用して、コード サイズを縮小し、エンティティで維持するシグナルを少な

VHDL