低抵抗Auオーミックコンタクトを備えた多層SnSeナノフレーク電界効果トランジスタ

要約

920°Cで修正ブリッジマン技術を使用して二重密封水晶アンプルで成長させたp型スズモノセレニド(SnSe)単結晶を報告します。 X線粉末回折(XRD)およびエネルギー分散型X線分光法(EDX)の測定により、成長したSnSeが単結晶SnSeで構成されていることが明確に確認されます。バルク単結晶からの剥離によって調製された多層SnSeナノフレークの電気輸送は、SiO 2 上にAuおよびTi接点を備えたバックゲート電界効果トランジスタ(FET)構造を使用して実施されました。 / Si基板、多層SnSeナノフレークがSnSeナノフレークの表面のSn空孔のためにp型半導体特性を示すことを明らかにします。さらに、70〜90nmの厚さのSnSeナノフレークFETで強力なキャリア遮蔽効果が観察されました。さらに、多層SnSeナノフレークベースのFETに対する金属接点の影響についても、Ti / Au接点とAu接点などの2つの異なる金属について説明します。

背景

一時的な金属カルコゲニドは、さまざまな光学バンドギャップを提供し、これらの材料をさまざまな光学およびオプトエレクトロニクスアプリケーションでの使用に適したものにします[1]。 PbTe、PbSe、Bi 2 などのこれらの材料の薄膜 Se 3 [2]は、赤外線オプトエレクトロニクスデバイス、放射線検出器、太陽電池、メモリデバイス、およびホログラフィック記録デバイスでの使用が見込まれるため、かなりの注目を集めています[3,4,5,6,7,8]。スズモノおよびジセレニド(SnSeおよびSnSe 2 )は、オプトエレクトロニクス用途に有利な高い吸収係数により、研究の脚光を浴びています。さらに、これらの材料は熱電用途での使用に有望です[9、10、11、12、13、14、15、16、17、18、19、20、21、22、23、24]。スズモノセレニド(SnSe)はp型半導体であり、間接許容遷移のバンドギャップは約0.9 eVに近く、直接許容遷移のバンドギャップは約1.2 eVに近いのに対し、スズジセレニド(SnSe 2 )はn型半導体です[6]。 SnSeの結晶構造は斜方晶系であり、そのユニットセルパラメータは a です。 =11.496Å、 b =4.151Å、および c =4.444Å;この斜方晶構造は、高温で正方晶構造に変化しますが、それでもSnSe 2 の融点よりも低くなります。 [25]。

最近、大面積の共通バックゲートを備えた電界効果トランジスタ(FET)を含む、Snベースのバイナリカルコゲニドおよびジカルコゲニド電気デバイスが広く研究されています。特に、SnジカルコゲニドベースのFETの特性評価において多くの進歩が見られました[26、27]。 2016年、Pei et al 。 数層のSnSe 2 を報告しました FET、約10 4 の高いオン/オフ比を示します 高分子電解質のトップキャッピング層を備えています[27]。 Guo etal。また、移動度の高い数層のSnSe 2 も報告されています 厚さが約8.6nmのFET [28]。以前の研究から、薄くてキャリア濃度の低いSnSe膜は、SnSe 2 の高い移動度と電流のオン/オフ比をもたらすことが確認されました。 FET。 SnSe 2 を利用するためのこれらの努力にもかかわらず ただし、単結晶からの剥離によって調製されたSnSeFETの電気的特性は報告されていません。数層および多層のSnSe 2 における電気輸送の詳細な特性評価 単一のSnSe結晶は、約7835 cm 2 の高いキャリア移動度を示すと予想されるため、SnSeナノフレークなどのスズカルコゲニドの電気輸送特性を評価するには、フレークを実行する必要があります。 / V s [29]。

この作業では、修正されたブリッジマン法を使用して成長した単結晶SnSeの特性を明らかにしました。バルク単結晶からの剥離によって調製された多層SnSeナノフレークFETの電気輸送は、SiO 2 上のバックゲートFET構造を使用して初めて特徴付けられました。 / Si基板。さらに、多層SnSeナノフレークベースのFETに対する金属接触の影響も、2つの異なるタイプの接触(Ti / AuおよびAu)について研究されました。これは、接触金属の仕事関数が、ショットキー障壁を通過する正孔キャリアの伝導を決定するためです。金属-SnSeナノフレーク界面。

メソッド

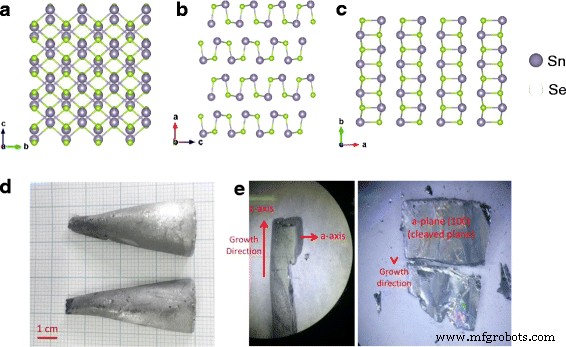

SnSeは、室温で層状の斜方晶構造を持っています[24]。図1a–cは、 a に沿ったSnSe結晶構造の斜視図を示しています。 、 b 、および c 軸方向。図1cに示すように、2原子層のSnSeスラブには溝がありますが、結晶の容易な劈開は(100)面に沿って発生します(図1b)。単一のSnSe結晶は、以前に説明されているように[24、30]、修正ブリッジマン法を使用して成長させました。化学量論量のSn(99.999%ショット、Alfa Aesar)とSe(99.999%粉末、Alfa Aesar)を最初に、二重密封石英アンプルでインゴット(〜20 g)に溶かしました。原料をゆっくりと500°Cに加熱して10時間滞留させた後、920°Cでさらに10時間保持してから、炉を停止しました。得られたインゴットを粉砕して粉末にし、円錐形の石英管に充填し、排気し、火炎シールした。この帯電した円錐形の石英管は、より大きな石英管に入れられました。外管は爆発と酸化を防ぐためにガス状のArで満たされ、次にフレームシールされました。帯電した石英アンプルは、垂直管状炉で温度勾配が最大になる位置に配置されました。垂直管状炉をゆっくりと970°Cに20時間加熱し、10時間保持した後、0.5°C / hの速度で830°Cに冷却しました。炉を830°Cでさらに24時間保持した後、100°C / hの速度で500°Cまで冷却してから、炉を停止しました。

a – c a に沿ったSnSe結晶の結晶構造 -、 b -、および c -軸方向。 d 成長した単結晶SnSeの写真。 e a に沿った劈開されたSnSe結晶の写真 -軸(100)平面。 SnSe単結晶の劈開面(100)の上面図(右の画像 d で )

結果と考察

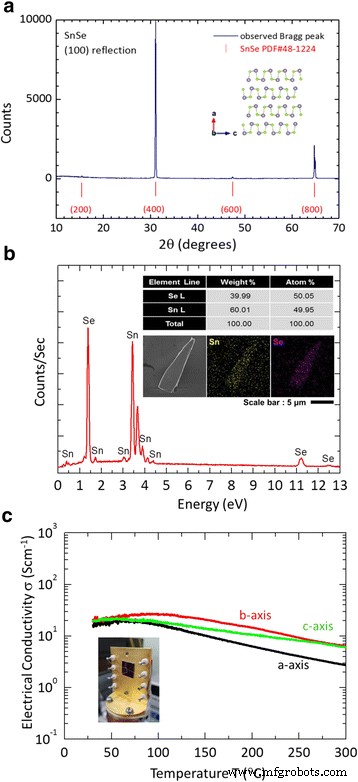

円錐形のSnSe結晶(直径30 mm、長さ70 mm)が得られ、図1d–eに示されています。得られた結晶は、水晶アンプルからの結晶の抽出中に発生した亀裂により、2つに分割されました(図1d)。成長したSnSe結晶の品質は、Cu Kαを備えた粉末X線回折計(XRD、New D8-Advance、Bruker-AXS、ドイツ)を使用してチェックしました。 (λ =1.5406Å)。図2aは、斜方晶系SnSeのパワー回折ファイル(PDF)48〜1224のXRDパターンと、結晶学的 a のパターンを示しています。 SnSe結晶の劈開面(100)に垂直な軸。図2aに示すように、単結晶SnSeのXRDパターンは、空間群 Pnma を持つ単相斜方晶を強く示唆しています。 [31]、(h00)反射を伴う強い優先配向を示し、これは以前のレポート[32]とよく一致しています。さらに、主なピークは(400)と(800)で、2 θ=でした。 図2a [33]に示すように、それぞれ31.081°と64.818°。図2bに示すように、エネルギー分散型X線分光法(EDX)により、Sn:Seの原子比が1:1であることがわかり、SnとSeの化学量論比が確認されました(図2bの挿入図)。図2bの挿入図は、デバイスの厚さが90 nmのSnSeナノフレークFETの走査型電子顕微鏡(SEM)画像とEDXマッピングも示しています。この結果は、以前の報告[24、33]とよく一致しています。さらに、単結晶SnSe(図2bの挿入図)の電気伝導率を、従来の4点プローブ法を使用して30〜300Kの範囲の温度で測定しました。図2cは、3つの異なる結晶学的方向に沿ったSnSe単結晶の温度依存電気伝導率を示しています。これは、異なる軸方向に沿ったSnSeの異なる正孔移動度による、同様の温度依存挙動と異方性挙動を示しています。図2cに示すように、 b に沿った電気伝導率 -および c -300 Kでの軸は、約6.00 S cm -1 であると決定されました。 、これは a の約2.2倍です。 -軸(〜2.7 S cm -1 )。この結果は、単結晶SnSeの以前の結果とよく一致しています[24]。図2cに、単結晶SnSeの温度依存電気伝導率を、半導体範囲(30〜100 K)と金属範囲(> 100〜300 K)で示します。 100 Kを超えると、成長したSnSe結晶は、以前の観察結果と一致する金属輸送挙動を示しました[24]。

a 明確な(h00)回折を示すSnSe単結晶のXRDパターン。 b SnSe単結晶のEDXスペクトル。挿入図 SnとSeの原子比の詳細情報を示します。 インセット デバイスの厚さが90nmのSnSeナノフレークFETのSEM画像とEDXマッピングを示します。 c 4点プローブ法を使用して測定された30〜300Kの範囲の温度でのSnSe単結晶の温度依存電気伝導率

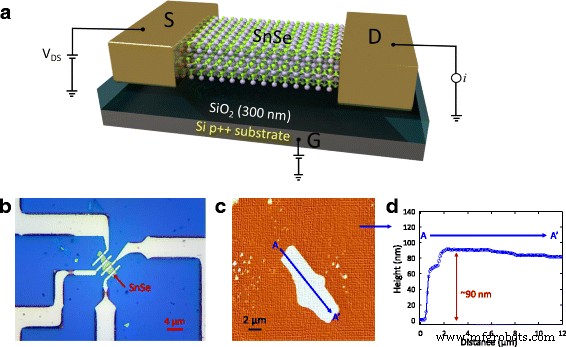

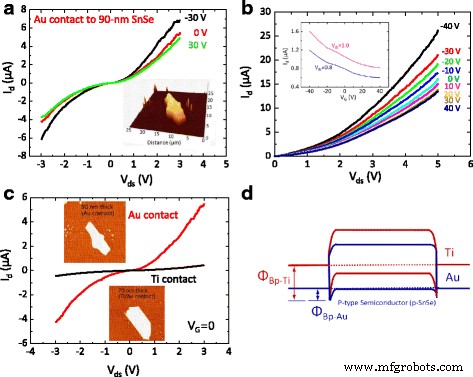

SnSeFETデバイスは次のように製造されました。まず、SnSeナノフレークを厚さ300nmのSiO 2 に機械的に剥離しました。 / p ++ 単一のSnSe結晶からのSi基板で、よく知られているスコッチテープ法を使用して(100)面で簡単に劈開されます(図1e)[26、27、34]。準備されたままの個々のSnSeナノフレークFETの電気輸送の測定は、バックゲートFET構成で室温で実行されました。図3aは、大面積のバックゲートを備えたSnSeナノフレークベースのFETデバイスを概略的に示しています。この研究では、2つのSnSeナノフレーク(70nmおよび90nmの厚さのSnSeナノフレーク)をSiO 2 上に準備しました。 / Si基板。 SnSe FETは、標準の電子ビームリソグラフィー法を使用して製造され、その後2種類の金属化が行われました。つまり、Au(厚さ、100 nm)とTi / Au(厚さ、10/100 nm)は、SnSeナノフレークのオーミック接触と見なされました。金属化プロセスの前に、緩衝酸化物エッチング(BOE)を実行して、ナノフレークの表面のポリマーと酸化物の残留物を除去しました。図3bは、デバイスの厚さが90nmのSnSeナノフレークFETの光学画像を示しています。 SnSeナノフレークの厚さは、原子間力顕微鏡(AFM)を使用して室温で測定されました(図3c–d)。図3bと図2bの挿入図に示すように、製造された厚さ90nmのSnSeFETのチャネル長は( L )でした。 )5μmおよび幅( W )4.71μm、厚さ70nmのSnSeFET L 5μmで W 6μmでした。すべての電流-電圧( I - V )特性は、室温で電気的にシールドされたプローブステーションで半導体パラメータアナライザ(HP 4155C、Agilent Technologies、米国)を使用して測定されました。図4aは、ドレイン電流( I )を示しています。 d )ゲート電圧( V )の関数として g )、厚さ90 nmのSnSeナノフレークの場合、ソース-ドレイン電圧( V ds )室温で-30、0、および30 Vであり、以前に報告されたように、主にSn空孔に起因する明確なp型半導体の挙動を示しています[15、16、22、24、35、36、37 、38,39]。図4aの結果は、仕事関数の高い金属AUがSnSeナノフレーク上に弱いオーミック接触を形成すると予想されることを示しており、SnSeナノフレークの伝導帯のショットキー障壁が低いことを示しています。さまざまな金属の仕事関数についてのより詳細な議論は、後で提供されます。図4bは、 I を示しています d 対 V ds さまざまな V g 、-40〜40 Vの範囲、10 V刻み。図4bから、穴の移動度(μ p )は〜2.7 cm 2 と決定されます / V s、μから取得 p = t m [ L ⁄( WC ox V ds)]、ここで t m は相互コンダクタンス(= dI d / dV g =2.89×10 − 8 A / V )、 L は長さ(〜5.1μm)、 W は幅(〜4.75μm)、 V ds はSnSeFETのドレイン-ソース間電圧(〜1 V)であり、 C ox (=ε r ε 0 / d =11.5 nF / cm 2 )εを使用 r (誘電率)3.9および d (酸化物層の厚さ)300 nmは、バックゲートされたSnSeナノフレークFETの単位面積あたりの静電容量です。機械的に剥離されたSnSeナノフレークFETの評価された正孔移動度は、エピタキシャルSnSe薄膜のそれよりもはるかに小さい(〜60 cm 2 / V s)Seリッチターゲットを使用したMgO基板へのパルスレーザー蒸着によって調製[40]。ただし、ここで得られる値は、単結晶SnSeナノプレートで得られる値の約1.8倍です(約1.5 cm 2 / V s)[33]。このような比較的低い正孔移動度は、SnSe表面のSn空孔[18、36、41、42]とAu金属-SnSeナノフレーク界面の比較的高いショットキー障壁による強いフォノン散乱に起因する可能性があります。

>

a SiO 2 上の機械的に剥離されたSnSeナノフレークFETの概略図 / p ++ Si基板。 b 電気輸送測定に使用された、製造されたSnSeナノフレークFETの光学画像。 c SiO 2 上のSnSeナノフレークのAFM画像 / Si基板。 d 厚さを推定し、FETデバイスを製造するためのSnSeナノフレークのAFM高さプロファイル

a 電流を排出します( I d )印加されたソース-ドレイン電圧( V )の関数として ds )、ゲート電圧( V g )、室温で、厚さ90 nmのSnSeナノフレークFETの場合、-30、0、および30V。 b 私 d 対 V ds V の場合 g 厚さ90nmのSnSeナノフレークFETの場合、10 V刻みで-40〜40Vの範囲。 挿入図 I を表示します d 対 V g V の場合 ds 室温で測定した0.8および1.0V。 c 私 d 対 V ds V にバイアスをかけずに g (=0)SnSeナノフレークFETのAuおよびTi接点の場合。 挿入図 は、SnSeナノフレークのAFMスキャン画像を示しています。 d p型SnSe半導体上の2つの金属、AuとTiのエネルギーバンド図の概略図

さらに、 I の空乏領域でコンダクタンスの弱いゲート調整が観察されました。 d 対 V ds 曲線(図4c)と低電流のオン/オフ比( V で約2) ds 1 Vの、図4cの挿入図)、Au金属接点を備えたp-SnSeナノフレークFET。同様の動作が、SnS FET(厚さ、約50〜80 nm)[43]、約15.8 nmの厚さのSnSeナノプレート[33]、約80など、同様の厚さの他の2次元(2D)半導体材料で報告されました。 -nm-thick MoS 2 [44]、および〜84nmの厚さのSnSe 2 [26]。これらの動作は、スクリーニング長よりも厚いFETデバイスに表面導電性表面層が存在することによる有限キャリアスクリーニング長効果によって説明できます\(\ left(\ sqrt {\ varepsilon {K} _B T} {e } ^ 2 p \ right)\)、ここでε 、 K B 、および p は、それぞれ半導体の誘電率、ボルツマン定数、および正孔キャリア密度です[43]。

金属接点は、2DFETデバイスの特性を重要に決定します[45]。 SnSeに対する金属の仕事関数の影響を判断するために、SnSeナノフレークの金属接点としてAu(仕事関数、〜5.1 eV)とTi(仕事関数、〜4.3 eV)を検討しました。図4cは、典型的な I を示しています d 対 V ds ゲート変調のない曲線( V g =0)AuおよびTi接点を備えたSnSeナノフレークFETの場合、Au(〜0.56MΩ)と比較してTi(〜15.4MΩ)の全体的な抵抗が高いことを示しています。したがって、金属とSnSeの界面でのショットキー障壁は、Tiの方が高くなります(図4c)。この動作は、Ti接点を備えたすべてのSnSeFETで常に観察されます。図4dに示すように、金属の仕事関数が減少すると、穴のショットキー障壁の高さが増加します。したがって、仕事関数が大きいPd、Au、Ptなどの金属は、p-SnSeナノフレークFETのオーミック接触として適しています。これらの金属では、正孔を注入するためのショットキー障壁の高さが低くなるためです。 SnSeナノフレーク上の金属接触としての適合性を判断するために、追加の金属の接触抵抗を測定する必要があります。この問題は現在、転送長法を使用して対処されています。

結論

要約すると、多層SnSeナノフレークは、SiO 2 上にバックゲートFET構造を持つSnSeFETチャネル用に成長、剥離、および特性評価されました。 / Si基板。電気輸送測定は、Au金属接点を備えた多層SnSeナノフレークが、剥離したSnSeナノフレークFETで比較的低いショットキー障壁と低い接触抵抗を備えたp型半導体特性を示すことを示しました。さらに、この研究は機械的に剥離されたSnSeナノフレークベースのFETを報告した最初の研究であり、当社のSnSeナノフレークFETは、2D電気デバイスだけでなく、次世代の熱電を含む環境発電アプリケーションにも非常に有望であると確信しています。 。

ナノマテリアル