エッチングストッパーナノレイヤーを介したクリーンなインターフェースプロセスを使用したa-IGZOTFTデバイスのパフォーマンスの向上

要約

工業生産用のアモルファスインジウム-ガリウム-亜鉛-酸化物(a-IGZO)ベースのディスプレイバックプレーンの技術的および経済的障害を克服するために、クリーンエッチングストッパー(CL-ES)プロセスが開発され、a-IGZOベースの薄膜トランジスタが製造されます。第8.5世代ガラス基板(2200mm×2500mm)での均一性と再現性が向上したフィルムトランジスタ(TFT)。バックチャネルエッチング(BCE)構造のa-IGZOベースのTFTと比較して、新しく形成されたESナノレイヤー(〜100 nm)とa-IGZOナノレイヤー(30 nm)とソースドレインの同時エッチング電極層は、CL-ES構造のIGZOベースのTFTデバイスに最初に導入され、大面積ディスプレイ用のデバイスの均一性と安定性を向上させます。 8.05 cm 2 の飽和電子移動度 / Vsと V th CL-ES構造のa-IGZOベースのTFTデバイスで0.72Vの均一性を実現。 3600秒間の±30Vバイアスでの負バイアス温度照明ストレスおよび正バイアス熱ストレス信頼性テストでは、測定された V th CL-ES構造のデバイスのシフトは-0.51および+1.94 Vに大幅に減少しました。これは、BCE構造のデバイスのシフト(-3.88 V、+ 5.58 V)よりもはるかに低くなっています。 CL-ES構造のa-IGZOベースのTFTデバイスの電気的性能は、LCD製造のためのシリコンベースのTFTプロセスから金属酸化物半導体ベースのプロセスへの経済的な移行が非常に実現可能であることを意味します。

背景

フラットプレーンディスプレイ業界では、より高い解像度とより大きなパネルサイズを備えた薄膜トランジスタ(TFT)バックプレーンが強く望まれています。電子移動度の高い半導体材料は、TFTバックプレーンの性能を向上させるために重要です。特に、金属酸化物半導体ベースのTFTバックプレーンは、機械的柔軟性と電子移動度の観点からシリコンベースのTFTバックプレーンの制限を克服するための有望な候補と見なされています[1,2,3,4]。金属酸化物半導体ベースのTFTバックプレーンは有望な特性を示しますが、工業用途向けの大規模な堆積の両方に低コストのプロセスを使用するプロセス方法が依然として必要です[5]。

アモルファスインジウム-ガリウム-亜鉛酸化物(a-IGZO)は、高い飽和電子移動度(〜5–10 cm 2 )を備えた優れた金属酸化物半導体です。 / V s)および低オフ電流(<10 pA)[6,7,8,9,10]。 a-Si:HベースのTFTバックプレーンの一般的な工業生産方法は、5マスクバックチャネルエッチング(BCE)プロセスです。ただし、a-IGZOナノフィルムは、BCEプロセスで現在使用されている一般的なエッチャントに対して非常に低い耐薬品性を備えています。特に、a-IGZOナノフィルムは、リン酸、硝酸、酢酸からなるAlエッチャントにさらされると、数秒で完全にエッチングされます[11、12、13]。この制御不能な高速エッチングは、a-IGZOベースのTFTバックプレーンにBCEプロセスを採用するのを妨げます。 BCE構造のバックプレーンでa-IGZOを利用するために、H 2 をベースにしたCu配線プロセスで使用されるエッチャントとして、Cu配線技術が開発されました。 O 2 、Al配線で使用されているものよりもa-IGZOナノフィルムに対してはるかに穏やかです[11、13]。残念ながら、よりマイルドなエッチャントを使用した場合でも、Cu配線プロセス中にa-IGZOナノフィルムが損傷します。よりマイルドなエッチャントでも、TFTデバイスのバックチャネルを形成するa-IGZOナノフィルムの表面に損傷を与えます。これらの損傷は、a-IGZOナノフィルムの表面近くの化学量論的分子組成比の崩壊を引き起こし、大面積ディスプレイの均一性とTFTデバイスの信頼性を悪化させます。これまで、従来の6マスクエッチングストッパー(CV-ES)プロセスが開発され、エッチングストッパー層(ESL)構造を備えたa-IGZOベースのTFTバックプレーンが製造されています[14、15]。ただし、この6マスクESプロセスは、マイナスの経済的実現可能性につながる可能性があります。さらに、この薄膜層の数の増加は、層間のオーバーラップ領域を増加させ、寄生容量の増加と開口率の減少をもたらします[16、17、18]。最近、ハーフトーンとリフトオフ技術を使用してTFTバックプレーンを製造する5マスクESプロセスが報告されていますが、アクティブ層の表面がまだ露出しているため、このプロセスはa-IGZOベースのTFTバックプレーンの製造には利用できません。最後のステップでストリッパーやフォトフォトなどの化学物質を処理します。これにより、a-IGZOがかなり汚染され、デバイスの品質と生産歩留まりが低下する可能性があります[19、20、21]。そのため、均一性と安定性に優れたa-IGZOベースのTFTバックプレーンの工業生産方法は依然として困難です。

本論文では、a-IGZOベースのTFTバックプレーンの製造にESLを導入することにより、クリーンな5マスクESプロセス(CL-ES)を提案します。この新しく開発されたCL-ESプロセスは、BCEデバイスの既存のプロセスとの互換性が高くなっています。このCL-ESプロセスは、BCEプロセスと同等のマスクを持つように設計されているため、既存のAM-LCDTFTバックプレーンFABの生産性の低下はごくわずかです。 a-CL-ESプロセスを使用して製造されたIGZOベースのバックプレーンは、ゲート絶縁体、IGZOナノ層、ESナノ層を順次堆積し、ドライエッチング法により新しいESLマスクを形成します。これにより、a-IGZOナノレイヤーとその界面がエッチャント、ストリッパー、溶媒から汚染されるのを防ぐことができます。この新しく形成されたナノマスクは、TFTデバイスの均一性と安定性を向上させるのに役立ちます。従来のBCE構造のデバイスと比較して、CL-ES構造のa-IGZOベースのデバイスは、電気的性能が向上しています。つまり、飽和電子移動度が高く、開口率が高く、消費電力が低くなっています。

メソッド/実験

a-IGZOベースのTFTバックプレーンの製造

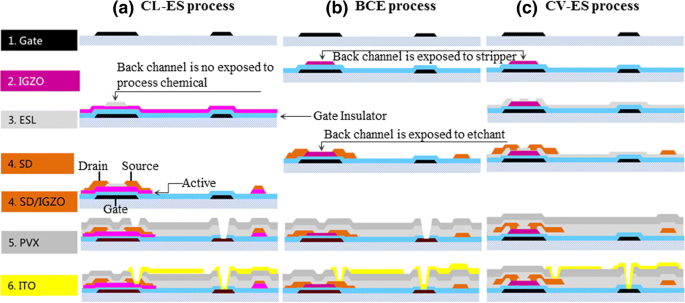

CL-ESプロセスで製造されたES構造のa-IGZOベースのTFTバックプレーンは次のとおりです(図1)。

(オンラインカラー) a の概略図 CL-ES、 b BCE、および c CV-ESプロセス

まず、ゲート電極には抵抗率が適度に低いため、二重層(Mo / Cu:30 nm / 250 nm)を使用しました。次に、ゲート絶縁体である窒化ケイ素(SiNx)/酸化ケイ素(SiOx)(300 nm / 100 nm)を、プラズマ化学気相成長法(PECVD)法で堆積しました。このSiNx膜は、Cuのメタライゼーションの酸化とゲート絶縁体へのCuイオンの拡散を防ぐように設計されています。続いて、SiOx薄膜が堆積された。 PECVD SiOx膜の堆積条件は、17 KW RF電力、1000 mTorr圧力、1:55 SiH 4 でした。 / N 2 Oガス比、および350°Cの温度。次に、DCロータリーマグネトロンスパッタを使用して、a-IGZOナノフィルムを30nmまで蒸着しました。組成がIn 2 である間、ターゲットの直径は171mmでした。 O 3 :Ga 2 O 3 :ZnO =1:1:1 mol%。 a-IGZOナノフィルムのスパッタリングパラメータは、5〜9×10 -7 のシステムベース圧力でした。 Torr、rfスパッタリングパワー10 KW、スパッタリング圧力5 mTorr Ar / O 2 ガス混合物(85%Ar-15%O 2 )。堆積温度は室温です。製造されたa-IGZOフィルムは、330°Cで1時間、清浄な乾燥空気環境でアニーリングされます。

第二に、エッチングストッパー(ES)ナノ層(SiOx)がPECVD法を使用して堆積されました。 ESナノレイヤーは、a-IGZOレイヤーの汚染を防ぐために同時に堆積されます。 BCEプロセスと同様に、S / D電極パターニングプロセス前のa-IGZOナノフィルムの保護層はなく、表面の汚染、TFTチャネル形成時のS / Dエッチャントによるa-IGZOナノフィルムの損傷は避けられません。 CL-ESプロセスのESナノレイヤーは、TFTチャネルを外部の汚染や損傷から効果的に保護できます。 ESナノ層は100nmの厚さに堆積されました。 SiOx薄膜の堆積条件は、17 KW RF電力、1000 mTorr圧力、1:66 SiH 4 でした。 / N 2 Oガス比、および240°Cの温度。製造されたESナノマスクは、ドライエッチングとパターニングによってエッチングされました。エッチングプロセス中、CF 4 およびO 2 ガスは2000sccm / 800sccmの速度で供給されました。

第三に、Mo / Cu / MoはS / D電極にも使用されました。 a-IGZOTFTのS / D電極を選択するために、金属とa-IGZOの仕事関数の違いがオーミック接触と低抵抗率材料を形成すると考えられました。エッチングストッパープロセスで説明したように、ESナノマスクのパターニング中に、エッチングストッパー層によって保護されていないa-IGZOナノフィルムは、CF 4 <で衝撃を受けることによってすでに伝導されています。 / sub> プラズマ。したがって、オーミック接触はMo / Cu / Moと自然に形成されます[22]。 S / D層は、ゲート電極と同じスパッタリング条件で30 nm / 300 nm / 30nmの厚さで堆積されました。また、「H 2 」を用いて、Mo / Cu / Moとa-IGZOの多層膜をバッチエッチングしました。 O 2 S / D電極を完成させるためのフッ化物添加剤を含むベースのCuエッチャント」。 Cuの上に追加された30nmのMoは、次のプロセスでのパッシベーション膜(SiOx)によるCu表面の酸化を防ぎ、パッシベーションホール形成のためのドライエッチング中のCu表面のプラズマ損傷を防ぐために形成されました。

第四に、2種類の薄膜に分割されたパッシベーション膜をPECVD法を使用して堆積させた。最初のパッシベーションは、SiOx薄膜で行われました。薄膜の厚さは250nmでした。 SiNx薄膜で構成される2番目のパッシベーション。薄膜の厚さは200nmでした。

第五に、画素電極として、ディスプレイ業界で最も一般的に使用されているインジウムスズ酸化物(ITO)膜を利用した。 ITO膜の厚さは40nmで、蒸着にはDCスパッタリングを使用しました。次に、熱風オーブンを使用して、230°Cのクリーンな乾燥空気環境で1時間最終アニーリングを実行しました。製造されたa-IGZOTFTの電気的特性は、Keysight4082Aパラメトリックテストシステムを使用して測定されました。このプロセスでは、大量生産で広く使用されているBCEプロセスと同じ数のマスク(TN製品標準:5つのマスク)が得られます。

比較のために、BCE構造のa-IGZOベースのTFTバックプレーンをBCEプロセスで製造しました。

特性評価

TFTのI-V測定は、半導体特性アナライザーを使用して室温で実施されました。負のゲートバイアス温度照明ストレス(NBTIS)下でのTFTの安定性を評価するための分析条件は次のとおりです。 V gs および V ds それぞれ-30Vと15Vに固定し、基板の温度を60°Cに維持しました。 NBITSの輝度は5000cd / m 2 に設定されました 。評価のためのストレスの持続時間は3600秒間続きました[23]。正のゲートバイアス熱応力(PBTS)は、 V でテストされました。 gs 30Vと V ds 15 Vで、基板温度は60°Cに設定しました。評価のためのストレスの持続時間は3600秒間続きました[24]。

結果と考察

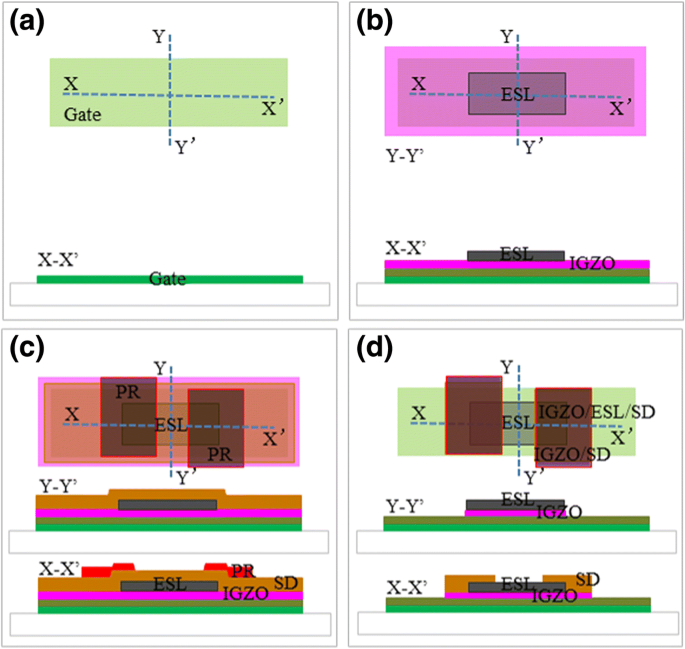

CL-ESプロセスで製造されたa-IGZOベースのTFTは、BCEプロセスと同じマスク番号を示しています(図1)。 BCE構造のa-IGZOベースのTFTと比較して、CL-ES構造のa-IGZOベースのTFTには2つの利点があります。(1)CL-ESプロセスを使用して製造されたa-IGZOベースのバックプレーンはゲート絶縁体、a-IGZOナノ-層、ESナノ層を順次、ドライエッチング法によりESLナノマスクを形成します。この新しく形成された100nmのESLナノマスクは、a-IGZOナノフィルムがエッチャント、ストリッパー、またはフォトレジストにさらされるのを防ぐことができます。したがって、層間界面での汚染は効果的に防止されます[25]。 (2)同時に、a-IGZOナノフィルムはES層では保護されていませんが、CF 4 で衝撃を受けています。 したがって、ESLナノマスク形成中のプラズマは導体になります。これにより、次のプロセスのS / D電極とa-IGZO半導体の間にオーミック接触が自然に形成されます。別の部分では、S / Dとa-IGZOナノレイヤーの同時エッチングは、ESL-(a-IGZO + S / Dメタライゼーション)レイヤーの1つのオーバーレイ許容値であり、a-の2つのオーバーレイプロセスエラーを減らすことができます。従来のESLプロセスにおけるIGZO-ESLおよびES-S / Dメタライゼーション層(図2)。 a-IGZO、ES、S / D層のオーバーレイ数が減少し、TFTデバイスのサイズが小さくなり、寄生容量が低下しました。結果の平面構造はBCE構造に似ています(図3a、b)。

(オンラインカラー)CL-ESプロセスにおけるTFTチャネルとS / D電極の同時形成法の概略図。 a ゲート電極を形成する最初のステップ。 b エッチングストッパー層を形成する2番目のステップ。 c S / D写真パターンを形成する3番目のステップ。 d S / D電極とアクティブパターンを形成する4番目のステップ

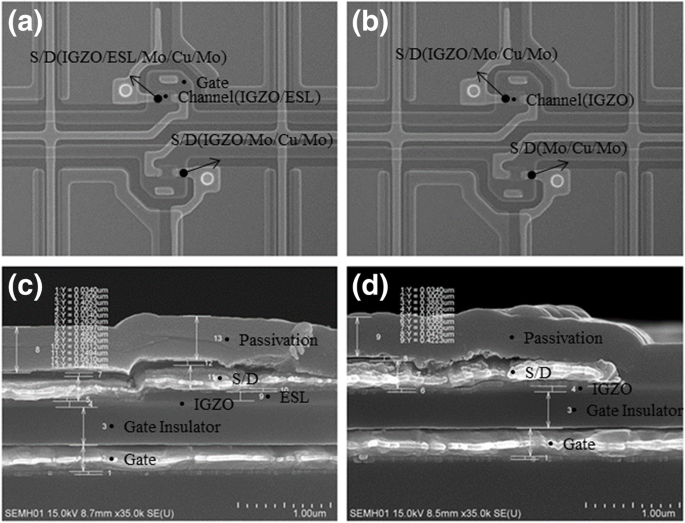

(オンラインカラー)a-IGZO TFTのSEM画像( a 、 b 上面図; c 、 d 側面図)CL-ES構造( a 、 c )およびBCE構造( b 、 d )

図3は、CL-ES構造(図3a、c)とBCE構造(図3b、d)を備えたa-IGZOベースのTFTのSEM画像を示しています。上面から見ると、CL-ES構造とBCE構造の違いを特定することは困難です(図3a、b)。側面から見ると、CL-ES構造のa-IGZOナノ層とS / D電極層の間にESナノ層が見られます(図3c)。一方、不動態化層は、BCE構造のa-IGZOナノ層の上部にあります(図3d)。提示されたCL-ESプロセスでは、厚さ30nmのa-IGZOナノ層が堆積されます。さらに、ウェットエッチング中の損傷はごくわずかです。 BCEプロセスでは、70 nmのa-IGZOナノ層が堆積されます。これは、a-IGZO層がエッチング損失の補償を必要とするためです。 CL-ES構造とBCE構造のa-IGZOナノレイヤーの厚さの違いは、SEM画像で確認できます(図3c、d)。

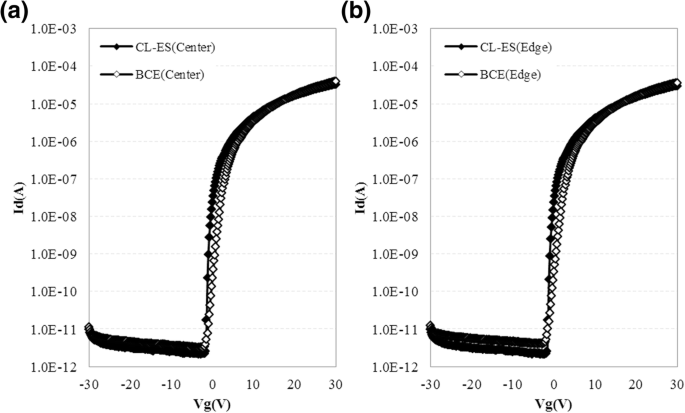

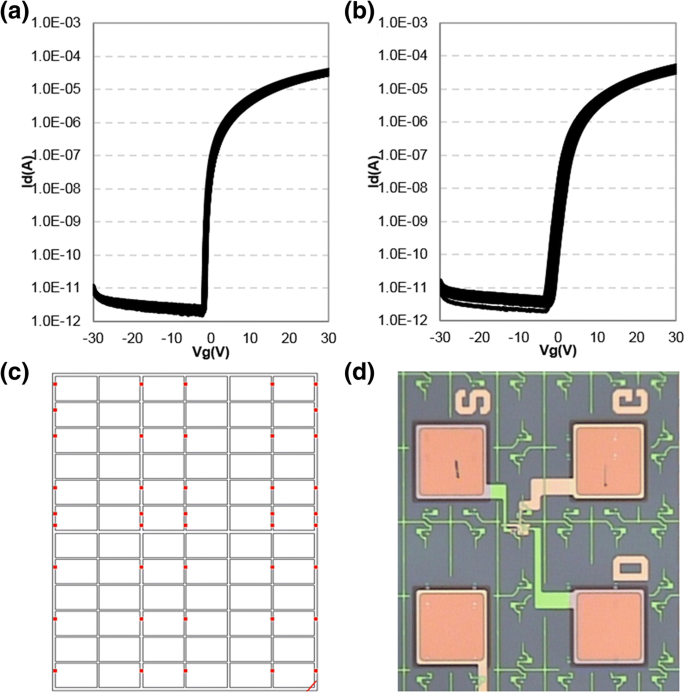

CL-ES構造とBCE構造のa-IGZOベースのTFTのI-V特性を比較します(図4)。飽和電子移動度、しきい値電圧、サブスレッショルド電圧スイング(SS)値、およびその他の特性値を表1にまとめています。表1にまとめた値は、8.5世代のガラス基板の中心と端から得られた平均値であることに注意してください。 。 CL-ES構造のa-IGZOベースのTFTが V を実現 th − 0.8 V、SS値0.18 V / dec、飽和電子移動度8.05 cm 2 /Vs。 BCE構造のa-IGZOベースのTFTでは、対応する結果は V です。 th + 0.5 V、SS値0.77 V / dec、飽和電子移動度6.03 cm 2 /Vs。 BCE構造と比較して、CL-ES構造は改善されたデバイス性能を示します。ただし、CL-ES構造のa-IGZOベースのTFTデバイスのオン電流特性は、BCE構造のデバイスのオン電流特性よりも低くなっています。これは、TFTチャネル構造がCL-ES構造とBCE構造で異なるためです。一般に、BCE構造のTFTチャネル長は、S / D金属電極間の距離であり、この研究で測定されたチャネル長は5umです[21]。 CL-ES構造では、電極はESLナノマスクの側面で引き伸ばされたa-IGZOナノフィルムと接触しています。したがって、チャネル長は、エッチングストッパーの側面で定義されたa-IGZO間の距離によって決定されますが、電極間の距離によっては決定されません。現在のCL-ES構造デバイスのチャネル長は10umと測定されています。

(オンラインカラー)中央にCL-ESとBCE構造のa-IGZOTFTのI-V特性の比較( a )とエッジ( b )8.5世代のガラス基板

表1に示すように、 I の測定値 on / 私 オフ 比率(〜10 6 、表1を参照)は、通常の値(> 10 7 )の約10分の1です。 )-IGZOベースのTFT。これは、ここで使用している測定器が8.5世代の量産用であるためです。産業機器のサイズが大きいため、これらの測定には長いケーブルが必要です。ケーブルが長いと、測定ノイズが増加しました。以下の信頼性試験では、より小規模な測定機器を使用し、個々のTFTデバイスを測定用の試験片として使用します。このようにして、測定された I on / 私 オフ 比率はすべて上位10 7 (以下を参照)。

CL-ESプロセスは、a-IGZOチャネル層がエッチャント、フォトレジスト、またはストリッパーにさらされるのを防ぐように注意深く設計されています。 CL-ESプロセス、ゲート絶縁体、a-IGZOナノレイヤー、およびESナノレイヤーを生成するプロセス中、各層間インターフェースは、洗浄目的でDI水のみと接触します。したがって、絶縁体層とa-IGZOナノ層の化学的汚染はごくわずかです[25、26]。ただし、a-IGZOチャネルはCu金属に直接さらされるため、BCEプロセスはチャネル層を化学物質にさらすだけでなく、Cuイオン拡散汚染も伴います。これは、CL-ES構造のデバイスでも回避されます。 a-IGZOナノフィルムのチャネル領域は、ESLナノマスクによって十分に保護されています。 CL-ESプロセスでの化学的汚染が少ないと、a-IGZOナノ層と絶縁体層の間の界面でのキャリアトラップ密度が低くなり、優れたSS値が得られる可能性があります。 CL-ESプロセスによるa-IGZOベースのTFTデバイスのこの低い化学的汚染は、工業生産で非常に重要なa-IGZO TFTの均一性と再現性の向上にも役立ちます[27、28]。

図5は、8.5世代の基板上の42の測定ポイントから得られたCL-ES構造とBCE構造のTFTの測定されたI-V特性を示しています。 a-CL-ES構造のIGZOベースのTFTは V th 範囲は0.72Vですが、BCE構造のデバイスの範囲は2.14 Vです(表1)。つまり、CL-ES構造により、デバイス性能の均一性が大幅に向上します。

(オンラインカラー) a CL-ES構造。 b BCE構造のTFTI-V転送特性。 c 42の測定ポイント。 d TFTの写真。すべて8.5世代の基板で測定

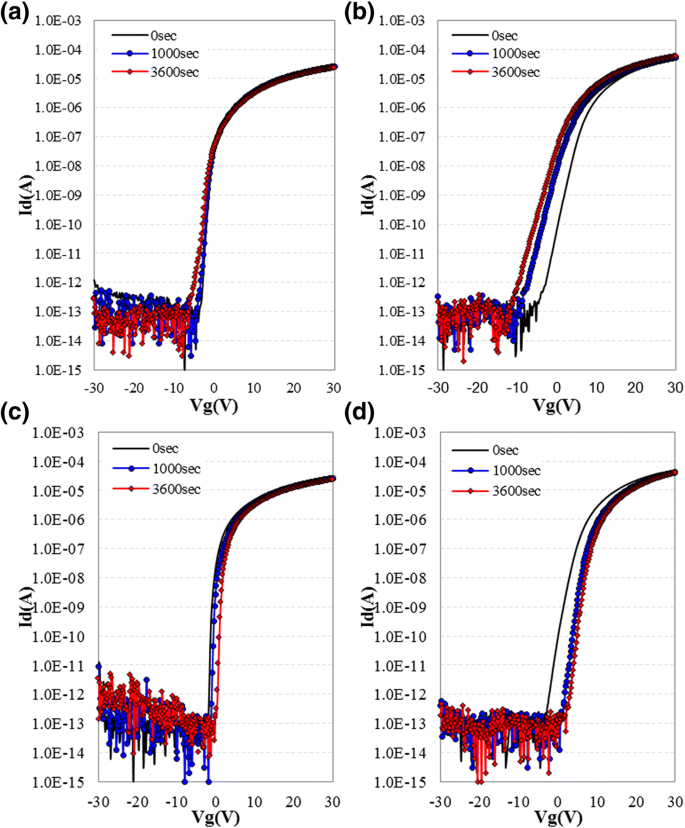

図6a、bは、それぞれNBTISテストで得られたCL-ES構造化デバイスとBCE構造化デバイスのI-V特性シフトを示しています。 NBTISのテスト結果は、表2にまとめられています。表2に記載されているストレス条件下で、 V th CL-ES構造のデバイスとBCE構造のデバイスのシフトはそれぞれ-0.51と-3.88Vです。さらに、CL-ES構造のデバイスのオン電流シフト、オフ電流シフト、およびSS値の変動はすべて、BCE構造のデバイスよりも低くなっています(表2)。これは、CL-ES構造のa-IGZOベースのデバイスがa-IGZOの汚染を効果的に防止し、a-IGZOTFTチャネルのキャリアトラップ密度を低下させるためです。特に、最初の1000秒間の応力の結果を見ると、CL-ES構造のデバイスではSS値の変化は観察されません。この現象は、BCE構造デバイスのSS値の0.16 V / decの増加に匹敵します。これは、CL-ESTFTバックチャネルを構成するa-IGZOナノフィルムの表面にキャリアトラップを形成する可能性のある欠陥サイトを示しています。電気的および照明的ストレスによって追加的に作成されることはありません。これらの結果は、CL-ES構造のデバイスがBCE構造のデバイスよりもはるかに安定していることを完全に証明しています。図6c、dは、PBTSテストから得られたCL-ESおよびBCE構造のTFTのI-V曲線シフトを示しています。詳細なPBTSテスト結果は、表3にまとめられています。CL-ES構造のTFTとBCE構造のTFTの両方で、PBTS評価中にイオン電流が減少しました。これは、 V のシフトが原因です。 th 正の方向に。 PBTS評価中、 V が比較的小さいCL-ES構造のTFTの残留イオン電流比[(最後のイオン/最初のイオン)×100] th 正のシフト(+ 1.94 V)は88.2%のレベルです。 BCE構造のTFTの残留イオン電流比41.3%と比較すると、CL-ES構造のTFTは非常に優れています。これは、アレイ上のゲートドライブ(GOA)回路の設計中の重要な容量の違いを示しています。 NBTISとは異なり、CL-ES構造のTFTのSS値には大きな変動がなく((∆SS 0.06 V / dec)、BCE構造のTFTのように減少します(∆SS − 0.86)。これはおそらく、キャリアは、正のゲートバイアスにより内部空間とゲート絶縁体とa-IGZOナノフィルムの界面に蓄積し、キャリアトラップサイトを早期に満たしてキャリアトラップ現象を低減します。また、しきい値電圧シフト現象は、ゲート絶縁体とa-IGZOナノフィルムの界面付近にキャリア電荷が閉じ込められているCL-ES構造のTFTのしきい値電圧シフトが小さいことは、a-IGZOの界面と内部空間が非常にきれいであることを示しています。結論として、PBTSテストもCL-ESの構造とプロセスがデバイスの信頼性の向上につながることを示唆しています。

(オンラインカラー)CL-ESのI-V伝達特性ドリフト( a 、 c )およびBCE( b 、 d )NBITSから取得したTFT( a 、 b )およびPBTSテスト( c 、 d )

結論

結論として、新しく開発されたCL-ESプロセスは、高度なディスプレイ用に5つのマスクを備えたa-IGZOベースのTFTバックプレーンを製造するために開発に成功しました。 CL-ESプロセスには、BCEプロセスと同じ数のマスクと同様のデバイス領域を維持しながら、エッチングストッパー層構造の利点があります。これにより、従来のエッチングストッパーTFTデバイスでのマスク数と占有領域の増加の問題が克服されます。 。新たに形成されたESLナノマスクとa-IGZOナノ層およびS / D電極ナノ層の同時エッチングにより、大面積ディスプレイ用のデバイスの高い均一性と安定性が可能になります。電気的性能に関しては、CL-ES構造のa-IGZOベースのTFTのデバイス性能の再現性と信頼性は、BCE構造のデバイスよりもはるかに優れています。 a-IGZOベースのTFTデバイスには V があります th 0.72 Vの8.5世代ガラス基板上の42の測定ポイントTFTにわたる分布、8.05 cm 2 の飽和電子移動度 / V s、SS値0.18 V / dec。 NBTISとPBTSから得られた信頼性評価結果によると、 V th CL-ES a-IGZOベースのTFTのストレス前後の変動は、3600秒のストレス後それぞれ-0.51Vと1.94Vです。 SS値の変動は0.33と0.06V / decです。したがって、技術的および経済的な障害を克服することにより、提示されたCL-ES技術は、次世代の高解像度および大型パネルディスプレイ製品への道を開くでしょう。

略語

- a-IGZO:

-

アモルファスインジウム-ガリウム-亜鉛-酸化物

- AM-LCD:

-

アクティブマトリックス液晶ディスプレイ

- BCE:

-

バックチャネルエッチング

- ESL:

-

エッチングストッパー層

- GOA:

-

アレイのゲートドライブ

- NBTIS:

-

負のバイアス温度照明ストレス

- PBTS:

-

正のバイアス温度応力

- SiNx:

-

窒化ケイ素

- SiOx:

-

酸化ケイ素

- SS:

-

サブスレッショルドスイング

- TFT:

-

薄膜トランジスタ

- TN LCD:

-

ねじれネマティック液晶ディスプレイ

ナノマテリアル

- 染色プロセスでの水を使わない技術の使用

- Picoを使用したハードウェアブート選択スイッチ

- 設備総合効率の使用

- 資産パフォーマンスを管理するための戦略

- 資産パフォーマンス管理を使用して資産価値を最大化する

- スリーステートエレクトロクロミックデバイスのディップコーティングプロセスエンジニアリングと性能最適化

- ゾル-ゲル法によるナノ構造シリカ/金-セルロース結合アミノ-POSSハイブリッド複合材料とその特性

- 溶液由来のZnOを使用したテンプレートプロセスによるナノシェルベースの3D周期構造の製造

- Ptナノ粒子表面プラズモンとのカップリングによるMgZnO金属-半導体-金属光検出器の大幅な強化

- 3D プリンタを使用して製造プロセスを改善する - ビデオ

- パッドでVIAを使用する利点