2DEGチャネルとパターン化基板を備えた新しいGaNナノピラー垂直電界効果トランジスタ(FET)のバリガの性能指数(BFOM)強化について

要約

オン状態抵抗( R )を低減するための2DEGを備えた新しいエンハンスメントモード垂直GaN電界効果トランジスタ(FET) オン )およびブレークダウン電圧(BV)を高めるための基板パターン(SP)がこの作業で提案されています。 SPの幅と高さを慎重に設計することにより、p-GaNキャップの下の高濃度電界(電界)を、 R に劇的な影響を与えることなく分離することができました。 オン 、強化されたバリガの性能指数(BFOM、BV 2 / R オン )。実験的に較正されたATLASシミュレーションによって検証された、長さ700 nm、幅4.6μmのSPを備えた提案されたデバイスは、パターン化された基板のないFETと比較して6倍高いBFOMを備えています。さらに、提案されたピラーデバイスと内部のSPはナノスケールの領域を占めるだけであり、そのようなデバイスの高密度統合を可能にし、将来の電力アプリケーションでその高い可能性をもたらします。

背景

現在、ZnO、In 2 などのワイドバンドギャップ半導体 O 3 、SiC、窒化ガリウム(GaN)が注目されています[1,2,3,4,5]。一方、電子特性を考慮すると、ラテラルAlGaN / GaN高電子移動度トランジスタ(HEMT)は、絶縁破壊電圧(BV)が高く、より強い熱安定性。 p型キャップ[6、7]、フッ素イオン注入[8、9]、薄いバリア[10、11]、ダブルチャネル[5、12]、フィールド結合ゲート[13]などの多くの取り組み。 、ドライバ回路を簡素化するために望まれるエンハンスメント型HEMTの実現に向けて作られました。

ただし、これらのテクノロジーは、しきい値電圧の均一性の低さ、垂直チップ領域の浪費、電流の崩壊、バリガの性能指数(BFOM)の制限など、多くの手ごわい課題に直面しています。特に、ドリフト長とBVの矛盾は、デバイスのスケールダウンに悪影響を及ぼします[14、15]。つまり、デバイスが小さいほどBVが低くなり、電界分布を最適化してBFOMを促進する接合端子を採用することが難しくなります。この目的のために、バックバリア[16]、埋め込み接合[17]、量子井戸フィールドプレート[18]、および電界プレートの特徴を示す側面HEMTに挿入される他の構造が、を利用してBVを強化するために提案されています。チップの垂直領域。

一方、GaNの優れた性質により、バルクGaN垂直電界効果トランジスタ(VFET)は、エンハンスメント型機能の実現が容易であり、垂直領域を最大限に活用することにより、ますます注目を集めています[19 、20、21、22]。多くの新しい構造が実験またはシミュレーションによって提示され、BVを傾斜させ、同時にオン状態の抵抗( R )を低減します。 オン )[23,24,25]。ただし、GaNでスーパージャンクション(SJ)を製造することの難しさは言うまでもなく、高移動度の2次元電子ガス(2DEG)がないため、 R が高くなります。 オン [26]、これはそのようなデバイスでのBFOMの最適化を妨げます。

この作業では、 R を低減するための2DEGを備えた新しいエンハンスメントモード垂直GaNFET オン また、BVを強化するための基板パターン(SP)が提案されており、2DEGチャネルとSPの組み合わせにより、低いオン状態抵抗と高いBVの間の矛盾のバランスが効果的に保たれます。さらに、提案されたデバイスピラーと内部のSPは、ナノスケールの領域を占めるだけであり、そのようなデバイスの高密度統合を可能にします。 ATLASで構築された数値シミュレーションによって検証された、提案されたデバイスは、パターン化された基板のない同じ電界効果トランジスタ(FET)と比較して、より高いBFOMを特徴とし、将来の電力アプリケーションでその高い可能性をもたらします。

メソッド

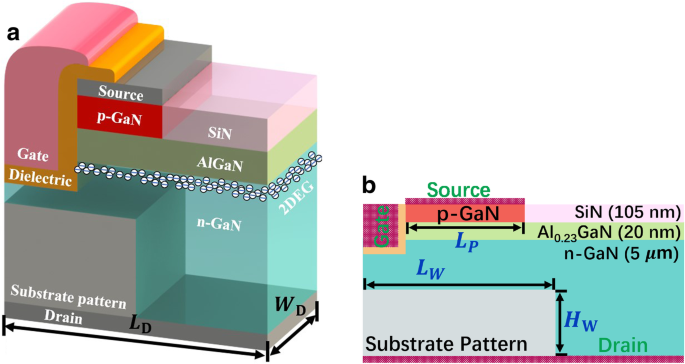

提案されたデバイスは、通常のAl 0.23 で生成されます。 図1aに示すように、ドレイン電極として機能する高濃度のn型基板を備えたGaN / GaNウェーハ。ここで、窒化ケイ素(SiN)、AlGaN、およびGaNの層の厚さは105 nm、20 nm、および5 µmです。 、 それぞれ。 2×10 16 のn型GaN cm -3 ドーピング n D 2×10 17 のp型GaNキャップ cm -3 ドーピング n A はそれぞれバッファと複合チャネルとして設定されます[27、28]。ゲートの横にあるチャネルのもう1つのコンポーネントは、図1bに示すように、2DEGを誘導するために導入された薄いAlGaN層です。酸化アルミニウム(Al 2 )で作られたSP O 3 )たとえば、この論文では、基板上で成長します。

回路図 a 3Dピラー構造と b 提案されたSP-VFETのラベル付き幾何学的パラメータの断面図

したがって、デバイス全体は、標準的なプロセスによって連続的に製造することができます:(1)伝導基板と統合SP層のエピタキシャル堆積、(2)SPパターンの部分エッチング、(3)n-の堆積と研磨GaNバッファ、(4)AlGaNバリアとp-GaNキャップの堆積、および(5)電極の製造とパッシベーション。

埋め込まれたATLASシミュレータは、p-GaNキャップを備えたエンハンスメントタイプのHEMTからの実験データによって較正されます[29、30]。デバイスのキャリブレーションされた仕様とその他の仕様を表1に示します。その他の構成は、以前の作業[31]で見つけることができます。 SP / GaN界面に配置された界面トラップのタイプと密度は、静電容量ベースの実験測定[32、33、34]を参照しています。 AlGaN / GaN表面の分極電荷は、対応する単純な2次フィッティング方程式[35]に従って確認されます。

<図>物理メカニズム

オン状態では、2-DEGチャネルとSPのないデバイスと比較して、基板パターンを備えた提案された垂直電界効果トランジスタ(SP-VFET)は、2-DEGと狭い垂直電流チャネルによる高導電性パスを備えています。これにより、図2に示すように、コンダクタンスが縮小します。詳細には、AlGaN / GaN界面に集中した高密度2DEGのおかげで、電流の横方向の経路を維持でき、デバイス全体のコンダクタンスを部分的に補償します。対照的に、2DEGチャネルのないSP-VFETデバイスの現在の輸送能力は劇的に影響を受けます。

a の順方向電流の概略図 SPのないデバイス、 b SPが短い提案されたSP-VFET、および c 長いSP

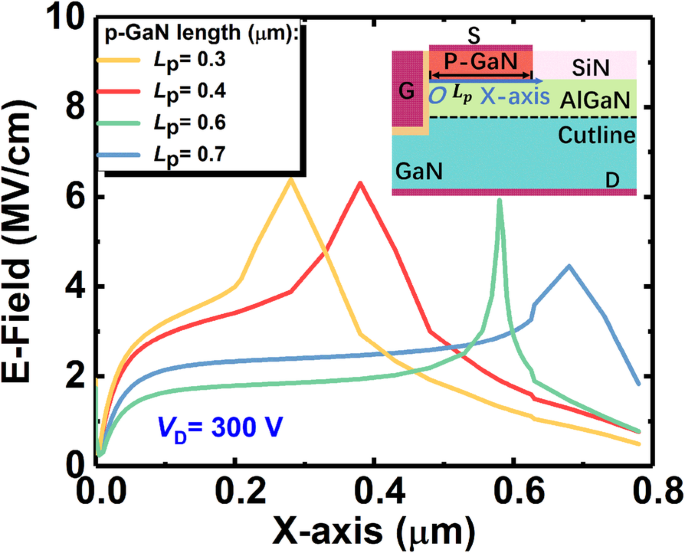

p-GaNキャップの長さは、p-GaNがデバイス表面全体をほぼ覆う700 nmより長くなるまで、電界(電界)の濃度に劇的な影響を与えることはありません。図3に示すように、AlGaN / GaN界面に沿った電界分布は、p-GaNの右隅の周りにピークを持っています。ピークの位置は、p-GaNの長さの変化に伴ってシフトしますが、同じ大きさを維持します。 p-GaNキャップが600nmより長い場合、ピーク値のわずかな違いが図3に見られます。これは、長いp-GaNキャップがデバイス内の電界全体を平坦化し、これによりデバイスの抵抗が拡大するためです。 2DEGの枯渇に。

異なるp-GaN長さのAlGaN / GaNヘテロ接合に沿ったSPなしのデバイスの電界分布

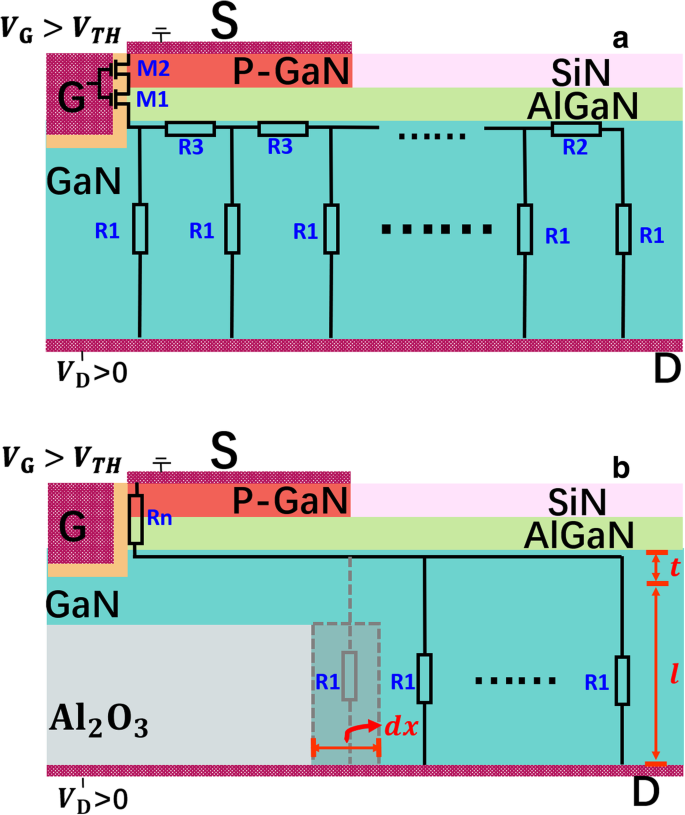

同時に導入されたp-GaN、2-DEG、およびSPの影響を説明するために、図4aに概略的に示すように、オン状態の伝導モデルを構築できます。 M 1 および M 2 は、それぞれp-GaNとAlGaNで形成された導電チャネルを備えたMISのようなトランジスタです。 R 1 バルクGaNの垂直抵抗の微小部分を表します。 R 2 および R 3 それぞれ部分的に枯渇している場合とない場合の2-DEGチャネルの微小抵抗部分を表します。抵抗の法則によれば、 R 1 、 R 2 、および R 3 として取得できます

$$ {R} _1 =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {dx \ bullet {W} _D} $$$$ {R} _2 =\ frac {1} {n_2 q \ mu} \ bullet \ frac {dx} {t \ bullet {W} _D} $$$$ {R} _3 =\ frac {1} {n_3 q \ mu} \ bullet \ frac {dx} {t \箇条書き{W} _D} $$

ここで n 1 、 n 2 、および n 3 GaN、非枯渇2-DEG、および枯渇2-DEGの電気濃度をそれぞれ表します。 q は電子の電荷であり、μ GaNにおける電子の移動度です。 l は垂直導電経路の長さであり、 dx 地平線の微小長です。 W D デバイスの幅です。および t は2-DEGの厚さです。便宜上、 t 10nmに設定されています[7]。 p-GaN n の下での枯渇した2-DEGの濃度 3 枯渇していない濃度に等しい n 1 枯渇したp-GaNの負電荷の合計を差し引いた[31]。 $$ {n} _3 ={n} _2- {n} _A {x} _D $$

a の概略図 SP b なしで提案されたオンステートモデル SPを使用したオン状態抵抗ネットワークモデル

p-GaNキャップは完全に消耗していると見なすことができるため、 x D p-GaNの厚さである105nmに相当します。 R との比較 1 、 R 2 および R 3 R よりはるかに低い 1 、電子濃度が高く、導電経路が短いため。したがって、2-DEGチャネルの抵抗は無視できます。また、ドレイン電圧が小さく、MIS様トランジスタ M 1 および M 2 不飽和モデルで動作し、 M のオン状態抵抗 1 および M 2 無視できる一定の抵抗と見なすことができます R n 。計算を簡単にするために、垂直電流経路コンダクタンスの分析形式 G v 垂直電流経路のは次のように取得できます

$$ {G} _v ={\ int} _0 ^ {L_D} \ frac {1} {R_1} ={\ int} _0 ^ {L_D} {n} _1 q \ mu \ bullet \ frac {dx \ bullet { W} _D} {l} $$ここで L D はデバイスの長さです。

したがって、オン状態の抵抗 R オン 取得できます。 $$ {R} _ {on} =\ frac {1} {G_v} + {R} _n =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {L_D \ bullet {W} _D } + {R} _n $$

SPが存在する場合、図4bに示すように、垂直方向の導電経路が部分的にブロックされています。したがって、垂直電流経路のコンダクタンスは次のように表すことができます

$$ {G} _v ={\ int} _ {L_W} ^ {L _ {\ mathrm {D}}} \ frac {1} {R_1} ={\ int} _ {L_W} ^ {L_D} {n} _1 q \ mu \ bullet \ frac {dx \ bullet {W} _D} {l} $$ここで L W SPの長さです。

したがって、対応する R オン

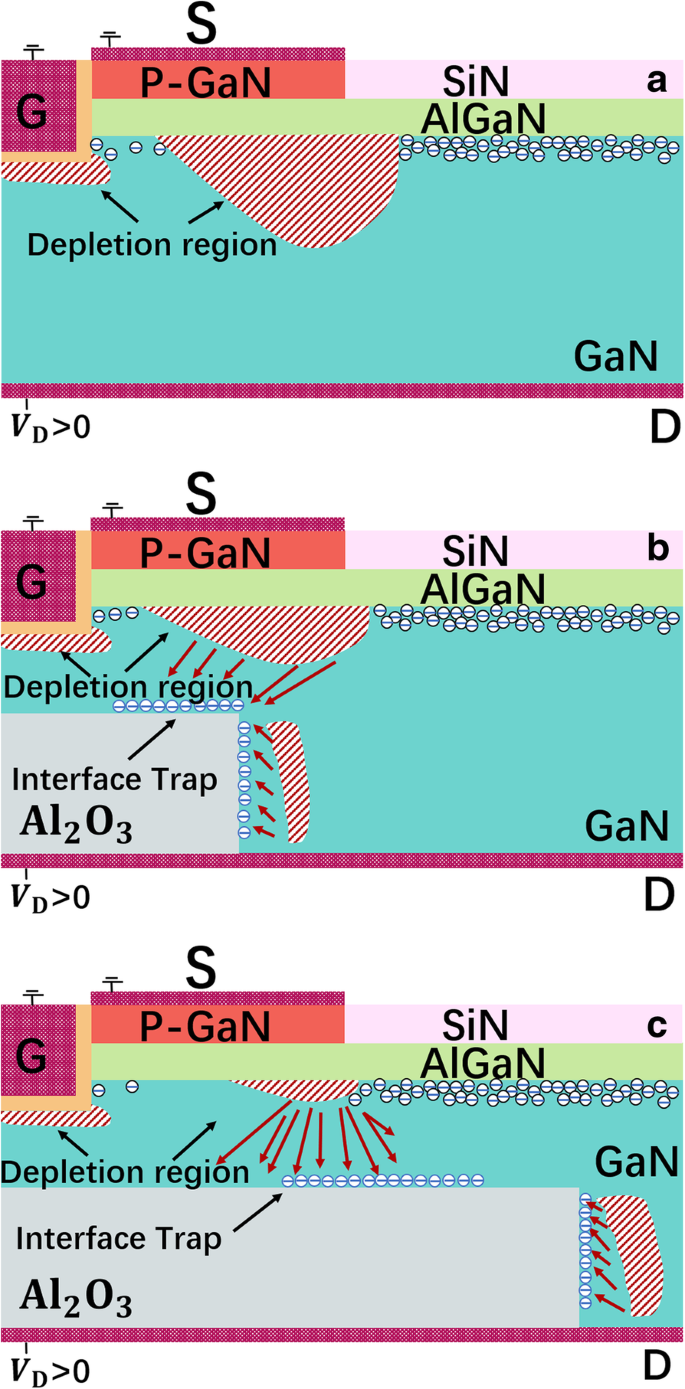

として表すことができます $$ {R} _ {on} =\ frac {1} {G_v} + {R} _n =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {\ left({L} _D -{L} _W \ right)\ bullet {W} _D} + {R} _n $$オフ状態では、コンデンサのような機能と負に帯電した界面トラップにより、SPはp-GaNキャップの下の電界を効果的に再分配し、図に示すように、より広いバンドギャップを所有するSPの周囲に電界集中をもたらします。図5.このような電界の再分布は、p-GaNとゲートの周りに現れる空乏領域を縮小し、それによってp-GaNキャップとゲートの周りの高電界集中を緩和します。これによりSP-VFETのBVが向上します。著しく。一方、前述のように、SPはデバイスのコンダクタンスに影響を与え、SPによって導入された負電荷がゲート付近の位置エネルギーの増加につながり、ゲート付近の2-DEGの減少を説明します。その結果、SPの長さと高さを変えることで変動するBFOMが達成されます。

a の電界と空乏領域の概略分布 SPのないデバイス、 b SPが短い提案されたSP-VFET、および c SPが長い提案されたSP-VFET

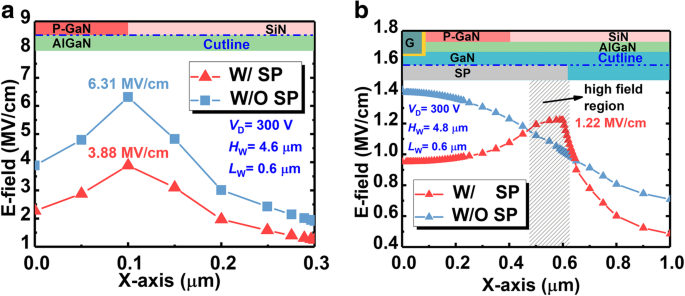

つまり、図6a、bに示すように、SPはp-GaNコーナー周辺の電界のピークを低減すると同時に、SP全体に集中する電界を引き付けることができます。ただし、SPのより高い臨界電界のおかげで、そのような電界集中はデバイスを破壊せず、それによってSP-VFETははるかに高いBVを示します。

a の界面に沿った提案されたSP-VFETの電界分布 p-GaN / AlGaNおよび b GaN / SP

結果と考察

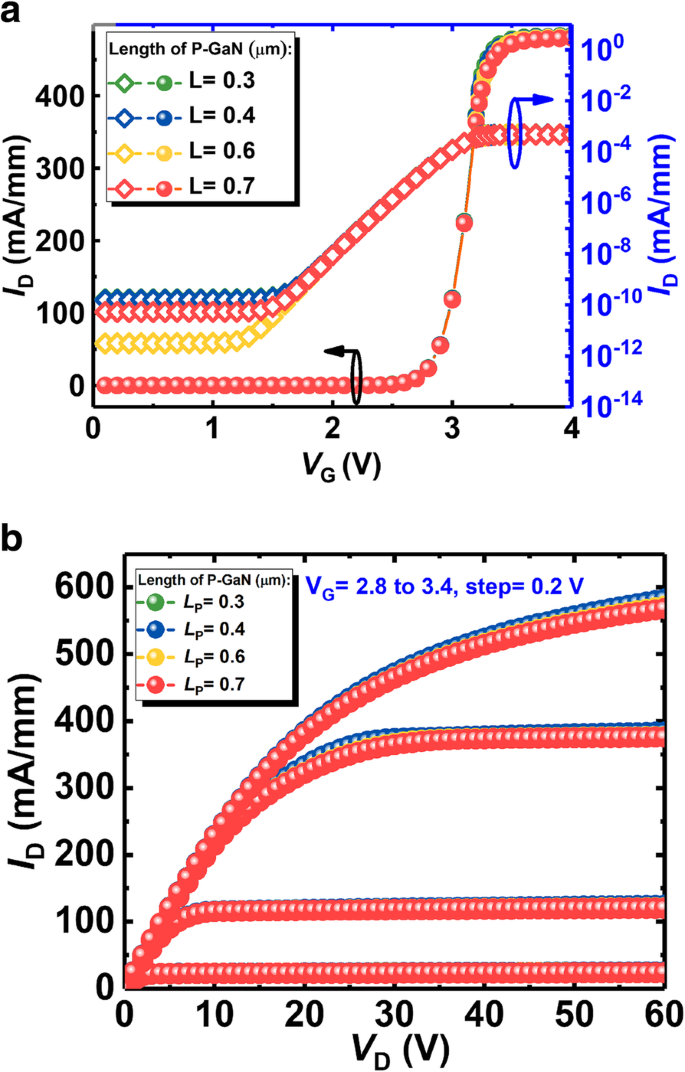

図7a、bは、それぞれSPなしの提案されたデバイスの伝達曲線と出力曲線を示しています。 p-GaNキャップの長さが異なる場合、これらの曲線はしきい値以下とターンオンの両方の領域で互いに重なり合い、p-GaNキャップの長さがSPなしのデバイスのコンダクタンスに影響を与えないことを示唆しています。言い換えると、p-GaNキャップは2-DEGを部分的に使い果たし、これにより2-DEGチャネルの抵抗に影響を与えますが、残った2-DEGは依然として大きな濃度を持っています n 3 これは、枯渇していない濃度に近似します n 2 、これは、p-GaNキャップのp型濃度を最適化することによって実現されます。さらに、前に分析したように、2-DEGチャネルの抵抗は、垂直経路のn-GaNの抵抗と比較してかなり小さいです。したがって、図7a、bでは、伝達曲線が互いに重なり合っています。ただし、高濃度の電界からゲートを保護するために、このような混雑はゲートに隣接してはなりません。つまり、p-GaNの長さが短すぎないようにする必要があります。したがって、特に明記しない限り、私たちの研究におけるp-GaNの最小長は400nmです。

a 伝達曲線と b p-GaNキャップの長さが異なる場合のSPなしのデバイスの出力曲線

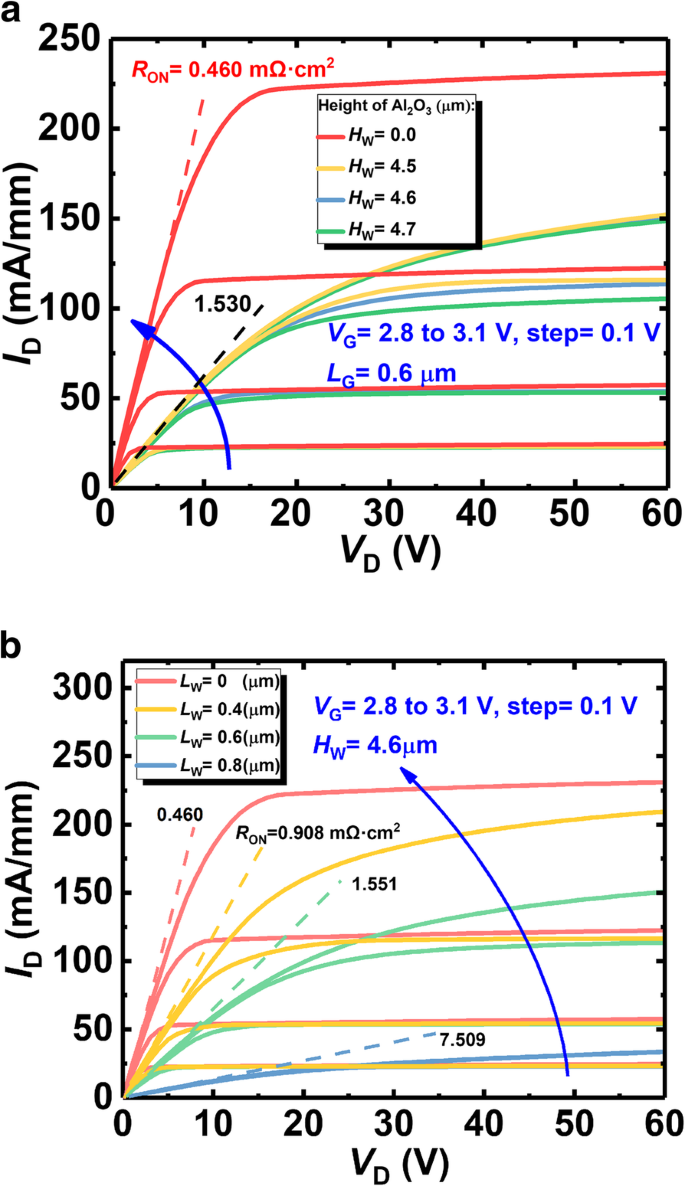

図8は、提案されたSP-VFETとSPなしのVFETの出力特性を示しています。 SPは垂直伝導チャネルを狭くすることによってデバイスの抵抗を課していることがわかります。詳細には、オン状態の抵抗は、高さが4.7 µm未満の場合、SPの高さに依存しませんが、狭い垂直電流経路がコンダクタンスを縮小するメカニズムに一致するSPの長さに大きく依存します。前者の独立性は、2DEGが、適度な高さの範囲内でSPによって弱められない主要な横方向伝導チャネルであるためです。ただし、SPが2-DEGチャネルに隣接している場合、SPの周囲に導入された負電荷によってエネルギー帯域がレベルアップし、2-DEG濃度が劇的に低下します。その結果、2-DEGの抵抗が増加し、合計オン状態抵抗 R オン それに応じて増加します。その上、後の依存関係は、前述のように垂直チャネルの著しくブーストされた抵抗に由来します。さらに、高いSPによって引き起こされる2-DEGの格子欠陥は、SPの高さを制限することに注意する必要があります。

a を変化させた提案されたSP-VFETの出力曲線 SP幅と b SPなしのデバイスと比較したSPの長さ

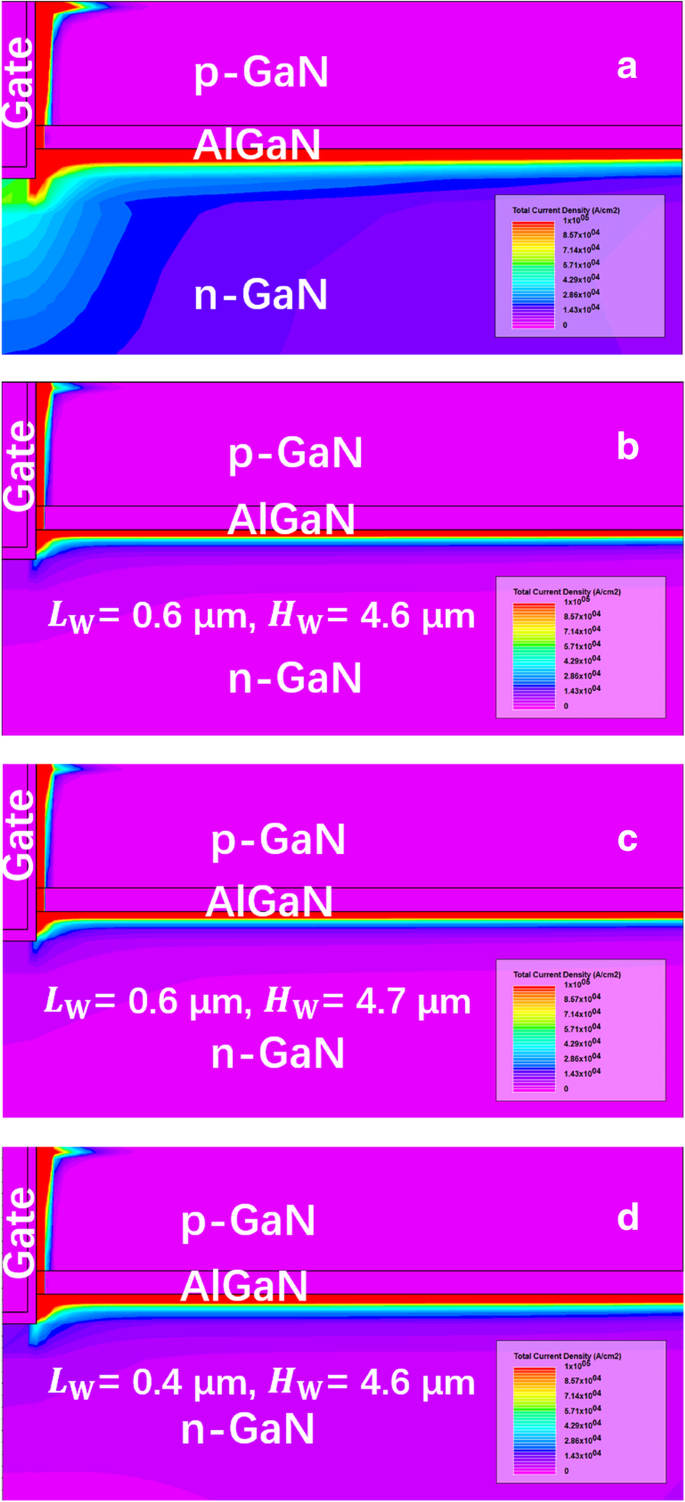

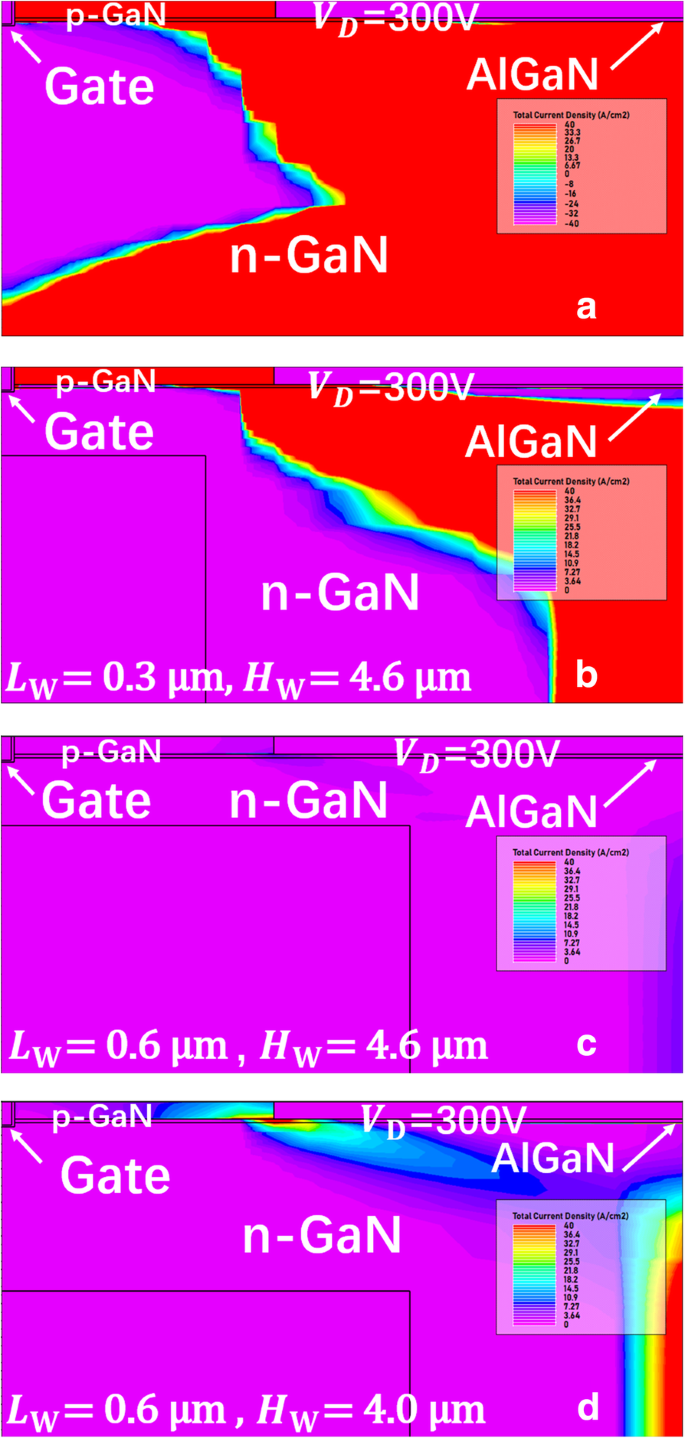

図9は、SPがある場合とない場合のVFETデバイスのゲート周辺の電流密度分布の詳細を示しています。SPなしのVFETは、図8aと一致する、より高い電流輸送能力を備えています。逆に、SP-VFETは、垂直チャネルを狭くすることによって電流伝導を縮小します。一方、詳細な図は、横方向チャネルの電流が2DEGによって輸送されることを明確に示しており、合計電流密度はSPの高さの増加に伴ってわずかに変化します。これは、メカニズムのセクションでも示されています。結果は、横方向のチャネル抵抗が中程度の高さのSPによって特に課されていないことを示しています。

a の電流密度 SPおよび b のないデバイス – d 異なるSP幾何学的パラメータを持つ提案されたSP-VFET

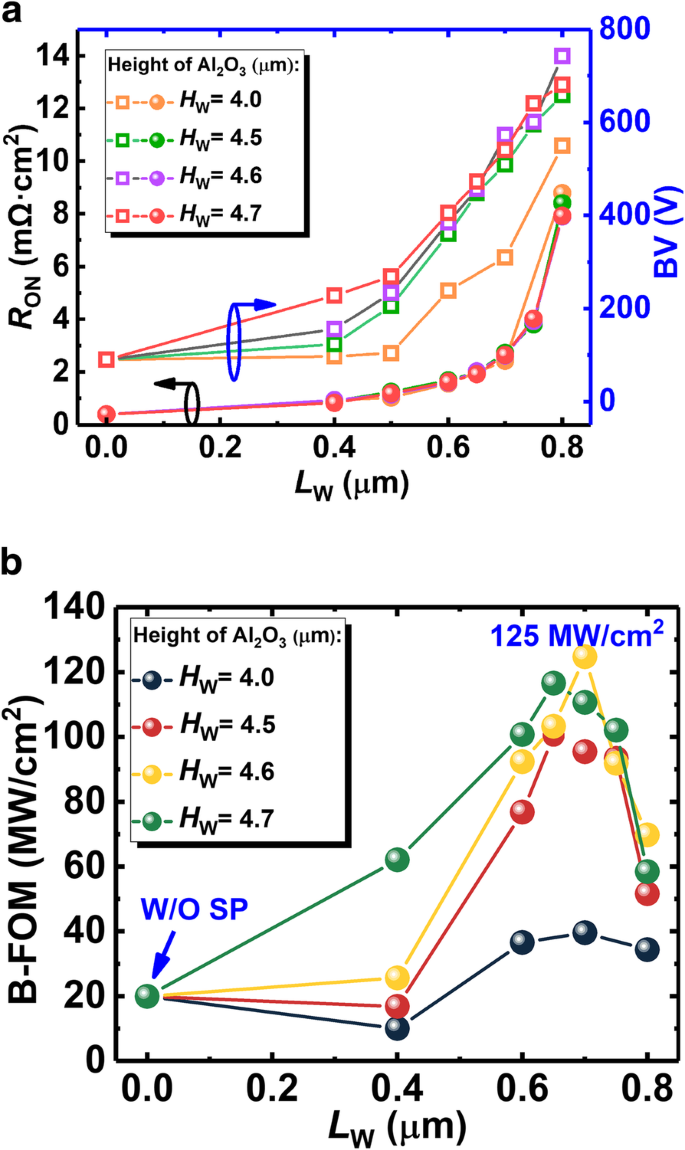

図10aは、抽出されたオン状態抵抗と対応するBVを示しています。 SP-VFETの抵抗は、SPが長くなると増加します。特に、抵抗対SPの長さの曲線は双曲線の傾向を示し、曲線の勾配はSPの長さが長くなるにつれて増加します。前に分析したように、 R オン SPの長さによって異なります L W シミュレーション結果と一致する双曲線関数の形式で。さらに、SPの高さが異なる抵抗の曲線は、高さが4.7 µm未満であるため互いに重なり合っており、前述のように、2-DEGチャネルが主な横方向の導電経路であり、2-DEGチャネルは影響を受けないことを示しています。

a 抽出されたオン状態抵抗、BV、および b 異なるSPの長さと幅で提案されたSP-VFETの対応するBFOM

図10bは、SP-VFETの計算されたBFOMを示しています。 BVの増加率とオン状態の抵抗が異なるため、すべてのデバイスのBFOMは最初に増加し、次にSPの長さが400nmを超えると低下します。 125 MW / cm 2 のピークBFOM 長さが700nmに達し、高さが4.6 µmに達すると達成されます。 SPのないデバイスと比較して、提案されたSP-VFETは、BFOMの点で6倍以上優れています。

この改善は、SPの周りの負に帯電した界面トラップのおかげで、p-GaNの下の高電界の抑制を所有して達成されます。 SPの界面にトラップされた負電荷とp-GaNの周りの空乏領域との間に発生する相互作用は、主にトラップされた電荷に向かって電界の新しい分布を形成します。ガウスの法則によれば、電束は囲まれた電荷によって制限されます。したがって、導入された電界は他の場所への電束に影響を与えます。空乏領域の負電荷がp-GaNの周りの混雑した電界の主な原因であるため、トラップされた電荷によって導入された電界は、p-GaNの周囲の混雑した電界を抑制する役割を果たします。 BVが強化されています。具体的には、SPの長さが400 nm未満の場合、SPによって導入される負電荷は空乏領域から遠く離れています。したがって、空乏領域とトラップされた負電荷の間に形成された電界は小さすぎて、p-GaN下の混雑した電界に影響を与える役割を果たしません。その結果、デバイスのBVはわずかに増加します。ただし、SPの長さが400 nmを超えると、SPの境界面にトラップされた負電荷が多くなり、空乏領域とトラップされた負電荷の間の距離が短くなるため、空乏領域とトラップされた負電荷の間の電界は次のようになります。強化され、BVの成長につながります。

さらに、SPによって導入された負電荷のために、SP周辺の領域が大幅に消耗します。また、図11に示すように、SPが長くなると、空乏領域がデバイスのエッジに押し付けられるため、垂直リーク電流パスの幅が狭くなり、リーク電流もブロックされ、結果としてBVが向上します。したがって、SPの長さが長くなるとBVは著しく上昇します。

a の漏れ電流密度 SPおよび b のないデバイス – d 異なるSP幾何学的パラメータを持つ提案されたSP-VFET

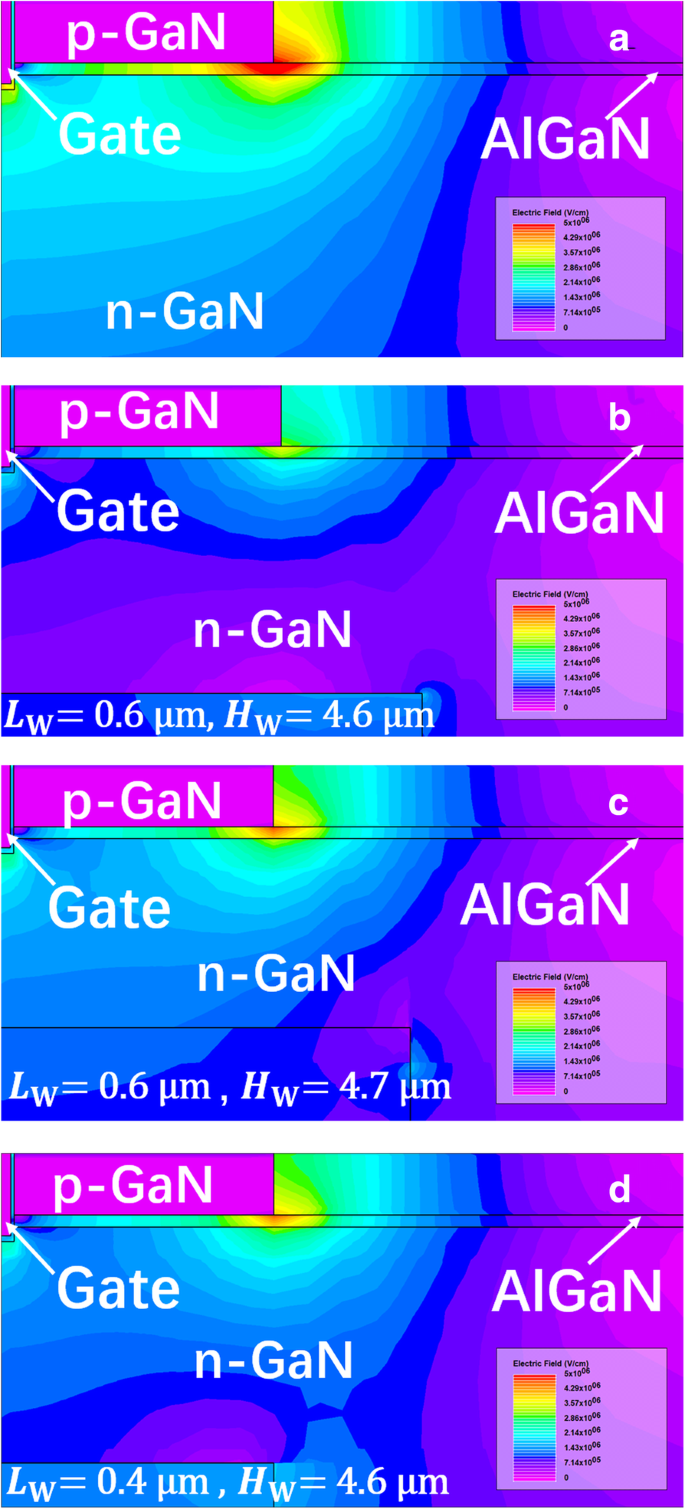

図12は、ドレイン電圧が300 Vの場合のSP-VFETでシミュレートされた電界分布を示しています。ここで、SPは他の新しい電界集中点を誘導しているようです。つまり、p-GaNの下のピーク電界領域が抑制されています。 。 SPの高さが異なるデバイスの電界分布と比較して、SPの長さが長くなると、電界の凝集が抑制され、その結果、BVがより効率的に向上します。

VFETのゲート周辺の電界分布 a withまたは b – d ドレイン電圧が300Vの場合、SPなし

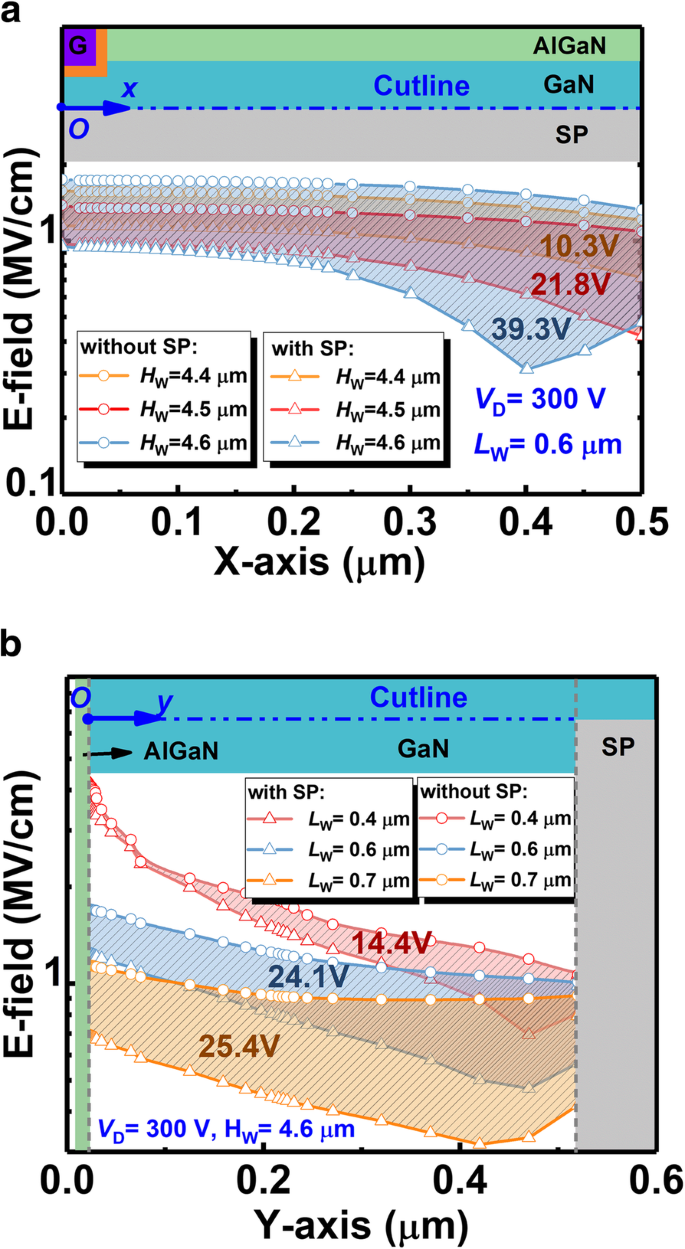

このような平坦化された電界は、図13でも明示的に観察できます。この図では、SPの水平エッジと垂直エッジに沿った電界分布がプロットされています(カットラインを参照)。ポリクローム図12に示されているように、図13では、SPが高くなるほど、p-GaNの下の電界を再構築し、電界を引き付けてSP全体に集中させるのにますます効果的な役割を果たすことがわかります。縁。この再分布は、脆弱なp-GaNの周りの電界を打ち消します。したがって、デバイスのBVが強化され、提案されたSP-VFETのB-FOMが向上します。

電界分布 a 水平方向および b SP-VFETのSPエッジのカットラインに沿って垂直に抽出

結論

本研究では、BFOMを改善するための2DEGチャネルと基板パターンを備えた新しいエンハンスメント型GaN垂直FET(SP-VFET)を提案し、調査します。 ATLASで実装された実験的に較正されたシミュレーションによって検証されたのは、p-GaNの下の電界ピークを緩和すると同時に、より高い臨界電界を所有するSP全体に新しい電界集中を引き付けるSPです。その結果、提案されたSP-VFETのBVは、2DEG補償により、適度に増加するオン状態抵抗でブーストされます。したがって、SPの長さと高さがそれぞれ700 nmと4.6μmの場合、SP-VFETのBFOMはSPのないデバイスのBFOMよりも6倍向上し、高密度電力で提案されたSP-VFETの有望な可能性をもたらします。統合。

略語

- n A :

-

p型GaNのドーピング濃度

- n D :

-

n型GaNのドーピング濃度

- 2DEG:

-

二次元電子ガス

- Al 0.23 GaN:

-

アルミニウムのモル分率が0.23のアルミニウムガリウムナイトライド

- Al 2 O 3 :

-

酸化アルミニウム

- BFOM:

-

バリガの性能指数

- D SP :

-

基板パターンの界面トラップ密度

- Eフィールド:

-

電界

- E T :

-

伝導帯と界面トラップのエネルギー準位の違い

- FET:

-

電界効果トランジスタ

- GaN:

-

窒化ガリウム

- HEMT:

-

高電子移動度トランジスタ

- H G :

-

ゲートの高さ

- H W :

-

基板パターンの高さ

- L D :

-

デバイスの長さ

- L G :

-

門の長さ

- L P :

-

p-GaNキャップの長さ

- L W :

-

基板パターンの長さ

- SiN:

-

窒化ケイ素

- SP:

-

基板パターン

- SP-VFET:

-

基板パターンの垂直電界効果トランジスタ

- W D :

-

デバイスの深さ

- σ p :

-

分極電荷

ナノマテリアル

- IoTのある道

- AlGaN / GaNHEMTの表面電位と2DEGに及ぼす表面状態とアルミニウムモル分率の影響

- 垂直電場によるML-GaSの電子的および光学的異方性特性の変調

- MnХFe3−XО4スピネルの構造的および磁気的特性に及ぼす接触非平衡プラズマの影響

- TIPS-ペンタセンベースの有機電界効果トランジスタの移動度と形態に及ぼすその場アニーリング処理の影響

- アップコンバージョン発光を増強するための異なる形態のBaYF5:Er3 +、Yb3 +の制御された合成

- SiナノワイヤFETセンサーの光伝導率、pH感度、ノイズ、およびチャネル長の影響

- 金属および金属酸化物ナノ粒子のグリーン合成と単細胞藻類Chlamydomonasreinhardtiiに対するそれらの効果

- チタニアナノチューブの熱伝導率に及ぼす形態と結晶構造の影響

- 堆積後エッチングを用いたディップドロップ法を使用した周期的ポリスチレンナノスフェアアレイの調製とInGaN / GaNLEDの光抽出効率を改善するその応用

- LSPカップリングの波長と強度に対する基板の影響