ZrO2誘電体を備えた高移動度GepMOSFET:ポストアニーリングの影響

要約

この論文では、ZrO 2 を使用したGep型金属酸化物半導体電界効果トランジスタ(pMOSFET)の電気的性能に対するポストメタルアニーリング(PMA)とポストデポジションアニーリング(PDA)の影響を調査します。 誘電。 PDAのないトランジスタの場合、オン状態電流( I オン )、サブスレッショルドスイング(SS)、および静電容量等価厚さ(CET)の特性は、PMA温度が350から500°Cに上昇するにつれて改善されます。 ZrO 2 の結晶化 より高いPMA温度での誘電体は、ZrO 2 の誘電率の増加に寄与します。 界面状態の密度の減少( D それ )、結果としてCETが低下し、実効正孔移動度が高くなります(μ eff )。 400°CでPDA処理を行ったGepMOSFETは、CETが低く、SSが急勾配ですが、μが低いことが実証されています。 eff PDAのないデバイスと比較して。

背景

ゲルマニウム(Ge)は、Siよりもはるかに高い正孔移動度を提供するため、高度なCMOSの魅力的なpチャネル材料の1つと見なされています[1,2,3]。高品質のゲート誘電体とGe表面の効果的なパッシベーションは、優れた効果的なキャリア移動度(μ)を実現するための鍵です。 eff )およびGeトランジスタの高い駆動電流[4,5,6,7]。 HfO 2 などのいくつかのhigh-κ材料 [8]、ZrO 2 [7、9]、La 2 O 3 [10]、およびY 2 O 3 [11]は、Ge p型金属酸化物半導体電界効果トランジスタ(pMOSFET)の代替ゲート誘電体として研究されており、サブ1 nmに向けた静電容量等価厚(CET)スケーラビリティを実現しています。これらの中で、ZrO 2 誘電体は、Hfベースのものと比較してはるかに高いκ値[12、13]およびより良い界面品質[14]のために最も注目されています。 ZrO 2 の結晶化が広く報告されています Ge pMOSFETの電気的性能をさらに向上させることができます。たとえば、CETを減らし、μを上げることができます。 eff [15、16]。ただし、ZrO 2 のプロセスステップの影響に関する研究は不足しています。 Geトランジスタのデバイス性能の結晶化。

この論文では、ZrO 2 を使用したGepMOSFETの電気的性能に対するポストメタルアニーリング(PMA)とポストデポジションアニーリング(PDA)の影響を調査します。 誘電。大幅に改善されたμ eff より高いPMA温度のデバイスでCETの低減を実現できます。

メソッド

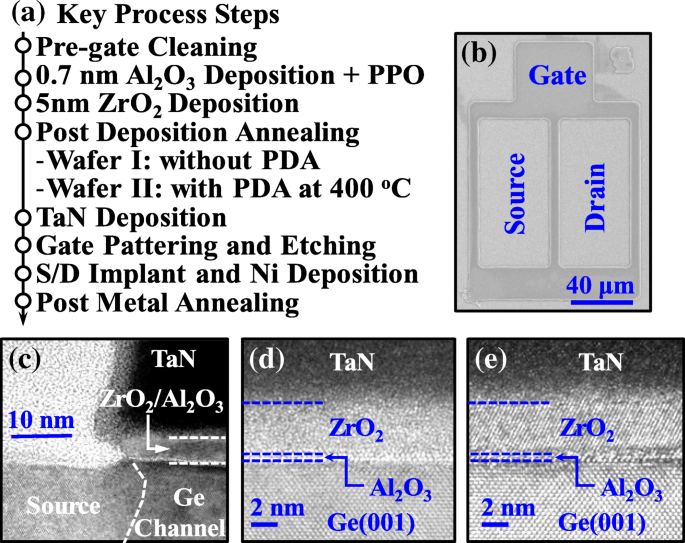

ZrO 2 を使用してGepMOSFETを製造するための主要なプロセスステップ 誘電体を図1aに示します。 Ge pMOSFETは、抵抗率0.088–0.14Ω∙cmのn型Ge(001)ウェーハ上に製造されました。希釈したHF(1:50)溶液での化学洗浄とDI水でのすすぎを数サイクル行った後。 Geウェーハを原子層堆積(ALD)チャンバーにロードしました。 Ge表面は、オゾン後酸化(OPO)、つまり極薄のAl 2 によって不動態化されました。 O 3 層を300°Cで堆積させた後、その場でのOPOを300°Cで15分間実施しました。その後、厚さ5nmのZrO 2 TDMAZrとH 2 を使用して、同じALDチャンバー内に250°Cで堆積しました。 それぞれZrとOの前駆体としてのO。堆積中、Zr [N(CH 3 ) 2 ] 4 ソースは85°Cに加熱されました。 PDAプロセスは、ラピッドサーマルアニーリングを使用して、400°Cで60秒間サンプルに対して実行されました。 PDAのあるサンプルとないサンプルは、それぞれウェーハIIとIで示されました。次に、100nmの厚さのTaNゲート電極を反応性スパッタリングによって堆積させた。ゲートのパターニングとエッチングの後、ソース/ドレイン(S / D)領域がBF 2 によって形成されました。 + 30keVのエネルギーと1×10 15 の線量での注入 cm −2 。 15ナノメートルのニッケルS / D接点は、リフトオフプロセスによって形成されました。最後に、350、400、450、および500°Cで30秒間のPMAを実行して、ドーパントの活性化とS / Dメタライゼーションを行いました。

a ZrO 2 を使用してGepMOSFETを製造するための主要なプロセスステップ 誘電。 b 作製したトランジスタのSEM像。 c ゲート領域とS / D領域を示すGepMOSFETのXTEM画像。 d 、 e それぞれ400°Cと500°CでアニールされたウェーハI上のGepMOSFETのゲートスタックのHRTEM画像

図1bは、製造されたGe pMOSFETの走査型電子顕微鏡(SEM)画像を示しています。図1cは、Ge pMOSFETの断面透過型電子顕微鏡(XTEM)画像を示しており、ソース/ドレイン領域、金属ゲート、およびZrO 2 を示しています。 誘電。図1dとeは、ウェーハI上にそれぞれ400°Cと500°CでPMAを備えたGe pMOSFETのゲートスタックの高分解能TEM(HRTEM)画像を示しています。ZrO 2 > 誘電体は完全に結晶化され、500°CでPMAを受けました。 Al 2 の厚さ O 3 界面層は約0.7nmです。

結果と考察

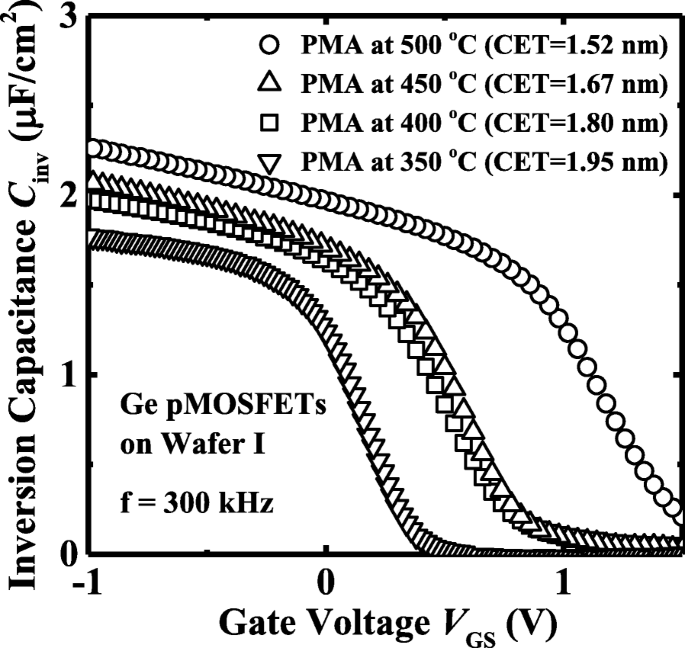

反転容量 C inv 対 V GS ウェーハI上のデバイスについて300kHzの周波数で測定された曲線を図2に示します。CET値は、PMAが350、400、450、それぞれ500°C。 ZrO 2 の結晶化により、より高いPMA温度でより小さなCETが達成されます。 。一般に、アモルファスおよび結晶性ZrO 2 のκ値 それぞれ約20〜23と28〜30です。厚さ5nmの結晶性ZrO 2 〜0.7nmのEOTに貢献します。 C-V のシフト さまざまなPMA温度での曲線は、結晶化によってZrO 2 のバルクトラップの密度が低下するためです。 誘電体。

反転 C inv - V GS 350°C、400°C、450°C、および500°CでのPMAを使用したウェーハI上のGepMOSFETの曲線

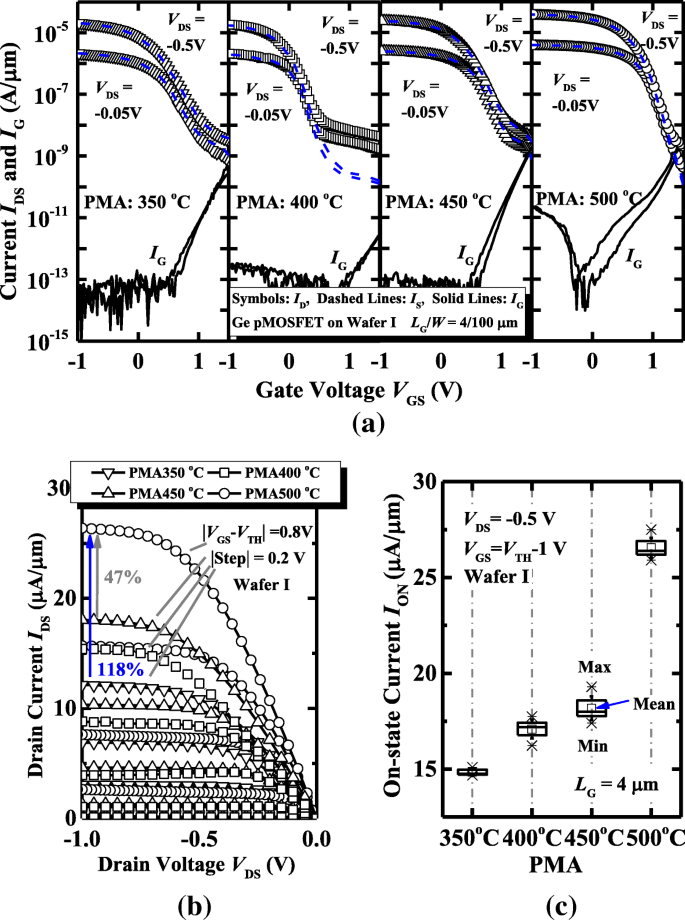

図3aは、測定された伝達特性とゲートリーク電流 I を示しています。 G 異なるPMA温度でのウェーハI上のGepMOSFETの性能。すべてのデバイスのゲート長は L G 4μmのゲート幅 W 100μmの。 Ge pMOSFETは、はるかに低い I を示します G I と比較して DS すべてのPMA温度に対して。 私 オン / 私 オフ 10 4 を超える比率 500°CでPMAを備えたデバイスで達成されます。 私 DS - V DS 異なるゲートオーバードライブで測定されたデバイスの曲線| V GS - V TH |図3bに示します。しきい電圧 V TH V として定義されます GS I で DS の10 -7 A /μm。 500°CでPMAを備えたGeトランジスタは、 V でそれぞれ450°Cと350°Cでアニールされたデバイスと比較して、約47%と118%の駆動電流の改善を実現します。 DS − 1.0Vおよび| V GS - V TH |図3cは、 I の統計プロットを示しています。 オン V で DS − 0.5Vおよび V GS - V TH さまざまなPMA温度のGepMOSFETの場合は-1Vです。このプロットのすべてのトランジスタには L があります G 4μmと W 100μmの。 500°CでPMAを備えたデバイスは、改善された I を示します オン S / D抵抗の低下、CETの低下、およびμの上昇に起因する、PMA温度が低いものと比較して eff 、これについては後で説明します。

a 測定された I D 、私 S 、および I G 対V GS 350、400、450、および500°CでのPMAを使用したウェーハI上のGepMOSFETの曲線。 b 私 DS - V DS さまざまな V で測定された曲線 GS - V TH デバイス用。 c 500°Cでアニールされたデバイスは、より高いオン状態電流 I オン 低温でのPMAを備えたトランジスタと比較して

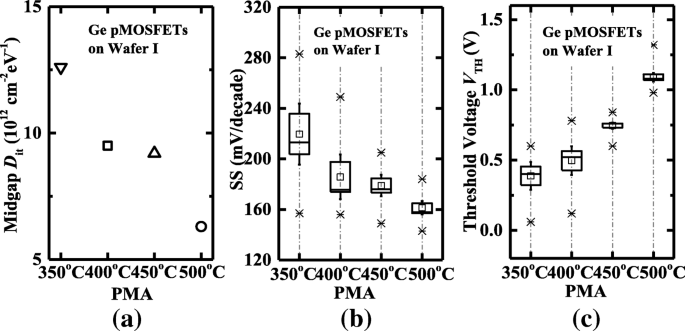

図4は、ミッドギャップ D の統計プロットを示しています。 それ 、SS、および V TH 異なるPMA温度のデバイスの特性。図4aに示すように、最大コンダクタンス法[17]に基づいて、ミッドギャップ D それ 値は1.3×10 13 になるように抽出されます 、9.5×10 12 、9.2×10 12 、および6.3×10 12 cm −2 eV -1 PMAがそれぞれ350、400、450、500°Cのデバイスの場合。図4bは、ミッドギャップ D が小さいため、500°CでアニールされたGe pMOSFETは、低温でアニールされたトランジスタよりもSS特性が向上していることを示しています。 それ およびCET。 D の値 それ また、PMAを備えたGe pMOSFETのSSは、最もよく報告されているGeトランジスタのSSよりもまだ高くなっています。 Al 2 などのOPOパッシベーションモジュールを最適化することで、削減できる可能性があります。 O 3 厚さとオゾンの酸化温度と持続時間。 V TH 正の V にシフトします GS CETと D の低下に起因するPMA温度の上昇に伴い それ 。最高の電気的性能は、500°CでPMAを備えたGepMOSFETで達成されると結論付けられています。

a の比較 ミッドギャップ D それ 、 b SS、および c V TH 350、400、450、および500°CのPMAを備えたウェーハI上のGepMOSFETの場合

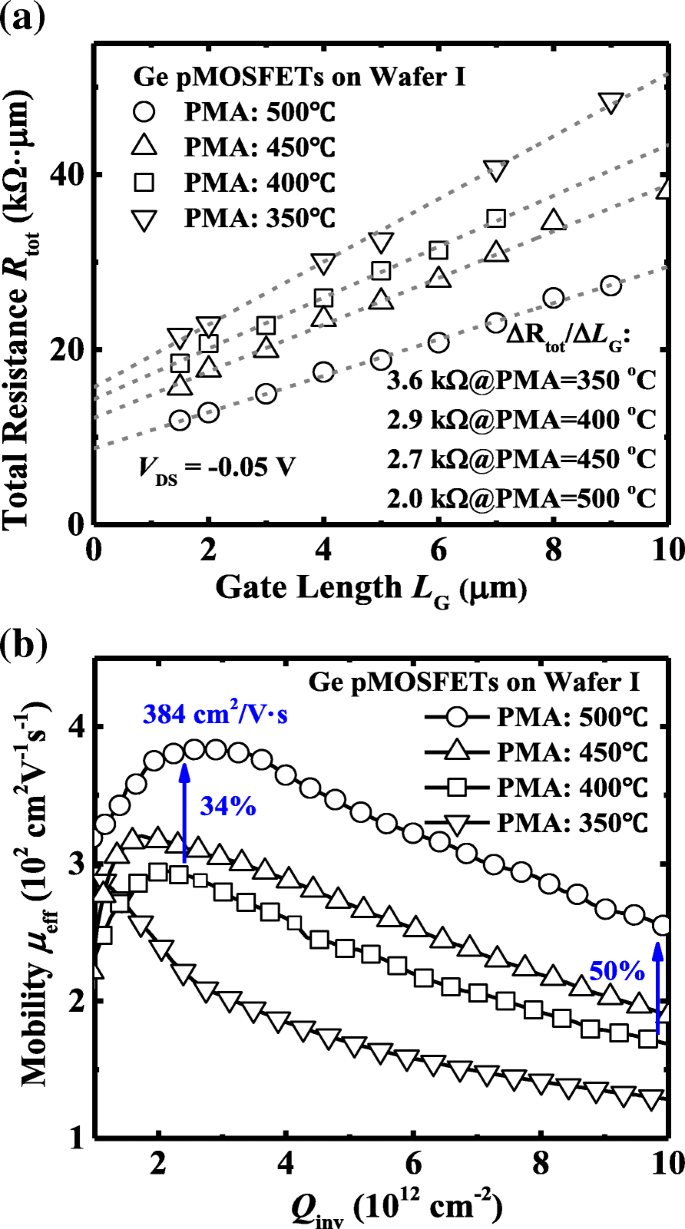

μ eff 、Ge pMOSFETのデバイス駆動電流と相互コンダクタンスに影響を与える重要な要因として、Δ R を使用して測定しました。 tot /Δ L G メソッド[18]。多数のデバイスが L で測定されました G 1.5から9μmの範囲。図5aは、総抵抗 R を示しています。 tot | V で抽出 GS - V TH | − 1Vと V DS L の関数としての− 0.05Vの G 。 R SD は、フィットした線が y で交差する値です。 -軸。 R SD 値は、350、400、450、および500°CでPMAを備えたデバイスで、それぞれ7.85、7.15、6.10、および4.35kΩ・μmと推定されました。これは、より高いPMA温度でのS / Dのより優れたドーパント活性化を示しています。 μ eff μで抽出できます eff =1 / [ WQ inv (Δ R tot /Δ L G )]、ここで Q inv はGeチャネルの反転電荷密度とΔ R tot /Δ L G R の傾きです tot 対 L G 図5aに示すように。小さいΔ R tot /Δ L G 500°CでPMAを使用するデバイスの場合、μの向上を示します eff 450°CでPMAを備えたトランジスタと比較して。図5bはμを示しています eff Q の関数として inv 分割 C を使用して抽出された曲線 - V 方法。ピークホール移動度は384cm 2 です。 / V・sは、500°CでPMAを使用するデバイスの場合、400°CでPMAを使用するデバイスよりも31%高くなります。高い Q inv 1×10 13 cm −2 、500°CでPMAを受けたGe pMOSFETは、400°Cでアニールされたデバイスと比較して移動度の向上を実現します。結晶性ZrO 2 を備えたGeトランジスタ アモルファスZrO 2 を備えたデバイスと比較して、バルクトラップ電荷の密度が低く、正孔のリモートクーロン散乱が低くなります。 。結晶性ZrO 2 間の滑らかな界面のため また、Ge、500°CでアニールされたGeデバイスは、表面粗さの散乱が低く、ピーク移動度がより高い Q にシフトします。 inv 。

a R tot L の関数として G V で GS - V TH − 1Vと V DS さまざまなPMA温度のウェーハI上のデバイスの場合は− 0.05Vです。 b μ eff 対Q inv 分割 C によって抽出 - V 方法。最高の移動度は、500°CでPMAを備えたデバイスで得られます

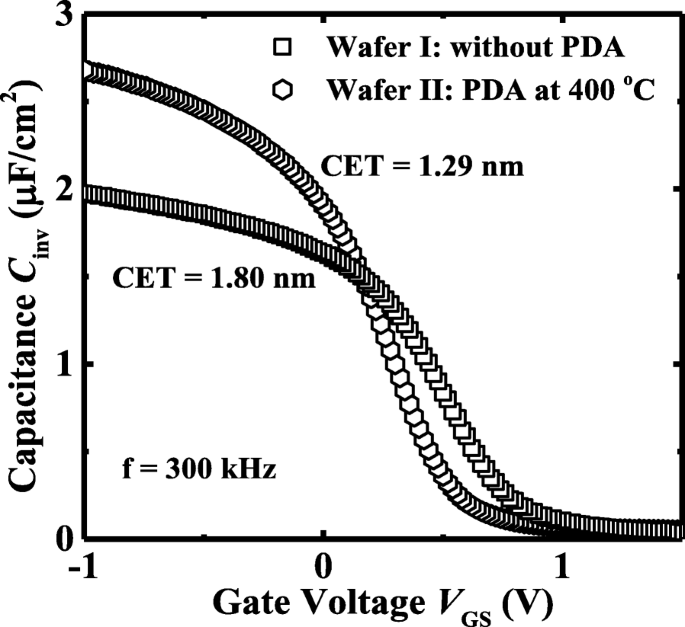

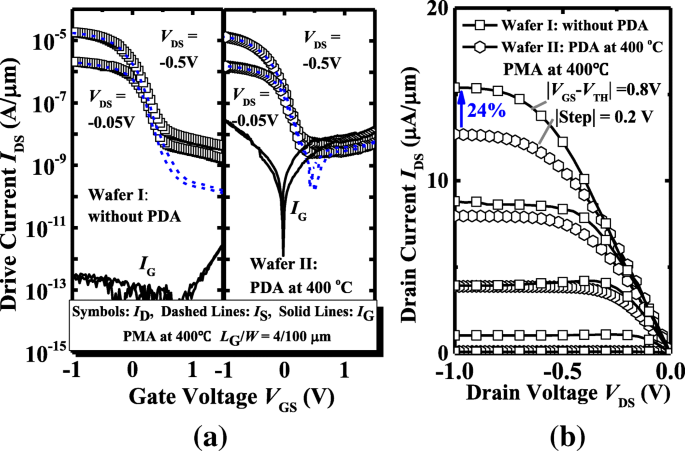

次に、GepMOSFETの電気的特性に対するPDAの影響について説明します。図6は、測定された C を示しています。 inv 対 V GS 400°CでPMAを使用したウェーハIおよびウェーハII上のGepMOSFETの特性評価。 400°CでPDAを受けたデバイスは、PDAなしのデバイス1.80 nmと比較して、1.29nmというはるかに低いCET値を持っています。図7aは、 I を示しています。 D 、私 S 、および I G - V GS ウェーハIとウェーハII上のGepMOSFETの特性曲線、および400°CでPMAを受けたデバイス。 PDAのないトランジスタと比較して、PDAのあるデバイスでは、より大きなゲートリーク電流が得られます。これは、CETが低いためです。対応する I DS - V DS 異なるゲートオーバードライブ V で測定されたデバイスの曲線 GS - V TH 図7bに示します。 PDAなしのGeトランジスタは、飽和領域での同じオーバードライブ-0.8 Vで、400°CのPDA付きトランジスタよりも駆動電流が約24%向上しています。

C inv -V GS 400°CでPMAを使用したウェーハIおよびII上のデバイスのプロット

a 私 D 、私 S 、および I G 対V GS 400°CでのPMAを使用したウェーハIおよびII上のGepMOSFETの曲線。 b 私 DS - V DS さまざまな V で測定された曲線 GS - V TH デバイス用

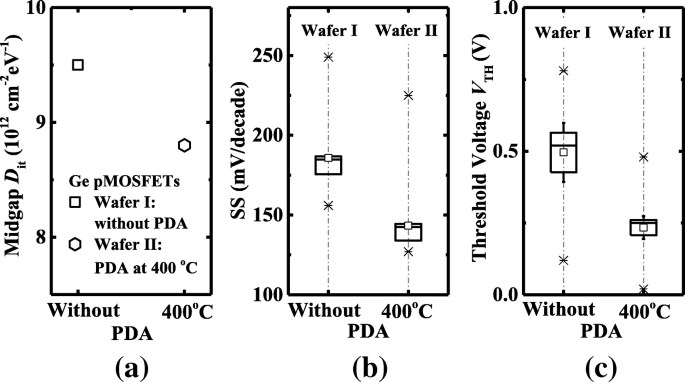

図8は、ミッドギャップ D の統計結果をプロットしたものです。 それ 、SS、および V TH PDAがある場合とない場合のGepMOSFETの図8aは、小さい D それ PDAのないデバイスと比較して、400°CでPDAのあるGepMOSFETで達成されます。図8bでは、PDAが400°Cのデバイスで、平均サブスレッショルドスイングの値が142 mV / decadeと低くなっています。これは、CETが低く D が低いことに対応しています。 それ 。これは、400°CでPDAを備えたデバイスが優れたZrO 2 を持っていることを示しています / Geインターフェース。図8cは、PDAがあるデバイスとないデバイスの V が異なることを示しています。 TH ;これは、 V で半分支配的なバンドギャップの低いトラップの密度に起因する可能性があります。 TH 。

a の比較 ミッドギャップ D それ 、 b SS、および c V TH 400°CでPMAを使用したウェーハIおよびII上のGepMOSFETの場合

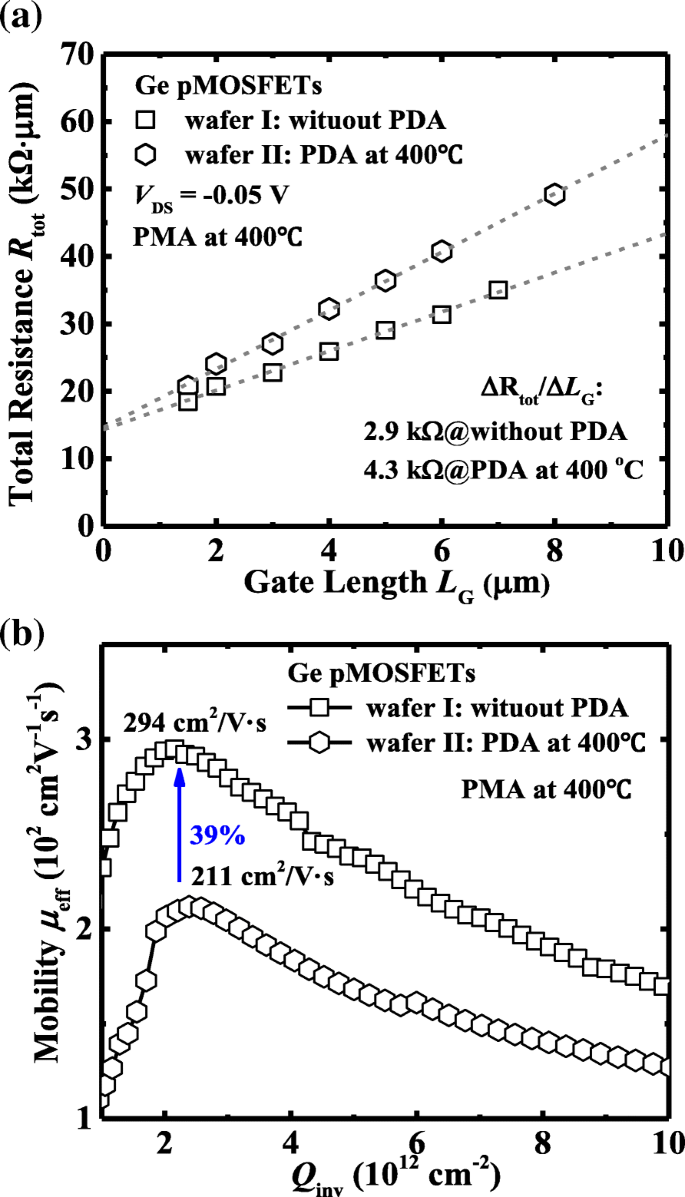

図9aは、 R を示しています。 tot 対 L G − 1Vおよび V のゲートオーバードライブでの曲線 DS 400°CでPMAを備えたデバイスの場合は− 0.05Vです。 R SD 400°CでPDAを使用しないデバイスと使用するデバイスの値は、それぞれ7.15と7.30kΩ・μmと推定されます。図9bに示すように、著しく高いピークμ eff PDAのないGepMOSFETで達成され、より小さなΔ R に対応します。 tot /Δ L G 図9aでは、PDAを備えたデバイスと比較しています。 400°CでPDAを備えたデバイスは、ピークμを示します。 eff 211 cm 2 / V・s;正孔移動度が低いのは、主にZrO 2 の固定電荷によってもたらされる強力なリモートクーロン散乱に起因する可能性があります。 誘電体。

a R tot 対 L G 400°CでPMAを使用したウェーハIおよびウェーハII上のデバイスの曲線。 b 正孔移動度μ eff 対 Q inv PDAのあるデバイスとないデバイスの場合

結論

要約すると、ZrO 2 を使用したGepMOSFETに対するPMAとPDAの影響 誘電体は広範囲に調査されました。 ZrO 2 の結晶化 ゲート誘電体は、より低いPMA温度のデバイスと比較して、正孔移動度を大幅に向上させ、CETを低減します。 384 cm 2 のピークホール移動度 / V・sと強化された駆動電流は、500°CでPMAを備えたデバイスで達成されました。 400°CでPDAを備えたデバイスは、CETが低く、 D が小さくなっています。 それ しかし、PDAのないトランジスタと比較して、正孔移動度が低く、リーク電流が大きくなります。

データと資料の可用性

この記事の結論を裏付けるデータセットは、記事に含まれています。

略語

- ALD:

-

原子層堆積

- BF 2 + :

-

フッ化ホウ素イオン

- CET:

-

容量性有効厚さ

- Ge:

-

ゲルマニウム

- HF:

-

フッ化水素酸

- HRTEM:

-

高分解能透過型電子顕微鏡

- IL:

-

界面層

- MOSFET:

-

金属酸化物半導体電界効果トランジスタ

- Ni:

-

ニッケル

- PDA:

-

堆積後のアニーリング

- PMA:

-

ポストメタルアニーリング

- SS:

-

サブスレッショルドスイング

- TaN:

-

窒化タンタル

- TDMAZr:

-

テトラキス(ジメチルアミド)ハフニウム

- ZrO 2 :

-

二酸化ジルコニウム

- μ eff :

-

効果的なキャリアモビリティ

ナノマテリアル

- KUHMUTEはSLS3D印刷でモビリティを再設計します

- AFPMを使用した高速3D印刷

- AION500MK3による高速3Dプリント

- 誘電体メタ表面を介した帯域幅の拡大による完全なテラヘルツ分極制御

- コンプライアンスフリーのZrO2 / ZrO2 − x / ZrO2抵抗変化型メモリと制御可能な界面マルチステートスイッチング動作

- ハイブリッド全誘電体-グラフェンメタ表面に基づく制御可能な複屈折を備えた偏光変換器

- 表面構造が変更された高性能有機ナノ構造シリコンハイブリッド太陽電池

- マイクロ波アニーリングによる原子層堆積Al2O3 / ZrO2 / Al2O3MIMコンデンサの誘電増強

- 高PSRRのナノスケール低電力抵抗なし電圧リファレンス

- アモルファスSiパッシベーションを備えた高移動度GepMOSFET:表面配向の影響

- 2段階のポストアニーリングを備えた原子層堆積酸化アルミニウムによる強化されたSiパッシベーションとPERC太陽電池効率