Ag / SiOx:Ag / TiOx / p ++-Siメモリスタデバイスのアナログスイッチングと人工シナプス挙動

要約

この研究では、TiO x のバッファ層を挿入することによって SiO x の間 :Ag層と下部電極、Ag / SiO x のシンプルな構造のメモリスタデバイスを開発しました :Ag / TiO x / p ++ -物理蒸着プロセスによるSi。このプロセスでは、アナログスイッチング中にフィラメントの成長と破壊を効率的に制御できます。正または負のパルス列を実装することにより、重量変調のための広範囲の抵抗変化を伴うメモリスタデバイスのシナプス特性が広く調査されています。増強/抑制、対パルス促進(PPF)、短期可塑性(STP)、およびパルスを繰り返すことによって制御されるSTPからLTP(長期可塑性)への移行など、いくつかの学習および記憶機能が同時に達成されました。リハーサル操作よりも、スパイク時間依存可塑性(STDP)も同様です。対数I-V特性の分析に基づいて、誘電体層全体の導電性Agフィラメントの制御された進化/溶解により、テストメモリスタデバイスのパフォーマンスを向上させることができることがわかりました。

はじめに

2008年、Chua教授のメモリスタの理論的概念[1]は、Strukov etal。 TiO 2 における磁束と電荷の関係に関する研究を発表しました ベースの2つのコンパクトな端末デバイス[2]は、世界中の研究者の関心を呼び起こしました。論理演算や再構成可能な無線周波数システムから不揮発性メモリアプリケーションに至るまでのさまざまな潜在的なアプリケーション[2、3、4]とは別に、メモリスタは、類似した構造と動作ダイナミクスのために、生体シナプス機能をエミュレートするために調査されました。今日、電子デバイスにおけるシナプス機能の直接エミュレーションは、脳に触発されたニューロモルフィックコンピューティングシステムの開発に不可欠であることが広く受け入れられています[5、6、7]。ただし、従来の設計の電子シナプスは、相補型金属酸化膜半導体(CMOS)テクノロジに基づいており、計算の複雑な実行プロセス、積分密度の限界、およびエネルギー散逸の観点から、フォンノイマンボトルネック効果に悩まされています。したがって、調整可能な2端子デバイスの使用は、電子シナプスの新しい構造を開発するための多くの有望な機会をもたらしました。これは、不揮発性特性、ナノスケールサイズ、低消費電力、高速応答などを備えたメモリスタの独自の特性に起因します。 。[8、9]。

最近、さまざまな材料(たとえば、ZnO 2 のような金属酸化物 、WO x 、SnO x [10、11]、Cu 2 のようなカルコゲニド S、Ag 2 S [12、13]、およびLa 2 のような強誘電体材料 O 3 、Pb 0.8 Ba 0.2 ZrO 3 [14、15])は、メモリスタデバイスの設計と製造について調査されています。多くのデバイスでは、抵抗の変化は、酸素空孔または金属イオン(Ag + など)の電界誘起移動に起因します。 、Cu 2+ 、およびAl 3+ )そして導電性の高い経路の形成。メモリスタの導電経路は一般に「導電フィラメント(CF)」と呼ばれ、その後、スイッチング動作中に切断される可能性があります。一般に、メモリスタでは2種類のスイッチング動作が観察されています。つまり、突然(デジタルスイッチング)と段階的(アナログスイッチング)です。抵抗の急激な変化はデジタル信号(0または1)と一致しており、情報の保存に役立ちます[16、17]。

デジタルスイッチングとは対照的に、メモリスタの連続コンダクタンス調整可能性は、人間の脳の学習および記憶機能の基本的な細胞単位である生物学的シナプスといくつかの類似点があります[18]。いくつかのメモリスタデバイスでは、生物学的シナプスの重量変調をエミュレートするために使用されるアナログコンダクタンスの変化が実現されています[19、20]。 Pt / a-Si:Ag / PtおよびPt / SiO x を使用したa-Siおよび酸化物ベースのメモリスタ内の拡散Ag N y :Ag / Pt構造はCa 2+ をうまく模倣しました またはNa + バイオシナプスのダイナミクス[21、22]。同様に、金属酸化物ベースのメモリスタの酸素イオン/空孔フィラメントも、短期増強(STP)やペアパルス促進(PPF)などのシナプス機能を実現するために提案されています[23、24]。ただし、生物学的学習ルールは多様であり、これまで、すべてのシナプス機能がメモリスタモデルに関与しているわけではありません[16]。

材料の選択に加えて、「金属/記憶層/金属」構造に追加の誘電体層を挿入することによるフィラメントの成長と破壊の制御は、STPやLTP、低消費電力などのシナプス機能をエミュレートするための特定の利点を提供します。最近、導電性フィラメントの形成/破壊の速度を制御するために、Wang etal。 [25]は、SiO 2 を挿入することによってアナログスイッチング動作を実証しています。 TaO x のレイヤー ベースのメモリスタ。 Wan etal。 [26]は、Ag / SrTiO 3 の構造に還元型酸化グラフェン層を挿入することにより、アナログスイッチングとエミュレートされたSTPおよびSTDP機能も実現しました。 / FTO memristorは、Agフィラメントの異常成長を制御します。さらに、TiO x の知識に基づいていることが報告されています[27、28]。 誘電率が高く(〜40)、バンドギャップが低い(〜3 eV)材料であるため、サイクル耐久性と均一性に関するメモリスタデバイスのパフォーマンスは、特にTiO 2 を挿入することで向上しています。 HfO 2 の薄層 memristiveレイヤー。これとは別に、イオン移動度が低く、酸化還元反応速度が低いため、TiO x が報告されています[24]。 薄膜は、導電性フィラメントの過成長を防ぐためのバッファー層としても機能し、シナプスの動作を改善し、抵抗性スイッチングプロセス中に導電性フィラメントの良好な接触を維持します。

この記事では、Ag / SiO x の新しい構造を報告します。 :Ag / TiO x / p ++ -Siメモリスタデバイスとそのアナログスイッチング動作。以前に報告された単層デバイス[22、29]と比較して、TiO x の挿入が発見されました。 上記の構造に示されている層は、コンダクタンスウィンドウを拡大し、スイッチングプロセス中に安定した状態を維持するという点で、メモリスタデバイスのスイッチング動作に影響を与えます。さらに、メモリスタデバイスのコンダクタンスは、それぞれ正と負の両方のパルス列の下で簡単に調整できます。私たちの最近の結果は、信頼性の高いアナログスイッチングと、短期および長期可塑性(STPおよびLTP)、ペアパルス促進(PPF)機能、スパイク時間依存可塑性( STDP)およびAg / SiO x でのSTPからLTPへの遷移 :Ag / TiO x / p ++ -Siメモリスタデバイス。

メソッド

- i。

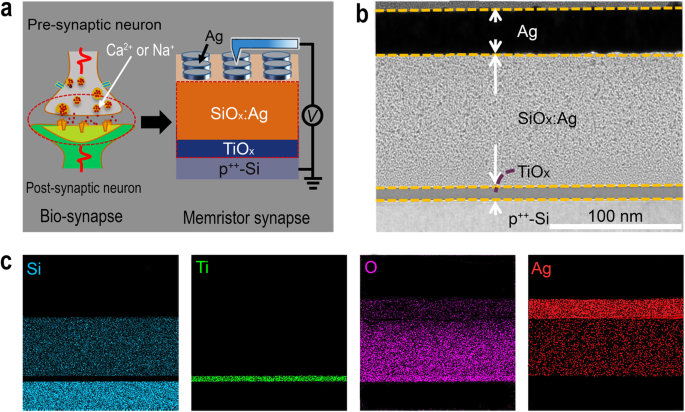

デバイス製造:図1aに示すように、メモリスタはAg / SiO x として設計されました。 :Ag / TiO x / p ++ -Si構造。 p ++ -Si基板(15×15 mm 2 )抵抗率が約0.01Ωcmの標準的な方法で洗浄し、その上にデバイスを作製しました。以下のすべてのプロセスは、高真空システム内で室温で実行されました。最初に、厚さ約10nmの酸化チタン層がp ++ に堆積されました。 -高純度セラミックTiO 2 を使用したRFマグネトロンスパッタリングによるSi基板 目標。次に、厚さ約95nmのSiO x :Ag層は、SiO 2 を使用したRF同時スパッタリングによって堆積されました。 磁気スパッタリング経路上に配置された小さなAgスライスを備えたターゲット。堆積プロセス中、Arの流量と圧力はそれぞれ50sccmと20mTorrに保たれ、RF電力は80 Wに保たれました。最後に、厚さ約30 nmのAg層の上部電極(TE)がパターン化されました。 DCマグネトロンスパッタリングを使用して薄い金属層を堆積させるフォトリソグラフィーおよびリフトオフ技術を介して。個々の電極の直径は約150μmです。

- ii。

特性評価方法:透過型電子顕微鏡(TEM)測定およびX線光電子分光法(XPS)分析を実施して、SiO x の微細構造を分析しました。 :AgとTiO x 層とAg原子の化学状態、それぞれ、最初に集束イオンビーム(FIB、FEI Nova Nano Lab 200)を使用してTEMサンプルを作成し、次にFEI Phillips CM10- SupraTEMシステムで観察しました。電気的特性評価は、プローブステーションに接続された半導体アナライザー(Keithley 2636B)を使用して実行されました。電気的測定中、正と負のバイアスは、上部電極と下部電極の間を流れる電流によって定義されました。すべての電気的測定は、空気中の室温で実施されました。

Ag / SiO x の概略図 :Ag / TiO x / p ++ -Siメモリスタデバイスとその断面TEM分析。 a デバイスの概略図と、生物学的シナプスと電子シナプスの類似性。 b Ag / SiO x の単一メモリスタユニットの断面TEMビュー :Ag / TiO x / p ++ -Si構造。 SiO x :AgとTiO x AgTEとp ++ の間に挟まれた薄膜 -SiBE電極。 c デバイス断面の元素マッピング

結果と考察

デバイスの概略図と測定構成を図1aに示します。このデバイスは、SiO x で構成される単純な構造を持っています。 :AgとTiO x AgTEとp ++ の間に挟まれた薄層 -図1bおよびcに示すメモリスタセルの断面TEMおよび元素マッピングによって確認されたSiBE。 SiO x の表面のAg原子の化学状態 追加ファイル1:図S1に示すように、XPSによって分析されます。 AgのAg3dスペクトルは、Ag3d 5/2 の結合エネルギーが368.0eVの単一のダブレットにデコンボリューションされます。 Ag3d 3/2 の場合は374.0eV 、Ag金属状態に正確に割り当てられます。追加ファイル1のHRTEM画像:図S2は、アモルファスTiO x の断面を示しています。 小さなAgナノクラスターがSiO x に表示されます :Ag層。これは、材料システムの総界面エネルギーを最小限に抑えるために、TEMサンプル準備プロセス中にAgが外方拡散することによって引き起こされる可能性があります[22]。さらに、高速フーリエ変換(FFT)により、AgナノクラスターがSiO x に埋め込まれていることが確認されます。 Ag(111)およびAg(002)ナノ結晶などの構造が多結晶です。 Ag / SiO x :Ag / TiO x / p ++ -Siメモリスタデバイス、Ag / SiO x :AgとTiO x / p ++ -図1aに示すように、それぞれシナプス前膜およびシナプス後膜としてのSi。シナプスの重みは、Ca 2+ を放出することで変化します またはNa 2+ 神経パルスが受信されたときにシナプス前膜によって「裂け目」と呼ばれるシナプス前膜とシナプス後膜の間のギャップにあるイオン。同様に、Ag / SiO x のコンダクタンス :Ag / TiO x / p ++ -Siメモリスタデバイスは、電圧インパルス下でのAgイオンの移動により、電子シナプスとして人工的に変調できます。

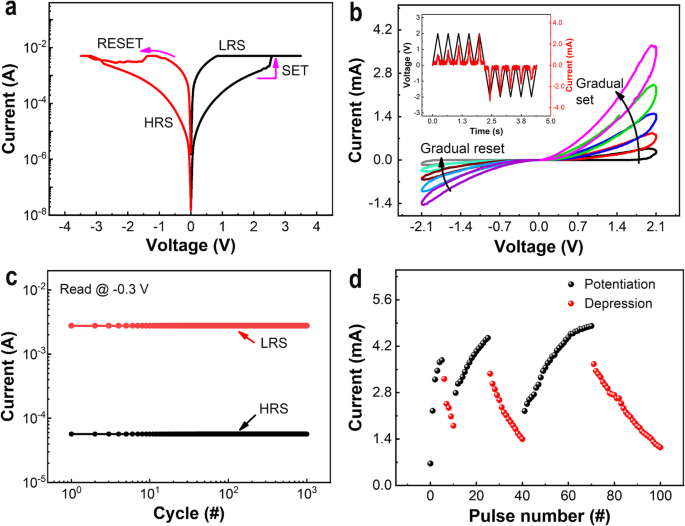

図2aは、Ag / SiO x の電流-電圧(I-V)曲線を示しています。 :Ag / TiO x / p ++ -半対数スケールのSimemristorデバイス。 0V→+ 4.0V→-4.0V→0Vのスイープバイアスの下で、測定されたI-V曲線は、メモリスタの指紋である挟まれたヒステリシスループを示しています。 Ag TEに正のバイアスが印加されると、コンプライアンス電流制限(I cc )まで電流が徐々に増加します。 )が発生し、デバイスの抵抗状態が高抵抗状態(HRS)から低抵抗状態(LRS)に変化します。これは「SET」プロセスと呼ばれます。一方、Ag TEに負のバイアスが印加されると、電流が減少し、抵抗状態がLRSからHRSに戻されます。これは「リセット」プロセスと呼ばれます。これは、デバイスの導電率が正または負の掃引バイアスに対応して変調できることを示しており、バイポーラ抵抗スイッチング動作を示しています。高電圧領域でのSETおよびRESETプロセス中の電流の急激な増加または減少の代わりに、非常に興味深いことに、デバイス電流は、0V→+ 2.1Vまたは0V→-2.1Vの繰り返し電圧掃引の下で連続的に増加または減少します。図2bに示すように。電流と電圧の時間に対する関係(I-V-t)も図2bの挿入図にプロットされており、コンダクタンスの変化をより明確に示しています。バイオシナプスの場合と同様に、電流のダウンアップまたはアップダウンの進化の明らかなデバイス応答は、I-V曲線のそれぞれ正(1〜5)および負(6〜10)の連続部分の実装後に観察されます。正(または負)の電圧スイープ中の電流の継続的な増加(または減少)は、デバイスの抵抗がDCスイープモードによって変調できることを示しています。また、後続の各正または負のスイープ中に、I-V曲線が最後のスイープが省略された場所を選択し、メモリスタデバイスの典型的なアナログスイッチング機能を示していることも観察されます。図2cのように、読み出し電圧+0.3 Vでより広いバイポーラ掃引電圧を実装することにより、メモリスタデバイスの耐久性能を評価できます。これは、デバイスがセット/リセット中にLRSとHRSの間で安定して均一に動作できることを示しています。 10 3 を超える操作 サイクル。

Ag / SiO x のI–V特性 :Ag / TiO x / p ++ -Siメモリスタデバイス。 a バイポーラスイッチング動作 b 電圧掃引を繰り返すことによる増強または抑制。挿入図は、電圧と電流の時間に対する関係(V-I-t)を示しており、増強または抑制中のコンダクタンス状態を示しています。 c 10 3 の-0.3Vの読み出し電圧での耐久性サイクリング性能テスト セットの場合は0〜 + 4.0 V、リセットの場合は0〜-4.0Vのより広い範囲のバイポーラスイープのサイクル。 d コンダクタンス変調の繰り返し特性

メモリスタデバイスは、DCバイアス掃引電圧ではなくパルス信号の下で動作させることもできます。図2dは、繰り返しの増強(正のバイアス)および抑制(負のバイアス)パルスの実装後の増強または抑制の形でのデバイス応答を示しています。増強パルスと抑制パルスの振幅はそれぞれ+ 1.2Vと-1.2Vであり、すべてのパルス幅と間隔は5msに固定されています。ここで、デバイスのコンダクタンス変調は、正または負のパルスバイアスに関係なく観察されます。これは、それぞれ増強および抑制刺激下での増強または抑制の形でのシナプス応答に類似しています。刺激パルスの数に応じてデバイスの応答をサイクルごとに調整できることは明らかであり、適用されたバイアスの極性を超えた安定した均一な増強と抑制を使用して、体重調整と記憶をエミュレートできることを示しています電子シナプスの強化[30]。

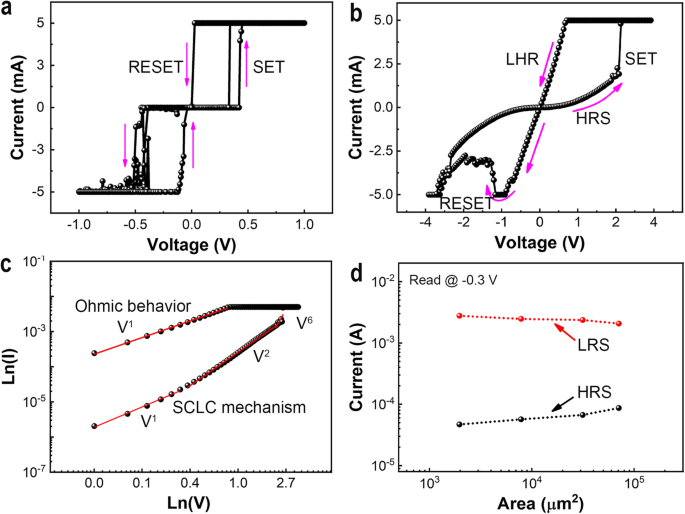

スイッチング動作を理解するために、I-V特性をフィッティングすることによって伝導メカニズムを分析します。この目的のために、スタンドアロンのSiO x :Ag / SiO x の構造を持つAg薄膜ベースのメモリスタ :Ag / p ++ -Siも製造されています。図3aに示すように、準DC電圧スイープに対するデバイスの応答は、以前に報告されたように、典型的なしきい値スイッチング動作を示しています[29、31]。矢印の方向は、デバイスが揮発性メモリとして2つの状態間を循環できることを示しています。ただし、Ag / SiO x のI-V曲線 :Ag / TiO x / p ++ -Siメモリスタデバイスは、状況がスタンドアロンのSiO x とはまったく異なることを示しています :Agベースのメモリスタデバイス。図3bは、デバイスがI-V曲線の正と負の部分でLRSとHRSの観点からバイポーラスイッチング動作を示すのに対し、動作電圧は比較的高いことを示しています。図3cは、Ag / SiO x のI-V曲線を示しています。 :Ag / TiO x / p ++ -SIメモリスタデバイス。HRSおよびLRSの正の領域データのLn(I)対Ln(V)として適合されます。これらのフィッティング結果は、HRSでの電荷輸送挙動が、オーム領域(I / V)、子供の法則領域(I /)の3つの部分で構成される古典的なトラップ制御の空間電荷制限伝導(SCLC)メカニズムと一致していることを示しています。 V 2 )、および急電流増加領域[32]。一方、傾きが=1であるLRSでの線形動作は、図3cに示すように、優れたオーム動作を示します。 HRSとLHRでの異なる伝導挙動は、LRSでの導電性Agフィラメントの形成によって証明されています[32]。図3dはさらに、抵抗スイッチングがフィラメントの形成/破壊を行うことによって引き起こされることをサポートしています。デバイスのLRSはデバイスのセルサイズに依存しませんが、デバイスのHRSはセルサイズに比例することがわかります。 LRSでのこのサイズに依存しない特性は、フィラメントベースのメモリデバイスの導電性で一般的に観察されています[33]。したがって、Ag / SiO x の抵抗スイッチング現象は :Ag / TiO x / p ++ -Siメモリスタデバイスは、通常、正/負のバイアス電圧下での導電性フィラメントの制御された形成/破壊に起因します。コンダクタンスの段階的な変化は、他の報告と同様に、電界下でのTEとBEの間の断面ギャップの変化に起因する可能性があります[34]。したがって、デバイスの総抵抗は、等価回路に従ってR =Rij =V / Iとして表すことができます。ここで、Rijは、TEとBEの間のCFの横方向のギャップサイズに関連する抵抗として定義されます。したがって、適切にプログラムされたバイアスを使用してTEとBEの間のAg CFサイズを変調することでこのギャップを調整できる場合は、メモリデバイスの導通または抵抗を徐々に調整できます。

Ag / SiO x の伝導メカニズム分析 :Ag / p ++ -SiおよびAg / SiO x :Ag / TiO x / p ++ -Siデバイス。 a Ag / SiO x の線形I–V曲線 :Ag / p ++ -Siおよび b Ag / SiO x :Ag / TiO x / p ++ -Siデバイス。 c 伝導メカニズムは、Ag / SiO x のHRSでのSCLCおよびLRSでのオーミックに対応します。 :Ag / TiO x / p ++ -( b のI–V曲線の正の領域のフィッティング結果によるSiデバイス )。 d LRSまたはHRSでのコンダクタンスの細胞面積依存性

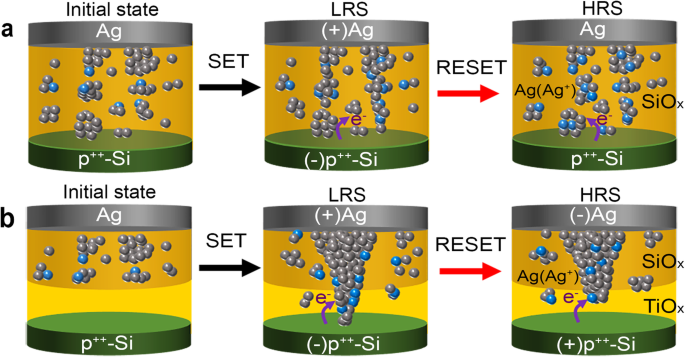

対応する物理モデルも図4に示され、スタンドアロンのSiO x のスイッチングメカニズムを解釈します。 :AgおよびSiO x :Ag / TiO x ベースのメモリスタデバイス。 SiO x におけるAgナノ粒子の挙動 ベースのセルは、以前に報告されたのと同様に、双極電極間の電気化学反応(AgイオンとAg原子の移動と蓄積)に基づいて解釈できます[22、35]。スイープ電圧が印加されると、Agナノ粒子がさらに成長して電極間のギャップを埋め、コンプライアンスレベルまで急激な電流が増加し、LRSでメモリスタがオンになります(図の中央のパネルを参照)。 4a)。電気的バイアスを取り除いた後、ブリッジを早期に形成した細長いAgナノクラスターは急速に収縮し[22]、デバイスはHRSに戻り(図3aの最後のパネルに示すように)[35]、双極しきい値スイッチングを示します揮発性メモリデバイスのように、2つの状態間で循環できるメモリスタの動作。

スイッチング動作の物理モデルの概略図。 a Ag / SiO x :Ag / p ++ -Siメモリスタデバイス。 b Ag / SiO x :Ag / TiO x / p ++ -Siメモリスタデバイス

SiO x の場合、状況はまったく異なります。 :Ag / TiO x ベースのメモリスタデバイス。ここで、SiO x 薄層はバンドギャップが高く(〜9 eV)、誘電率が低くなります(〜3)が、TiO x 層のバンドギャップは低く(〜3 eV)、誘電率は高く(〜40)、SiO x を横切る電界になります。 TiO x よりも高い層 層、スイッチング層でより多くのAg原子を溶解します[28]。界面層を横切るAg原子とAgイオンの移動と蓄積を制御するのは、酸化チタンの低いイオン移動度と低い酸化還元反応速度です[36]。これらの2つの事実は、前述のように、TEからBEへのナノコーン型フィラメントの形成を引き起こす可能性があります[37]。 TEからBEへのナノコーンの形でフィラメント成長の効果的な閉じ込めの形で集中した金属領域は、周期的操作中の抵抗状態の制御を提供することができます[38]。上部のAg電極が二重層全体で十分に正にバイアスされている場合、誘電体層全体の電界は、AgイオンをAgTEからp ++ に駆動するのに十分です。 -Si BEは界面層を通過し、電極間の有効ギャップを減少させます(図4bの中央のパネルに示されているように)。 Agフィラメントは、負の電圧が印加されない限り溶解せず、バイアス電圧が除去されても元の形状を維持する傾向があります。負の電圧が印加されると、通常のRESETが開始され、熱支援電気化学プロセスにより、Ag CFが部分的に(通常は最も薄い場所で)分離されます[39]。メモリスタデバイスはオフになり、HRS(図4bの最後のパネル)に戻り、不揮発性メモリデバイスとして2つの状態(図3bに表示)間で可逆的に循環します。図4bの左側のパネルは、ここで形成されたフィラメントが図4aの中央のパネルのフィラメントよりも太くなければならないことを示しています。これは、負の電圧が印加されない限り溶解および破裂することはできません。 SiO x のフィラメント部分 層は、TiO x のナノコーン部分の層よりもはるかに薄いです。 層、そしてフィラメント全体の形はどういうわけかナノコーンのようなものです。したがって、負のバイアスが印加されると、負の電圧が印加されるとフィラメントが急速に破壊されますが(図3b)、電圧はさらに上昇し、電流は再び増加します。これは、高バイアスでの負のSETのリスクを示しています。 BEの表面近くに存在する残留Ag原子による範囲。

実際、HRSでの総メモリスタ抵抗は、フィラメントナノコーンチップと下部電極の間のギャップに関連しているだけであり、電気バイアスを調整することで増減できます[33]。メモリスタのHRSを変更するこの傾向は、図2bに見ることができます。この図では、0Vから+ 2.1Vおよび0Vから-2.1Vの繰り返し掃引バイアスの下で、電流を連続的に増減できます。一方、+ 2.1 V未満の電圧を一定に掃引するだけでは、TEとBEの間に導電性フィラメントを形成するのに十分ではありません。代わりに、導電性のAgフィラメントが徐々にAg原子を蓄積し、追加ファイル1:図S3に示すように、電極間の有効ギャップが減少します。したがって、適切なプログラミングバイアスを使用することにより、通常のしきい値スイッチングから段階的スイッチングへの移行を実現でき、生物学的シナプスで観察できるように、電極間の有効ギャップを調整することでメモリセルの総抵抗を調整できます。

バイオシナプスと同様に、適切なパルスプログラミングによる入力刺激は、メモリスタデバイスのコンダクタンス状態を変更して、いくつかの神経タスクを実行できます。 PPFは別の種類の重要な機能であり、入力刺激の時間的合計によってコンダクタンスを調整し、シナプスフィルタリングや適応を含むいくつかの短期的な神経タスクを実行できます[40、41]。バイオシナプスのPPF機能は、次のように機能します。2回の連続するスパイク刺激中に、2番目のシナプス後応答が最初の応答よりも高くなり、スパイクの間隔時間が回復時間よりも短くなります[22]。図5aは、デバイスの応答を示しています。これは、0.08秒のスケールとして指定された固定幅と間隔で振幅+ 2.0Vの促進パルスのペアを実装した後に監視されます。最初のパルスよりも2番目のパルスの応答として電流の顕著な増加が観察され、適切なパルスプログラミングの実装後のコンダクタンス状態の明らかな変化を示しています。後続の2つのパルス間の間隔中に、電流の減衰が観察されます。これは、デバイスに揮発性の特性が存在することに起因する可能性があります。コンダクタンスの減衰は、増強パルスの除去後のAg原子の拡散に対応する可能性があります[42]。成功したPPF関数は、2つの連続するパルス間の時間間隔がAg原子の拡散緩和時間よりも短く、より多くのAg原子がSiO x に押し込まれる場合にのみ実行できます。 :Ag / TiO x 層。さらに、飽和状態は、図5bに示すように、振幅+2.0 V、0.08sのスケールと呼ばれる固定幅と間隔の多数の促進パルスでデバイスが連続的に刺激されると達成されます。結果は、高周波パルスが適用されると、SiO x でより多くのAg原子をポンピングすることを示しています。 TEとBEの間に導電性ブリッジが形成され、飽和レベルに達するまで層を形成します[22]。この現象は、パルス列の染色されていないスパイクが適用されたニューロンの過度の興奮性を回避するために、シナプスの重みの変化が飽和値でなければならないというヘッブの学習規則と非常に似ています[43]。

ペアパルスファシリテーション(PPF)の実験結果。 a Ag / SiOでのPPFの実装 x :Ag / TiO x / p ++ -0.08秒で+ 2.0Vパルス高さを使用するSiデバイス。 b 同じ幅と0.08sの間隔で振幅+ 2.0Vのパルス列を使用した飽和のシナプス荷重運動のデモンストレーション

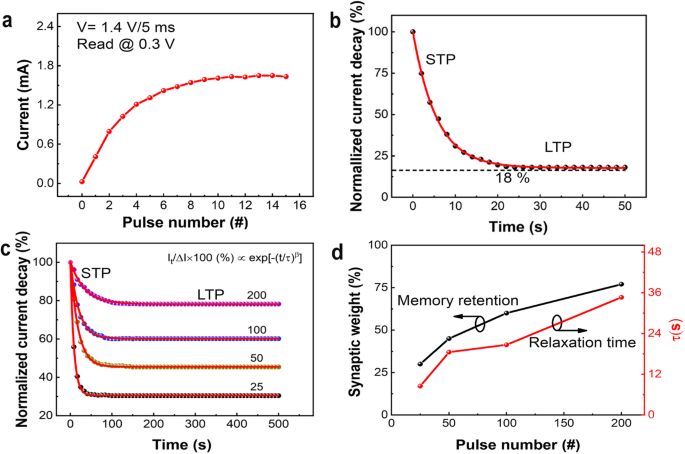

さらに、生物学的シナプスの場合と同様に、メモリスタは、強化スパイクの実装後に電流が突然減少することで記憶喪失を被ります。これは、メモリスタにSTPが存在するためと考えられます[44、45]。神経生物学では、STPとLTPは一般的に短期記憶(STM)と長期記憶(LTM)とされています[46]。 STPからLTPへの移行は、刺激の繰り返し(つまり、リハーサルのプロセス)によって発生する可能性があることが確立されています[46、47]。この動作を検証し、生物学的シナプスで観察された動作と比較するために、一連の電圧パルスがAg / SiO x に実装されています。 :Ag / TiO x / p ++ -Siメモリスタデバイス。図6aは、15個の連続パルス(振幅+1.4 V、幅、間隔5 ms)を実行した後の、初期状態の0.05mAから1.8mAへの電流の増加を示しています。正規化された電流減衰((I t -I o )/ I o ×100%)は、時間( t )で増強パルスを印加した直後の読み取り電圧+ 0.3Vで測定されます。 )、図6bに示すように。正規化された電流減衰と時間の関係は、式(1)で与えられる関係によく適合します。 (1)[48]:

$$ {\ Delta I} _t / {\ Delta I} _o \ times 100 \%=\ exp \ left [-{\ left(t / \ tau \ right)} ^ {\ beta} \ right] $$( 1)

Ag / SiOの電流減衰とメモリ保持 x :Ag / TiO x / p ++ -Siメモリスタ。 a 連続した15の増強同一パルスの実装後の電流の増加。 b デバイスを刺激した後、電流減衰は+ 0.3Vの読み取り電圧で監視されます。 c 刺激数のパルス列を実装した後のSTPからLTPへの遷移を示す時間に対する正規化された電流減衰。 d 記憶の保持と緩和時間(τ )パルス数に

ここでは、τ 緩和時間と呼ばれ、β ストレッチインデックスと呼ばれます(0 <β <1)。一般に、この関係は、エネルギーのランダムな分布を持つ無秩序な材料の緩和プロセスを説明するために使用されます。この曲線は、シナプス荷重の減衰が心理学の人間の記憶の「忘却曲線」に類似していることを示しています[49]。デバイスで。ただし、デバイス内の正規化された電流の明らかな減衰は、非常に短い時間間隔( t )で観察されます。 )その後、低コンダクタンス状態で飽和レベルに達します(50秒で最大16%)。この状況下で、パルスパラメータを他に変更することなく、パルス数を繰り返してさらにシミュレーションプロセスを実行しました。電流は、パルス列の各セットに対して同じ初期状態から異なる数のパルス(つまり、25、50、100、および200)を課した直後に、+ 0.3Vの読み取り電圧で測定されます。図6cは、測定の各セットにおける時間の経過に伴う正規化された電流減衰が、式(1)で与えられる関係に適合していることを示しています。 (1)。図6dは、刺激数の増加により、緩和時間(τ )が増加し、忘却プロセスがゆっくりと消えることを示します。一方、電流レベルの明らかな上昇が観察され、図6dに黒い線で示されているように、シナプス荷重(コンダクタンス)の正の変化を意味します。図6に示されているこれらの結果は、デバイスにSTPとLTPが存在することの明確な証拠を提供します。刺激の数が少ないと、デバイスにSTPを誘発するだけで、飽和レベルでコンダクタンスがわずかに上昇します。したがって、反復刺激の回数を増やすことにより、リハーサルプロセスはコンダクタンスレベルを上げるだけでなく、図6dに赤い線で示すように、長期記憶保持現象を実現します。

従来のデジタルタイプのメモリは、情報を保存するために非揮発性を必要としますが、バイオシナプスでは、情報が処理され、それに応じてメモリの状態が再構成されます。図6からわかるように、STPからLTPへの移行が実現され、それに応じてシナプスの重みが調整され、シナプスの重みが小さい重要でないものは一時的に保存され、時間とともに減少します。この現象は、アトキンソンとシフリンによって提示された「マルチストアモデル」[50]と非常によく似ています。このモデルでは、最初に入力情報が分析され、次にリハーサルプロセスを通じて「シナプスの重み」の重要性に応じてさまざまな階層レベルに保存されます。したがって、シナプス荷重の増加とその結果としての緩和時間の延長(τ )刺激数の関数としての私たちのデバイスでは、リハーサルスキームが最もよく検証されています。

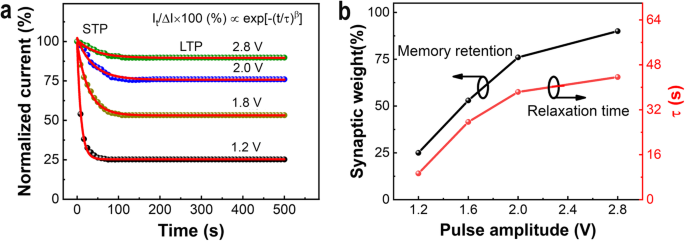

パルス繰り返しプロセスに加えて、STPからLTP現象への遷移が、パルス強度の関数としてさらに調べられます。図7aに示すように、デバイスの応答は、さまざまなパルス振幅、つまり+1.2 V、+ 1.6 V、+ 2.0 V、および+ 2.8Vの実装後に監視されます。電流は、50パルスで構成される各パルス列を印加した後、+ 0.3Vの読み出し電圧で監視されます。図7aの拡張指数緩和モデルでのフィッティング結果は、緩和時間がパルス強度の関数として増加することを示しています(図7bの赤い線で示されているように)。一方、図7bに示すように、より大きなτではシナプス荷重の約90%の上昇が観察されます。 43sおよび+ 2.8Vの振幅であり、小さいτでのシナプス荷重の約25%よりもはるかに高いです。 10sおよび+ 1.2Vの振幅(図7bの黒い線に示されている)の値であり、LTPの形成を示しています。これらの結果に基づいて、デバイス内のLTPの形成と持続性は、パルス数またはパルス振幅の両方に大きく依存していることが簡単にわかります。これらの結果は、記憶状態、つまりSTMとLTM、およびバイオシナプスにおけるそれらの安定性が入力刺激特性に関連しているという事実と一致しています。

Ag / SiO x の電流減衰の実験結果 :Ag / TiO x / p ++ -刺激プロセス後のSiメモリスタデバイス。 a STPからLTPへの変換を示す時間に対する正規化された電流減衰。 b 記憶の保持と緩和時間(τ )パルス振幅の関数として

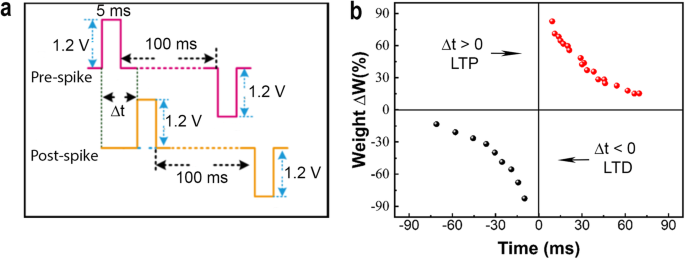

スパイク時間依存可塑性(STDP)は、生物学的シナプスにおける学習および記憶機能[51]のもう1つの基本的な特性です。電子シナプスでは、シナプス前とシナプス後のパルスの相対的なタイミングによって重みを変調できることが報告されています[52]。ヘッブのSTDP規則は、次のように機能します。スパイク前がスパイク後(Δt> 0)に先行する場合、2つのニューロン間の接続強度を強化する可能性があります。対照的に、ポストスパイクがプレスパイクの先頭にある場合(Δt<0)、2つのニューロン間の接続強度が弱くなる可能性があります。このような2つのニューロン間の接続強度の強化と弱化は、それぞれLTPとLTDとも呼ばれます[45]。プロセス全体で、時間に対するスパイク前とスパイク後の順序によって、重量変化(ΔW)の極性が決まります。デバイスでSTDPルールをエミュレートするために、図8aに示すように、スパイク前後の信号として1対のパルス(+1.2 V、5 ms、および-1.2 V、5 ms)が実装されています。 Δtの減少に伴い、より大きなコンダクタンスの変化(シナプス荷重)が現れることがわかります(どちらの場合も、Δt> 0およびΔt<0の場合)。シナプス荷重の変化率は、ΔW=(G t −g 0 )/ G 0 ×100%。ここで、G 0 刺激前に測定されたコンダクタンスとG t は、それぞれスパイク前とスパイク後のペアを使用して刺激後に測定されたコンダクタンスです。シミュレーションプロセスの前後のΔWとΔtの関係を説明できるプロットを図8bに示します。シナプス前(正)がスパイク後(負)の前に現れる場合(Δt> 0)、コンダクタンスはΔtの減少とともにΔWの増加とともに強化されることがわかります。逆に、シナプス前(正)がスパイク後(負)の後に現れる場合(Δt<0)、デバイスの正味コンダクタンスは、Δtの増加とともにΔWで減少(抑制)されます。これらの結果は、Ag / SiO x :Ag / TiO x / p ++ -Si memristorデバイスは、人工シナプスの形でヘッブのSTDP学習ルールをエミュレートすることに成功しました。

Ag / SiO x でのSTDPルールの実装に関する実験結果 :Ag / TiO x / p ++ -Siメモリスタデバイス。 a 同じ幅5msで固定された振幅+ 1.2Vと-1.2Vのパルスのペアを含む電気プログラミングバイアスの実装の概略図。刺激パルス間の接近する時間差はΔtms(t =±10n、 n =1、2、…、10); b スパイクタイミング(Δt)の関数としてのシナプス荷重(ΔW)は、メモリスタデバイスの相乗作用と抑うつ行動をよく示しています

結論

要約すると、Ag / SiO x の単純な構造を持つ新しい種類のメモリスタデバイス :Ag / TiO x / p ++ -Siは物理蒸着プロセスによって製造されています。正または負のパルス列を実装することによるシナプスの重み変調のための広範囲の抵抗変化を伴うメモリスタのシナプス特性は、広く調査されてきました。短期/長期増強および抑制(STP / STD、LTP / LTD)、PPF、STPからLTPへの移行など、いくつかの重要な学習および記憶機能が、このような単一の製造されたメモリスタデバイスで同時に実証されています。 STDPは、リハーサル操作よりもパルスを繰り返すことによって調整および制御されます。さらに、対応する物理モデルを使用した対数I-V特性の分析は、Agおよびp ++ 全体でのAgフィラメントの制御された形成/溶解を示しています。 -Si電極は、新しいAg / SiO x の性能を向上させる可能性があります :Ag / TiO x / p ++ -TiO x のバッファ層を備えたSiメモリスタデバイス SiO x の間 :Ag層と下部電極。この開発されたデバイスは、人工シナプスとして、新世代の生体模倣ニューラルネットワークとコンピューティングシステムの設計とハードウェア実装に潜在的な研究の見通しをもたらす可能性があります。

データと資料の可用性

すべてのデータは制限なしで完全に利用可能です。

略語

- BE:

-

下部電極

- HRS:

-

高抵抗状態

- I-V:

-

電流-電圧

- LRS:

-

低抵抗状態

- LTM:

-

長期記憶

- LTP:

-

長期的な可塑性

- PPF:

-

ペアパルスファシリテーション

- SCLC:

-

空間電荷制限伝導

- STDP:

-

スパイク時間依存可塑性

- STM:

-

短期記憶

- STP:

-

短期的な可塑性

- TE:

-

上部電極

- TEM:

-

透過型電子顕微鏡

- XPS:

-

X線光電子分光法

ナノマテリアル

- アナログおよびデジタル信号

- アプリケーションを備えたアナログおよびデジタルセンサーの種類

- セレクタおよびメモリとしてのV / SiOx / AlOy / p ++ Siデバイスの二重機能

- Ge / Siチャネル形成とデバイス性能に及ぼすエッチング変動の影響

- 不揮発性メモリのスイッチング特性に及ぼす二分子膜CeO2-x / ZnOおよびZnO / CeO2-xヘテロ構造と電鋳極性の影響

- 強化された近赤外吸収体:2段階で製造された構造化ブラックシリコンとそのデバイスアプリケーション

- Ag / BiPbO2Clナノシート複合材料の強化された可視光応答性光触媒特性

- テラヘルツ範囲での吸収と偏光変換の切り替え可能な機能を備えた多機能デバイス

- パッシブ直接グリセロール燃料電池におけるナノ構造Pdベースの電極触媒および膜電極接合体の挙動

- 人工知能は量子システムの振る舞いを予測します

- 人工知能の長所と短所