PCIE に基づく高速パスワード カードの PCB 設計と研究

現在、インターネット技術の急速な発展により、電子メール、オンライン決済、個人通信の大規模なアプリケーションが見られます。このような背景の下、情報セキュリティは世界中で重要な研究テーマとなっています。 PKI (Public Key Infrastructure) 技術は、公開鍵の理論と技術を使用してセキュリティ サービスを提供します。 PCIE (Peripheral Component Interface Express) テクノロジは、シリアル データ伝送とポイント ツー ポイント相互接続テクノロジを適用した第 3 世代の I/O バス規格として、高速デバイスに広く適用されています。デジタル システム設計の分野では、比較的高いクロック周波数がシグナル インテグリティ、パワー インテグリティ、クロストークの観点から問題を引き起こし、従来の PCB 設計ではシステムの安定性の要件を満たすことができません。

この記事では、PCIE 高速シリアル伝送の利点に従って、PCIE に基づく高速パスワード カードの PCB 設計スキームを提供します。

全体的な設計スキーム

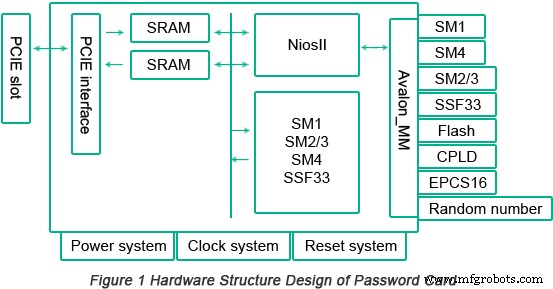

アルテラが設計したCyclone IV GXに属するFPGAチップEP4CGX50CF23C6Nがこの設計に適用され、PCIE IPハードコアモジュールを統合し、4つの高速データ伝送パスワードカード設計を実装しています。 4 種類のチップ、チップ 1、チップ 2、チップ 3、およびチップ 4 は、それぞれ SM1、SM2/SM3、SM4、および SSF33 のアルゴリズムを実装し、パスワード カードの初期化、秘密鍵の管理、バックアップと回復、および権限の機能を実装することができます。管理。パスワード カードは PC に適用され、PCIE スロットを介して PC のメイン ボードに接続され、PC によって制御されます。 FPGA の IP ハードコアは、PCIE を実装するために適用され、PCIE コアと SRAM キャッシュおよび制御モジュール間の通信につながります。コントロール センターとして、NiosII はパスワード カード ソフトウェアの機能を実装します。一方、追加のパスワード チップは、各インターフェイス モジュールとパスワード カード間の通信を実装します。パスワードカードのハードウェア構造設計は、以下の図 1 に示されています。

高速 PCB 設計

• スタックアップとレイアウト

スタックアップ設計は考慮すべき最も重要な問題であり、合理的なスタックアップ設計は EMI (電磁干渉) 放射を抑制し、電源プレーンまたはグランド層の過渡電圧を可能な限り小さくし、信号と電源の電磁界をシールドします。一般に、高速デジタル回路の設計では多層基板や複数電源が適用されます。 PCB積層設計は、回路クロック周波数、PCB製造コスト、ピン密度、製造期間、および信頼性などの包括的な要素に基づいて実装されます。また、非対称積層設計では基板の反りが発生するため、多層基板の層は対称に保ち、基板の数は偶数にする必要があります。この記事で設計されたパスワード カードは、PCIE スロットを介して PC に接続され、回路基板のサイズと形状は、高さ約 67mm、長さ約 174mm で固定され、底部に PCIE X4 インターフェイス ピンを構成します。高いコンポーネント密度と厚いルーティングの結果、PCB 層の数は、信号層、電源層、信号層、電源層、グランド層、信号層の分布を持つ 6 層としてピックアップされます。この設計には、3 つの信号層、1 つのグランド層、および 2 つの電源層が含まれており、信号の完全性に必要な環境を提供します。

PCB スタックの決定後、コンポーネント グループとレイアウトを実装する必要があります。まず、PCB の寸法とパターンに従って、ライン接続、機能的な分割、およびコンポーネント間のトリムと美しさを考慮して、コンポーネントの位置をプログラムする必要があります。次に、コンポーネント電圧のさまざまなグレードに応じてコンポーネントを合理的に分散して、電圧ワイヤをできるだけ短くする必要があります。これにより、電源ノイズの干渉を減らし、電源の安定性を高めることができます。チップの配置は、補助回路とチップの関係、クロック端子後方の水晶振動子の配置に注意してください。高ノイズ部品を水晶発振器の周りに配置することは避け、駆動部品の近くに配置する必要があります。さらに、各チップの電源ピンと信号ピンの配置は、接続されたラインに基づいて位置と方向を調整して考慮する必要があります。 PCIE スロット、挿入穴、表示 LED の位置が固定されている場合、パスワード カードの長さと幅の比率は 2:1 以上であるため、固定コンポーネントのコンポーネント レイアウトをコンポーネント レイアウトの最初に考慮する必要があります。また、コンポーネントと FPGA 間の接続線が多数あるため、PCB の上下のスペースを順番に有効に使用できるように、他のコンポーネントの配置よりも前に FPGA を中心としてコンポーネントのレイアウトを実装する必要があります。コンポーネントとコンポーネントと位置決め穴の間に十分なスペースを空けてください。

• 電源設計

高速回路基板の設計において、電源システムの設計はシステム全体の成功に直結します。製品の信頼性を確保するためには、電源とグランドから発生するノイズを最小限に抑える必要があります。層の方法における配電スキームの適用は、電力が層全体の金属を介して分配されるという事実を指し、電力インピーダンスとノイズを減らし、信頼性を高めます。 PCB には複数の電源が関係するため、ノイズ ループとしての公衆インピーダンス結合干渉を排除できるマルチ電源層設計を適用する必要があります。デカップリング キャパシタンスの適用は、コンデンサを PCB の最下層または最上層にのみ配置できるため、デカップリング キャパシタを接続するワイヤは短く太くする必要があるため、パワー インテグリティの問題を解決することができます。チップの材料に応じて、電源ラインに流れる電流を計算し、リードの幅を決定することができます。リードが広いほど、より多くの電流を流すことができます。実験式は次のように表されます:W(線幅:mm) ≥ L(mm/A) x I(電流:A)

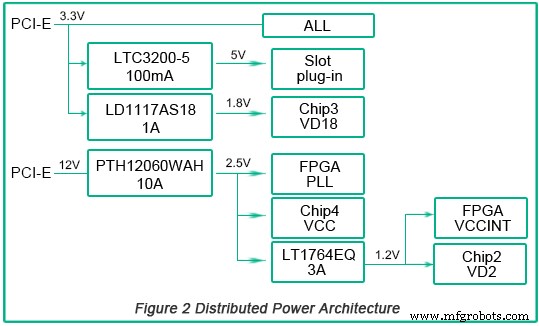

PCB 上の複数の電源は、バック ボードを使用して電源ボードから 1 種類または 2 種類の電力を取得し、その電力はコンポーネントが必要とする他の電力に変換されます。電力の変換は、集中型電力アーキテクチャと分散型電力アーキテクチャの 2 つのアーキテクチャに分けられます。前者は、電力が独立した電力によって供給され、必要なすべての種類の電力に変換されることを指し、後者はマルチグレード電力変換を指します。集中型電源アーキテクチャにはコストが高く、PCB 面積が大きいという欠点があるため、この設計では分散型電源アーキテクチャが適用されます。暗号化カードは、12V、3.3V、5V、2.5V、1.2V、および 1.8V を含む 6 つの電源に関係します。この設計は、PCIE スロットに 3.3V および 12V 電源が参加することから始まり、3.3V 電源は電圧変換チップを介して 5V 電源と 1.8V 電源を生成し、プラグインとチップ 3 に電源を供給します。次に、12V 電源は2.5V 電力に変換され、FPGA とチップ 4 に電力を供給します。最後に、2.5V 電力は 1.2V 電力に変換され、FPGA とチップ 2 に電力を供給します。暗号化カードの分散電力アーキテクチャを以下の図 2 に示します。

• スルーホール設計

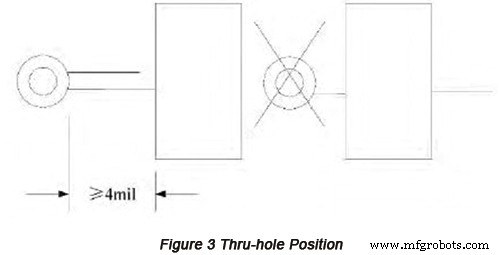

高密度の多層PCBの設計レイアウトのプロセスでは、層間の電気通信を提供するために、ある層から別の層に信号を伝送するスルーホールを適用する必要があります。スルーホールの位置設計には細心の注意が必要です。パッド上にスルーホールを配置してはならず、印刷された 1 本の線で接続できます。そうしないと、トゥームストーンやはんだ不足などの問題が発生します。はんだマスクは、距離を 4 mil に設定してスルー ホール パッド上にコーティングする必要があり、スルー ホールははんだ付け側のチップ部品用のパッドの中央に配置してはなりません。スルーホールの位置は、下の図 3 に示されています。

さらに、スルーホールの位置は、プラグイン側に面取りが必要なゴールドフィンガーに近すぎてはなりません。回路基板を PCIE スロットに差し込むために、(1~1.5)x45° の面取りをプラグイン基板の 2 つの側端に設計できます。

• 高速信号ルーティング

ルーティングの過程で、クロストークを減らすことができるように、接続ラインを最小限にするように分配を合理的に調整する必要があります。高速デジタル信号ルーティングのプロセスでは、信号電流によるリターン パスの生成を回避するために、マルチ電源レイヤー ルーティングの近くの信号レイヤーは電源基準面から遠く離れている必要があります。

高速回路のクロック信号周波数は比較的高いため、ジッタ、ドリフト、および変形がシステムに大きな影響を与えるため、高速 PCB 設計では信号波干渉を小さくする必要があります。したがって、クロックの分配とルーティングの問題を最初に考慮する必要があります。配線は高速クロック信号に実装する必要があり、クロックと電源間のクロストークを防ぐために、メインクロック信号ラインの配線はできるだけ短く、ストレートで、スルーホールや電源部分がないようにする必要があります。異なる周波数の複数のクロックが同じ PCB に適用される場合、異なる周波数の 2 つのクロック ラインを平行に維持してはなりません。ただし、同じ周波数のクロック信号を使用する複数のコンポーネントの場合、スパイダー タイプ、ツリー タイプ、およびブランチ タイプによってネットワークを分散できます。

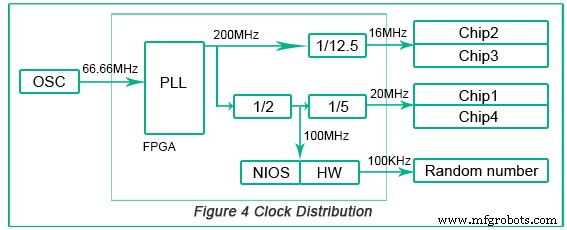

高速暗号化カードでは、FPGA は PCB 上の水晶発振器を介して 66.66MHz クロックを取得します。 FPGA内部のイントリンシックロックでループした後、200MHzの基本クロックをチップ2とチップ3のインターフェースとして生成し、クロックを動作させます。次に、100MHz のクロックが NiosII ソフトコアとして固有の分周回路と FPGA 内部のハードウェア回路の動作クロックとして提供されます。分周された周波数 16MHz は、チップ 2 とチップ 3 の動作クロックであり、分周された周波数 20MHz は、チップ 1 とチップ 4 の動作クロックです。クロック分布は、以下の図 4 に表示されています。

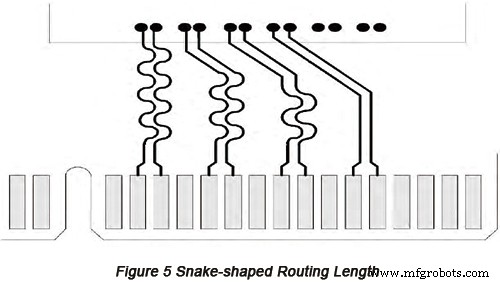

PCIE スロットと PC 間の高速信号伝送は、信号の完全性に関する問題を回避するために、差動ペア ルーティングの方法で高速暗号化カードによって実装されます。一般に、グランド線は差動ペア信号間に配置されません。そうしないと、差動ペア信号間のカップリング効果が破壊されます。差動ペア信号の配線後、PCB 高速信号の周囲に銅を配置し、回路の EMI 能力を向上させるためにグランド ワイヤで完全に埋められた予備スペースを確保します。 PCB ルーティングの鍵は、差動ペアの対称性を維持することです。差動ペアの長さに互換性がない場合、データの読み取りと書き込みの精度が影響を受け、データ転送速度が低下します。同一期間内のデータ読み取りのシステムの有効性を保証するには、差動信号間の遅延差を許容範囲内に維持し、配線長を厳密に同じにする必要があります。したがって、スネーク型ルーティングを適用して、時間遅延を調整することでこの問題を解決できます。この設計では、通信は PCIE と暗号カードを介して PC によって実装され、高速信号の送受信は、25mil 以内に制御された PCB ルーティングの長さを持つ差動ペア信号によって実装されます。蛇の形をした配線の長さのマッチング図を図 5 に示します。

役立つリソース

• 高品質の PCB を設計する方法

• SMT 製造に影響を与える PCB 設計要素

• 組み込みアプリケーション システムにおける高速 PCB 設計に関する研究

• 微分等尺性処理と高速 PCB 設計のシミュレーション検証

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術