高速 PCB 設計の差動アイソメ処理とシミュレーション検証

信号に対する相対遅延の影響

差動信号線で伝送される信号には、信号の差動モード成分とコモンモード成分が含まれています。

差動信号の量は、式 Vdiff に従う 2 つの信号間の差を指します。 =V1 - V2 .コモンモード信号の量は、次の式の 2 つの信号の合計の半分を指します。  .したがって、単一のラインの電圧変化は、ディファレンシャル モード信号とコモン モード信号に同時に影響を与えます。次に、グラフ ソフトウェアを使用して関数図を作成し、ディファレンシャル モード信号とコモン モード信号への影響をそれぞれ調べます。研究の便宜上、シグナルは同じアッパータイムとダウンタイムを持つ台形波形にシミュレートすることで分析できます。

.したがって、単一のラインの電圧変化は、ディファレンシャル モード信号とコモン モード信号に同時に影響を与えます。次に、グラフ ソフトウェアを使用して関数図を作成し、ディファレンシャル モード信号とコモン モード信号への影響をそれぞれ調べます。研究の便宜上、シグナルは同じアッパータイムとダウンタイムを持つ台形波形にシミュレートすることで分析できます。

• 差動信号への影響

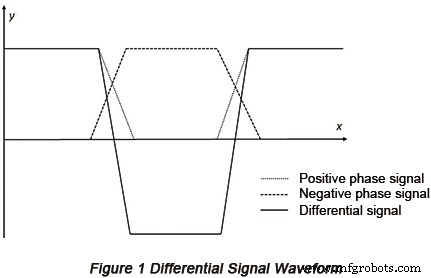

差動ライン ペアの正相端子信号、逆相端子信号、および差動信号を下の図 1 に示します。実線は差動信号波を表します。

正相端子から逆相端子に相配置すると、アップエッジまたはダウンエッジで正相端子信号と逆相端子信号の差が変化し、この変化が位相の変化に伴って変化します。 Tr 上昇時間と下降時間のうち、短い方の時間を表すために使用されます。位相配置が Tr のポイント 2 よりも小さい場合、それを示すことができます。 、信号歪みは比較的小さく、位相配置の増加は微分波形の大きな歪みにつながります。フェーズの配置が Tr を超える場合 、非単調領域が波形上に発生します。ここで、非単調領域は直線です。ただし、実際の信号では、反射のために、非単調領域で大きなアップダウンが発生し、干渉パルスが形成されて誤ったトリガが発生する可能性があるため、これは避ける必要があります。また、位相配置の増加に伴い、差動波形の上端が遅くなり、データ信号の確立時間が不十分になり、クロック信号の保持時間が不十分になる可能性があります。

• コモンモード信号への影響

単一端子信号の位相配置は、差動波形に影響を与えませんが、コモン モード信号の波形を変更します。位相配置が正端子信号で行われると、波形の変化がコモンモード信号に発生します。変動幅は位相配置量に関係していることがわかる。位相配置量がそれぞれ 0.05Tr の場合 , 0.1Tr , 0.2Tr および 0.5Tr 、コモンモードの変動範囲は、元の変動範囲のそれぞれ5%、10%、20%、50%です。フェーズが Tr に増加すると 以上になると変動幅が最大の約100%まで変動します。コモンモード信号の変化は EMI 問題につながる可能性があり、コモンコード信号は多くの条件下で端末で受信されないため、受信端末で反射が形成され、信号リンギングにつながります。したがって、コモンモード信号の変動範囲は可能な限り小さくする必要があります。

結論として、差動ペア間の相対遅延が大きすぎると、信号の誤ったトリガ、信号反射、EMI、およびタイム シーケンスの問題が発生する可能性があります。ただし、相対遅延信号の影響度は、信号 Tr と互換性のあるスケール ファクタに依存します。 .スケール ファクタが 0.05 の場合、差動信号の歪みはほとんど無視できます。ただし、コモンモード信号の場合、スケールファクタが 0.05 の場合、コモンモード信号の電圧変動を約 5% に抑えることができます。そして、全反射状態でも信号線にかかる反射電圧は元の変動の10%程度で、通常は許容値です。したがって、高速 PCB 設計のプロセスでは、ルーティング規則ルールにおける差動信号線の相対遅延を 0.05 Tr に設定できます。 シグナル インテグリティの要件を満たすことができます。

相対遅延カテゴリの決定

上記の分析に基づいて、差分等尺性カテゴリの決定、つまり差分ペアの相対遅延の決定の鍵は、Tr の決定にあります。 差動信号のアッパータイムとダウンタイムの最小値を指します。立ち上がり時間と立ち下がり時間の出力は、実際にはインピーダンスと静電容量の組み合わせの出力です。したがって、負荷なしの立ち上がり/立ち下がり時間は、実際には固有の立ち上がり/立ち下がり時間です。

Tr の値を取得するには、次の 3 つの方法を適用できます。 :

• 立ち上がり/立ち下がり時間は、コンポーネントのマニュアルから直接取得できます。ただし、ほとんどの場合、このパラメーターは提供されません。

• Tr の値。 コンポーネント IBIS (Input/Output Buffer Informational Specification) モデルの Ramp キーワードから取得できます。 Ramp キーワードの立ち上がり/立ち下がり時間パラメータは、通常、50Ω の抵抗に接続された出力ポートで測定されます。これは通常、最終電圧時間の 20% から 80% です。パラメータはパッケージの影響を考慮せずに取得されるため、Tr の値として立ち上がり/立ち下がり時間を使用することは厳密です。 .

• Tr の値 出力信号の最小クロック周波数または最大クロック周波数に基づいて見積もることができます。ほとんどの高速デジタル システムでは、分配立ち上がりエッジがクロック周波数の約 10% であるため、Tr の値は 式に基づいて提供される最小クロック周期 Tclk で推定できます:Tr =Tclk x 10%.

パッケージの寄生パラメータまたはコンポーネントの負荷により、トランジスタの固有の立ち上がり/立ち下がり時間が大幅に遅くなるため、クロック周期で得られる推定値は通常厳密です。

実際の作業では、ほとんどの場合、回路設計者は Tr の情報を提供しません。 ディファレンシャル アイソメトリック コントロールに関してあいまいな要求しか受けない PCB レイアウト エンジニアに。 3 番目の方法は、信号ラインで最高のクロック周波数が得られる限り、間違いなく PCB レイアウト エンジニアに簡単なスキームを提供します。最も高いクロック周波数は、回路設計者にとって最も信頼できる設計パラメータと見なされており、通常、PCB 設計の開始時に PCB レイアウト エンジニアに提供されます。

3 番目の方法は、通常、下の表に示すように、差動ペア間の相対遅延制御カテゴリ内の基準値のリストにつながります。

| クロック周波数/ns | クロック周波数/MHz | 相対遅延カテゴリ/ps | 伝送線路の長さ/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

シミュレーション検証

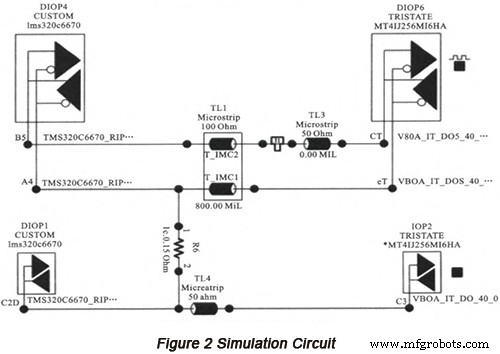

TSM320 と MT41J256M16 間の DQS (データ ストローブ) 差動信号を例にとると、ケイデンス シミュレーション ソフトウェアを適用して DOS 信号を DRR3 メモリに送信し、メモリ制御チップをシミュレートし、データ信号確立保持時間への影響を分析し、上記の分析を検証します。シミュレーション回路を下の図 2 に示します。

図 2 に基づくと、出力ピンの基準電圧は 1.5V です。メモリ制御チップは、800mil の伝送ラインで ODT (On-Die Termination) モードを介してメモリ チップと直接接続されます。差動インピーダンスは 100Ω、シミュレーション クロック周波数は 800MHz です。差動ペアの不一致現象をシミュレートするために、50Ωの伝送ラインが DQS 正相端子に直列に接続されています。等尺性差動の状況では、50Ω の単一端子伝送線路の長さは 0mil です。

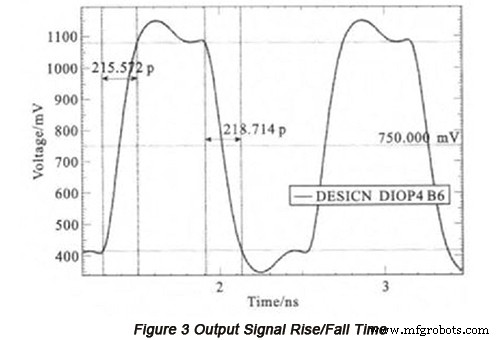

差動アイソメトリック回路に対してシミュレーションを行います。図 3 は、差動信号の正相端子での出力信号を示しています。測定によると、立ち上がり時間は約 216ps、立ち下がり時間は 219ps であるため、最小立ち上がり/立ち下がり時間 Tr 216ps のはずです。

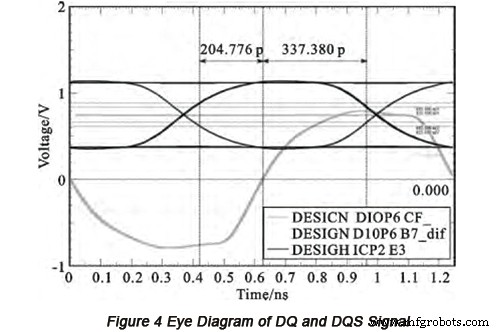

図 4 は、確立時間 205ps、保持時間 337ps でのシミュレーションによるデータ信号 DQ とゲーティング信号 DQS のアイ ダイアグラムです。シミュレーションおよびデータマニュアルに基づく DQS および DQ 信号のターンオーバーレートによれば、受信端末によるデータ信号の最小確立時間は 85ps、最小保持時間は 95ps である必要があります。したがって、最小確立時間は 120ps、保持時間は 242ps と過大評価されます。

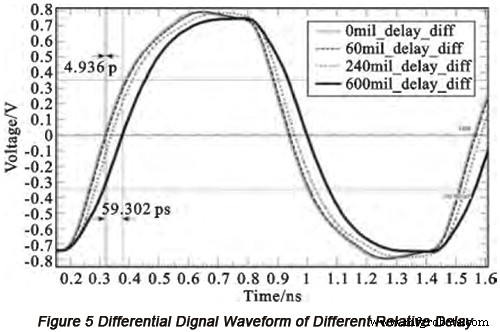

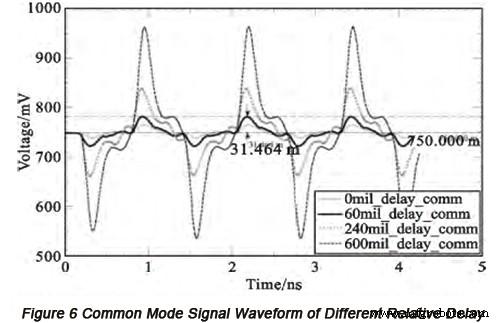

0.05Trの存在状況 位相配置、0.2Tr 位相配置と 0.5Tr 正相端子での位相配置を考慮する必要があります。回路は、それぞれ 60mil、240mil、および 600mil に設定された単一端子伝送線路長でシミュレートできます。 4 回のシミュレーションによる差動信号波形とコモンモード信号波形を図 5 と図 6 に示します。

図 5 に基づくと、相対遅延が 0.05Tr のときに歪みが最小になります。 および 0.2Tr 行われる。特に相対遅延が 0.05Tr の場合 、差動信号から差動信号波形への約 5ps の配置のみを相対的な遅延なしで行うため、データ信号確立オーバー測定は約 5ps 増加し、ホールドオーバー測定時間は 5ps 減少します。ホールドオーバー測定時間は減少しますが、ホールド時間 242ps に対してこの配置量は非常に少ないです。時系列は回避できます。相対遅延が 0.5Tr の場合 、DQS信号波形の配置は約60psに達しています。この配置はまだ過大評価の範疇ではありますが、十分に注意してください。

図 6 に基づくと、位相配置の増加は、波の明らかな周期的変動と範囲の漸進的な増加につながります。相対遅延がそれぞれ 0.05Tr の場合 , 0.2Tr および 0.5Tr 、コモンモード信号の測定されたピーク値は、それぞれ61mV、176mV、および430mVであり、そのうちの最高値は最低値の7倍です。最大の変動幅はそれぞれ 4.3%、12%、29% です。

結論として、シミュレーション結果は、数学関数ダイアグラム解析によって得られた結果と互換性があります。差動ペア間の相対遅延が 0.05Tr 未満の場合 、シグナルへの影響は非常に小さいです。

出力端子での出力信号の最小クロック周期は、相対遅延制御カテゴリを推定するために適用されます。コンポーネント マニュアルに基づくと、コンポーネントの最小クロック周期は 1.25ns で、クロック周波数は 800MHz です。表 1 によると、相対遅延は 35mil の伝送ライン長で 6.3ps 以内に制御する必要があります。どうやら、この値は 0.05Tr の相対遅延のコントロール カテゴリよりもはるかに小さいです。 シミュレーションを通して。したがって、推定相対遅延制御カテゴリは比較的保守的であり、シミュレーション結果よりも具体的です。

役立つリソース

• 組み込みアプリケーション システムにおける高速 PCB 設計に関する研究

• 高速 PCB のイメージ プレーンの設計方法

• シグナル インテグリティに関する高速 PCB 設計の課題とその解決策

• OrCAD PSpice を使用した PCB シミュレーション

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術