原子層堆積ZnO電荷トラッピング層を備えたアモルファスIn–Ga–Zn–O薄膜トランジスタメモリの電圧極性依存プログラミング動作

要約

アモルファスIn–Ga–Zn-O(a-IGZO)薄膜トランジスタ(TFT)メモリは、将来のシステムオンパネルアプリケーションで多くの関心を集めています。ただし、通常、消去効率は低くなります。この記事では、原子層が堆積したZnO電荷トラップ層(CTL)を備えたa-IGZOTFTメモリの電圧極性に依存するプログラミング動作を調査します。手付かずのデバイスは、正のゲートバイアス下だけでなく負のゲートバイアス下でも電気的にプログラム可能な特性を示します。特に、後者は前者よりもはるかに高いプログラミング効率を生み出すことができます。 +13 V /1μsのゲートバイアスパルスを印加すると、デバイスはしきい値電圧シフト(ΔV th )を示します。 )2Vの;およびΔV th -13 V /1μsのゲートバイアスパルスの場合、は-6.5Vと同じ大きさです。 12 V / 1 msプログラミング(P)および-12 V /10μs消去(E)の場合、10 3 で最大7.2Vのメモリウィンドウを実現できます。 P / Eサイクルの。 O 2 でアニーリングされたZnOCTLを比較することによって またはN 2 堆積したままの状態で、酸素空孔(V O )関連の欠陥は、TFTメモリデバイスのバイポーラプログラミング特性を支配します。正のゲート電圧でプログラミングする場合、電子はIGZOチャネルからZnO層に注入され、単一イオン化された酸素空孔(V O )の深いレベルで優先的にトラップされます。 + )および二重にイオン化された酸素空孔(V O 2+ )。負のゲート電圧でのプログラミングに関しては、ドナーが浅く、チャネルにトンネルバックするため、電子は中性酸素空孔から簡単にトラップ解除されます。したがって、これは、正電荷を持つ追加のイオン化酸素空孔の形成による非常に効率的な消去につながります。

背景

アモルファスインジウム-ガリウム-亜鉛-酸化物(a-IGZO)に基づく薄膜トランジスタ(TFT)は、柔軟で透明な電子システムへの応用のために広く研究されてきました[1,2,3,4,5,6,7 、8、9、10、11、12]。これは、良好な均一性、低い処理温度、可視光の透明性、高い電子移動度など、a-IGZOフィルムのいくつかの特定の特性に起因します[13]。それ以外にも、a-IGZO TFTの不揮発性メモリが提案されており、その不揮発性データストレージ機能により、a-IGZOTFTデバイスの利用範囲が広がります。不揮発性メモリデバイスの典型的なアーキテクチャとして、フローティングゲートa-IGZOTFTメモリが近年集中的に研究されています。これまで、誘電体[14、15]、金属ナノ結晶[16、17]、半導体材料[18、19、20、21]など、さまざまな材料がフローティングゲート(つまり、電荷蓄積媒体)として検討されてきました。 。 a-IGZOは天然のn型半導体であり、負のゲートバイアス下のa-IGZO TFTでは正孔反転がほとんど実現されないため、通常、a-IGZOTFTメモリの消去効率は低くなります。言い換えれば、ほとんどのa-IGZO TFTメモリは、チャネルからの正孔注入によって電気的に消去することはできません[14、15、16]。それにもかかわらず、張等。 [21]は、電荷トラップ層(CTL)とチャネル層の両方としてa-IGZOを使用してTFTメモリを製造しました。これは、電気的にプログラム可能で消去可能な特性と、優れたデータ保持を示しました。一方、ユンら。また、異なる組成のIGZOCTLを使用したa-IGZOTFTメモリの特性を調査し、O 2 の増加に伴ってメモリウィンドウが減少することを明らかにしました。 分圧(P O2 )CTLのスパッタリング堆積中[18]。さらに、Bak etal。さまざまな導電率のZnOCTLを備えたa-IGZOTFTメモリの性能を報告し、ZnO CTLのバンドギャップ構造の最適化された電子的性質が、高機能酸化物TFTメモリを実現するための最も重要な要因の1つである可能性があると推測しました[20]。前述の酸化物半導体CTLベースのa-IGZOTFTメモリは優れた電気プログラミング/消去速度を示しますが、上記のデバイスのバイポーラプログラミング特性は報告されておらず、酸化物半導体のCTLにおける異なる電荷の対応するキャプチャプロセスは報告されていません。特に正電荷のトラップについては、まだ明確です。

本研究では、CTLとして原子層蒸着ZnO膜を用いてバイポーラプログラマブルa-IGZOTFTメモリを作製した。 TFTメモリデバイスのバイポーラプログラミング特性を、堆積されたままのO 2 と比較することによって -またはN 2 -アニールされたZnOCTL、ZnO層のさまざまな電荷の捕捉プロセスについて説明しました。酸素空孔に関連する欠陥が、a-IGZOTFTメモリデバイスのバイポーラプログラミング特性を支配していることが明らかになりました。

メソッド

抵抗率が0.001〜0.005ΩcmのP型Si(100)ウェーハは、標準のRCA洗浄プロセスを使用して洗浄され、デバイスのバックゲートとして使用されました。次に、35 nm Al 2 O 3 および20nm ZnO膜は、250°Cおよび200°Cで原子層堆積(ALD)によって連続的に堆積され、それぞれ、TFTメモリのブロッキング層およびCTLとして機能しました。 ZnO膜の二乗平均平方根(RMS)粗さは0.553nmです。続いて、フォトリソグラフィーとウェットエッチングを実行して、ZnOのCTLを定義しました。その後、8 nm Al 2 O 3 トンネリング層はALDによって成長しました。ジエチル亜鉛(DEZ)/ H 2 の前駆体 OおよびTMA / H 2 OはZnOとAl 2 の成長に使用されました O 3 それぞれフィルム。その後、40 nmのa-IGZO膜を、InGaZnO 4 を使用して、室温でチャネル層として高周波マグネトロンスパッタリングによって堆積させました。 目標。次に、幅(W)/長さ(L)が100 /10μmのアクティブチャネルを、フォトリソグラフィーと希釈HClエッチングによって定義しました。 Ti / Au(30 nm / 70 nm)のソースとドレインの接点は、電子ビーム蒸着とそれに続くリフトオフプロセスによって形成されました。最後に、製造されたすべてのデバイスは、O 2 で250°Cでアニールされました。 パフォーマンスを向上させるために5分間。電気的特性評価は、室温で半導体パラメータアナライザ(Agilent B1500A)を使用して実行されました。しきい値電圧(V th )は、ドレイン電流がW / L×10 -9 に等しくなるゲート電圧として定義されます。 A. ZnO膜のキャリア濃度は、室温でのホール効果測定(Ecopia HMS-3000)から抽出されました。

結果と考察

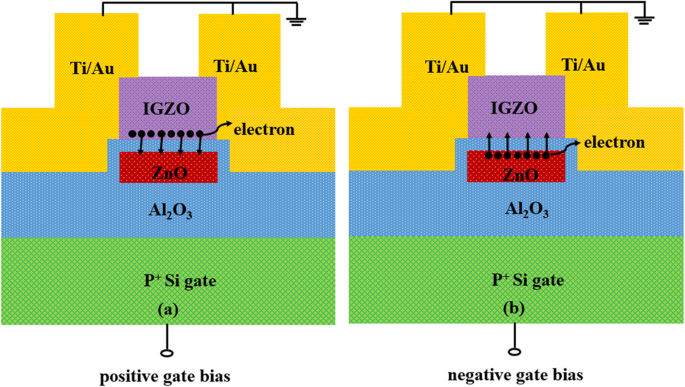

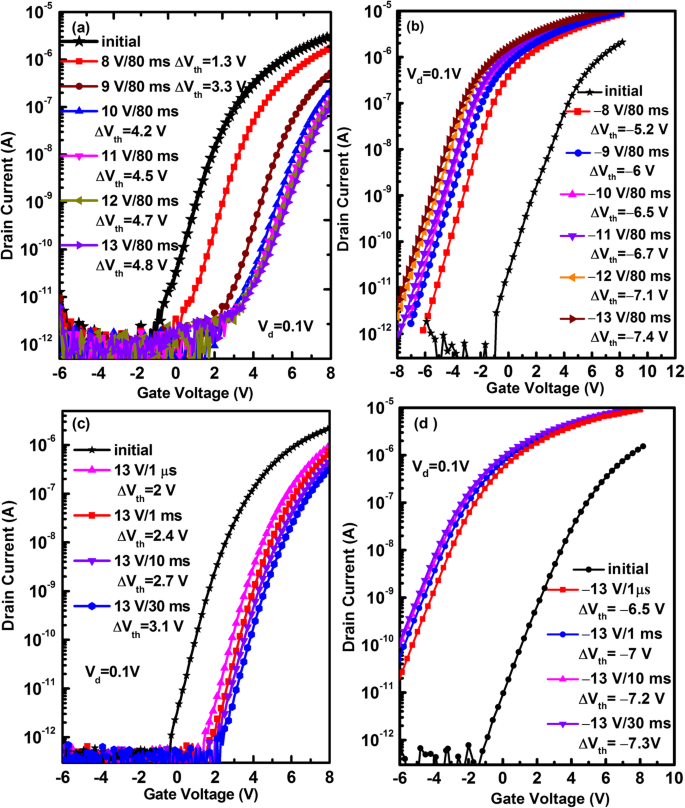

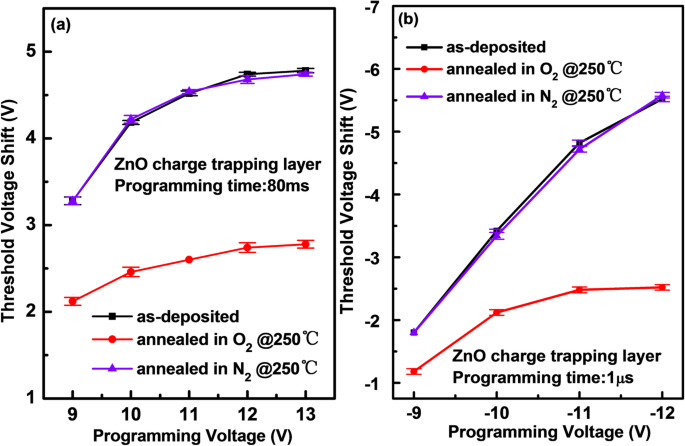

図1に、それぞれ正および負のバイアスプログラミングの下で製造されたa-IGZOTFTメモリデバイスの概略図を示します。電気プログラミング中、電気パルスがバックゲートに印加され、ソース電極とドレイン電極が接地されます。図2は、さまざまな条件下での元のメモリデバイスのプログラミング特性を示しています。手付かずのメモリデバイスの場合、オン/オフ電流比( I on / 私 オフ )1.5×10 7 、7.1cmの電界効果移動度 2 V -1 s -1 、および0.67 V / decのサブスレッショルドスイング(SS)。さまざまな正のバイアスでの80ミリ秒のプログラミングに関して、 I d – V g 曲線は、プログラミング電圧の関数として正のバイアスの方向に徐々に移動します。たとえば、結果のV th 元のデバイスに対してシフトします(ΔV th )図2aに示すように、プログラミング電圧が8から13 Vに増加すると、1.3から4.8 Vに増加し、12Vでプログラミング飽和を示します。このような重要なΔV th n型a-IGZOチャネルからのかなりの電子がZnOCTLに注入されることを示唆しています。また、プログラミング電圧を13Vに固定した場合、ΔV th 図2cに示すように、プログラミング時間を1μsから30 msに延長すると、2Vから3.1Vにゆっくりと増加します。興味深いことに、元のメモリデバイスが負のゲートバイアスでプログラムされている場合、V th 図2bに示すように、負のバイアスへの顕著なシフトを示します。 80ミリ秒の一定のプログラミング時間の場合、ΔV th プログラミングバイアスを-8から-13Vに上げると、-5.2から-7.4 Vに拡大します。元のメモリデバイスが-13Vで1μsプログラムされている場合でも、ΔV th を示すことができます。 図2dに示すように、-6.5Vの大きさです。これは、非常に多くの電子がCTLからトラップ解除されるため、多くの正電荷が残ることを意味します。

正のゲートバイアス( a )の下でプログラムされたa-IGZOTFTメモリデバイスの断面概略図 )および負のゲートバイアス( b )、それぞれ。

a-IGZOTFTメモリデバイスとプログラムされた a の伝達曲線 さまざまな正のゲートバイアスで80ミリ秒の一定時間、 b さまざまな負のゲートバイアスで80ミリ秒の一定時間、 c さまざまなプログラミング時間で13Vで、 d さまざまなプログラミング時間で-13Vで。各図のすべての伝達曲線は同じデバイスで測定され、すべてのプログラミング操作は順番に実行されました。

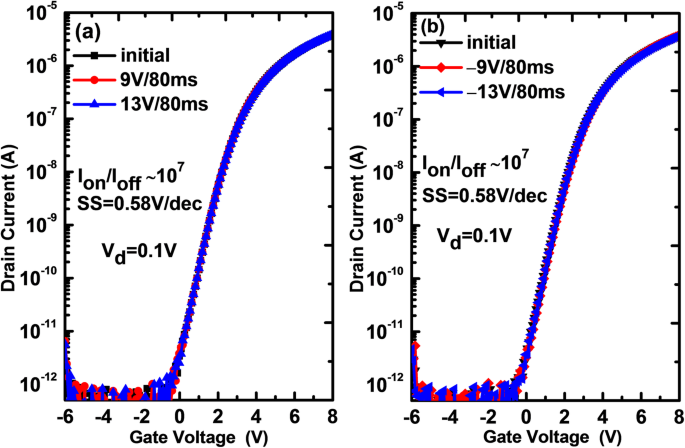

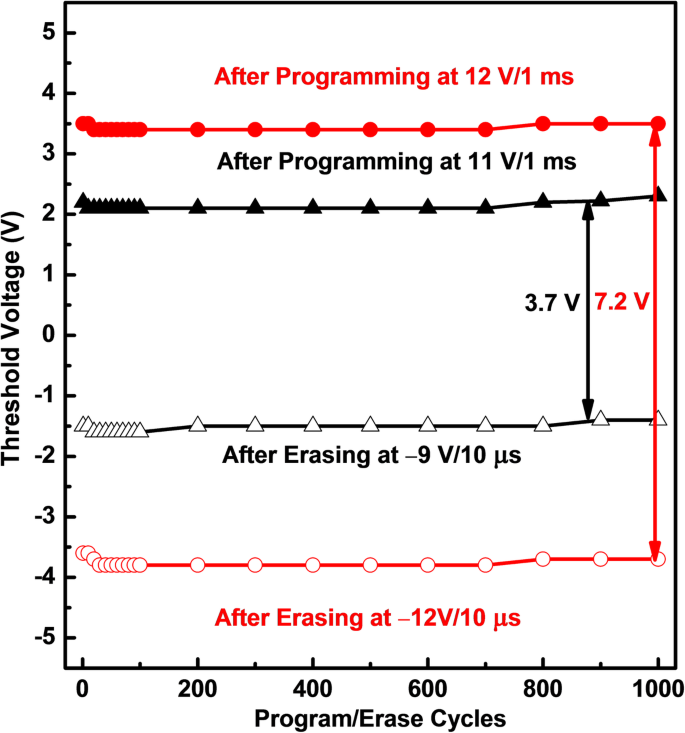

ZnO層の電荷トラップ効果を理解するために、比較用の制御デバイスとして、ZnOCTLを含まないa-IGZOTFTも製造しています。図3は、それぞれ異なる正バイアスと負バイアスでプログラムされた場合の制御デバイスの伝達特性を示しています。デバイスは識別可能なΔV th を示さないことがわかります。 プログラミング電圧の極性と振幅に関係なく。これは、前述の明確なΔV th メモリデバイスの場合は、ZnOCTLに帰属する必要があります。一方、IGZOは天然のn型半導体であるため、IGZOチャネル内の電子は正のゲートバイアス(例:。)の下でZnOCTLに容易に注入できることに注意してください。 、+ 9 V)。しかし、デバイスのゲート電極に負のプログラミングバイアスをかけると、a-IGZOチャネルが空乏化する傾向があり、正孔伝導はほとんど達成されません[15]。この場合、デバイスはチャネルからの正孔注入を介してプログラムすることはできません。したがって、電気的プログラミングの独自の可能性は、元のZnOCTL内の固有電子のトラップ解除によって実現されます。実際、私たちの実験結果は、デバイスが負のゲートバイアスの下で簡単にプログラムできることを示しています。図2dを参照してください。図4は、プログラミング/消去(P / E)サイクルの関数としてのメモリの耐久特性を示しています。このデバイスは、10 3 で3.7Vのメモリウィンドウを示します。 11 V / 1msのプログラミングと-9V /10μsの消去の場合のP / Eサイクルの変化。さらに、10 3 で最大7.2Vのメモリウィンドウを実現できます。 12 V / 1msのプログラミングと-12V /10μsの消去に関するP / Eサイクルの割合。表1に、さまざまなa-IGZO TFTメモリのプログラミング特性と消去特性を比較します[14、22、23]。他のデバイスと比較して、私たちのデバイスは、プログラミング効率の顕著な優位性にもかかわらず、より低いバイアス(-12 V)およびはるかに短い時間(10μs)の下でもはるかに高い消去効率を示します。

a-IGZOTFTデバイスとプログラムされた a の伝達曲線 異なる正のゲートバイアスで80msの一定時間および b さまざまな負のゲートバイアスで80ミリ秒の一定時間

P / Eサイクルの関数としてのa-IGZOTFTメモリデバイスの耐久特性

元のZnOCTLからデトラップされた電子の起源を明らかにするために、さまざまな処理済みZnOCTLをa-IGZOTFTメモリデバイスで比較します。図5に△V th のプログラミング電圧依存性を示します。 異なるZnOCTLを備えたデバイス用。堆積されたままのメモリデバイスとN 2 -アニーリングされたZnOCTL、結果として生じるΔV th 電圧の極性にもかかわらず、プログラミング電圧を上げると同様の増加傾向を示します。ただし、O 2 を備えたメモリデバイスの場合 -アニールされたZnOCTL、ΔV th の絶対値 は、同じプログラミング条件下で大幅な減少を示しています。たとえば、ΔV th の絶対値です。 13 V / 80msおよび-12V /1μsのプログラミングパルスの場合、それぞれ2Vおよび3V減少します。さらに、O 2 では飽和プログラミング動作が観察されます。 -正および負のゲートバイアスの場合、アニールされたZnOCTL。これは、CTL内の限られたトラップに起因する必要があります。一言で言えば、O 2 でのポストアニーリング 250°Cでは、ZnO膜のトラップ中心の数が減少するため、電荷トラップ能力が低下します。

a の関数として、さまざまな処理済みZnO電荷トラップ層を備えたa-IGZOTFTメモリデバイスのしきい値電圧シフト 80msの一定のプログラミング時間と b の正のプログラミング電圧 1μsの一定のプログラミング時間に対する負のプログラミング電圧。各条件について、5つのデバイスが測定されました。

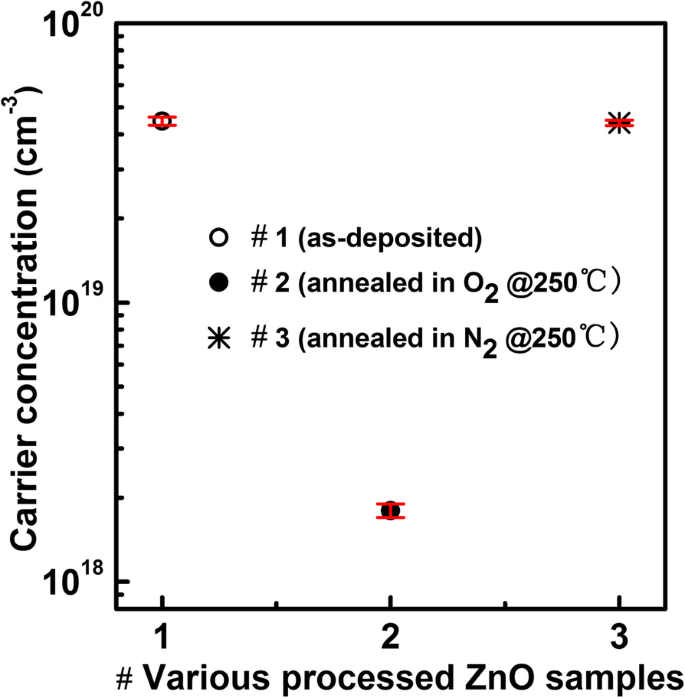

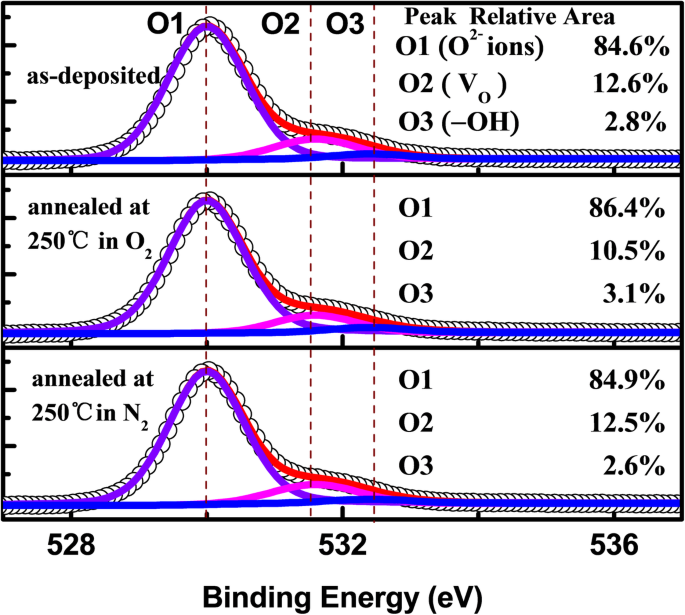

ポストアニーリングがZnO膜の特性に与える影響を調査するために、堆積および処理されたままのZnO膜は、ホール効果測定とXPSによって特徴付けられます。図6に示すように、N 2 でアニールされたZnO膜 250°Cでのキャリア濃度は4.4×10 19 cm -3 、これに非常に近い(4.5×10 19 cm -3 )堆積したままのZnO膜の;ただし、O 2 でアニールされたZnO膜 250°Cでは、キャリア濃度の著しい低下が見られます。これは、1.8×10 18 に相当します。 cm -3 。 n型ZnO半導体膜の固有のドナーは酸素空孔であると報告されています[24]。クォンらまた、ALDZnO膜のO / Zn原子比は、堆積温度を70から130°Cに上げると、0.90から0.78に徐々に減少することも報告されています[25]。これは、ALDZnO膜に酸素空孔が存在することを示しています。したがって、O 2 -アニーリングによって引き起こされるキャリア(電子)濃度の低下は、ZnO膜の酸素空孔の減少に関連しているはずです。さらに、堆積されたままのZnO膜とN 2 でアニールされたものの高分解能O1sXPSスペクトル またはO 2 図7に示すように、デコンボリューションされた3つのピークは、O 2- に対応する530.0、531.6、および532.4eVを中心としています。 Zn 2+ と結合したイオン それぞれ(O1)、酸素空孔(O2)、および化学吸着された酸素元素(–OHなど)(O3)[26]。堆積したままのZnO膜と比較して、O 2 でのポストアニーリング O2の相対パーセンテージが2.1%減少します。それにもかかわらず、N 2 でアニールされたZnO膜の場合 、O2の相対的な割合はほとんど変わりません。これらの結果は、O 2 アニーリングは、ZnO膜の酸素空孔を不動態化できますが、N 2 アニーリングはできません。これにより、酸素空孔とキャリア濃度の相関関係がさらに確認されます。

堆積したままのZnO膜と異なる条件下でアニールされたZnO膜のキャリア濃度。

堆積したままのZnO膜とO 2 で250°Cでアニールしたものの高分解能O1sXPSスペクトル およびN 2 、 それぞれ。 O1とO2はO 2- に対応します Zn 2+ と結合したイオン それぞれ、酸素空孔。 O3は、化学吸着された酸素元素(–OHなど)に起因します。意図せずに表面の汚染物質を除去するために、すべてのサンプルをその場でのArイオン衝撃でエッチングしました

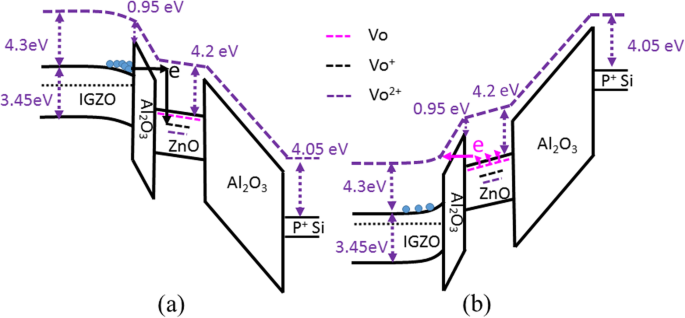

前述の実験結果に基づいて、元のメモリデバイスのプログラミング特性は、ZnOCTLの酸素空孔関連欠陥の集中によって支配されていると結論付けることができます。言い換えれば、ZnO膜の酸素空孔は、主に正電荷と負電荷をトラップするためのトラップ中心として機能します。 ZnOの酸素空孔関連の欠陥には、中性酸素空孔(V O )が含まれると報告されています。 )、単一イオン化酸素空孔(V O + )、および二重にイオン化された酸素空孔(V O 2+ )、そのエネルギー準位は、ZnOの伝導帯の最小値よりもそれぞれ0.02〜0.04、0.3〜0.45、および0.61 eV下にあります[27、28]。この場合、堆積したままのZnO膜は高い電子濃度を示すため、浅いドナーとして機能する中性酸素空孔の濃度は、イオン化酸素空孔の濃度よりもはるかに高くなるはずです(V O + およびV O 2+ )。正のゲートバイアスでのプログラミングに関して、a-IGZOチャネルの蓄積層の電子は、Fowler-Nordheim(FN)トンネリングメカニズムによってZnO層に注入されます。これは、増分ΔV th <によって示されます。 / sub> 図2aのプログラミング電圧を強化します。一方、これらの電子は、V O の深いレベルで優先的にトラップされると予想されます。 + およびV O 2+ 、図8aに示すように。これにより、V th がシフトします。 正のバイアスに向かって。もちろん、電子をトラップする酸素空孔に加えて、他の欠陥も電子を捕獲する可能性があります。しかし、私たちの実験データは、図5に示すように、酸素空孔が電子トラップと正電荷の捕捉に重要な役割を果たすことを示しています。負のプログラミング電圧では、元のZnOCTLの中性酸素空孔が主に電子を供与します。最も浅いエネルギー準位[27、28]、および放出された電子はZnO CTLからチャネルにトンネルし、正に帯電した酸素空孔(V O など)の形成につながります。 + )、図8bに示すように。これにより、V th がシフトします。 図2bに示すように、負のバイアスの方向に。さらに、中性酸素空孔の濃度が高いため(V O )ZnOの堆積されたままのCTLでは、元のメモリデバイスは、正のゲートバイアスの下よりも負のゲートバイアスの下ではるかに高いプログラミング効率を示します。たとえば、ΔV th の絶対値 -13 Vで1μsプログラミングした後は6.5Vになります(図2dを参照)。ただし、ΔV th 13 Vで1μsプログラミングした後の2Vに等しくなります(図2c)。これは、前者が主にV O の濃度によって決定されるためです。 、後者はV O の濃度によって支配されます + およびV O 2+ 。

a でプログラムされたa-IGZOTFTメモリデバイスのエネルギーバンド図 正のゲートバイアスと b それぞれ負のゲートバイアス。 V o 、V o + 、およびV o 2+ それぞれ、中性酸素空孔、単一イオン化酸素空孔、および二重イオン化酸素空孔を示します

結論

要約すると、原子層が堆積したZnOCTLを備えたバイポーラプログラマブルa-IGZOTFTメモリを製造しました。正のゲートバイアスの下でのプログラミングと比較して、負のゲートバイアスの下でのプログラミングははるかに高い効率を生み出すことができます。これは、電圧極性に依存するプログラミング中に、さまざまな酸素空孔欠陥が発生するためです。つまり、V O の深い欠陥 + およびV O 2+ 正バイアスプログラミング中の電子トラップ、およびV O の浅い欠陥に重要な役割を果たします 主に負のバイアスプログラミング中に電子を供与し、正に帯電した酸素空孔を生成します。

データと資料の可用性

この原稿の結論を裏付けるデータセットは、原稿に含まれています。

略語

- a-IGZO:

-

アモルファスインジウム-ガリウム-亜鉛-酸化物

- ALD:

-

原子層堆積

- CTL:

-

電荷トラップ層

- TFT:

-

薄膜トランジスタ

- XPS:

-

X線光電子分光法

ナノマテリアル

- 界面層の設計によるZnO膜の表面形態と特性の調整

- 超循環原子層堆積によるZnO膜のフェルミ準位調整

- CdSe QD / LiF電子輸送層を備えた高効率の逆ペロブスカイト太陽電池

- 後部に黒色シリコン層を備えた結晶シリコン太陽電池の調査

- エッチングストッパーナノレイヤーを介したクリーンなインターフェースプロセスを使用したa-IGZOTFTデバイスのパフォーマンスの向上

- アルゴンプラズマ処理によるZnOの挿入による金属とn-Ge間の接触抵抗の低減

- 不揮発性メモリのスイッチング特性に及ぼす二分子膜CeO2-x / ZnOおよびZnO / CeO2-xヘテロ構造と電鋳極性の影響

- 原子層に堆積したZnO /β-Ga2O3(\(\ overline {2} 01 \))ヘテロ接合でのエネルギーバンドの調査

- 強化されたデュアルゲートと部分的なP埋め込み層を備えた超低比オン抵抗横方向二重拡散金属酸化物半導体トランジスタ

- 高いオン/オフ比と極性切り替え可能な光伝導性を備えたSnSe2電界効果トランジスタ

- Python - C による拡張プログラミング