高度なCMOSBEOLプロセス用のプラズマ誘起帯電効果の広範囲検出器

要約

この作業では、高度なCMOS BEOLプロセス中にウェーハ全体で発生する可能性のあるプラズマ損傷を監視するために、検出範囲を広げるための修正プラズマ誘導帯電(PID)検出器を提案しました。拡張コンデンサを使用したプラズマ誘起損傷パターンの新しいアンテナ設計を調査します。新しいPID検出器を採用することにより、検出器の最大充電レベルが向上しました。

はじめに

近年、半導体プロセス技術の進化により、大規模集積回路の限界寸法が縮小され続けています[1,2,3]。高度なFinFETロジックプロセスは、多機能でより強力なSiチップでより密集したトランジスタを実現するために、より複雑になっています。プラズマによって強化された反応性イオンエッチングステップ[4、5]は、高充填密度回路に不可欠な高アスペクト比構造を実現するための高度なナノスケールプロセスでは避けられません[6]。 45 nmを超えるCMOSテクノロジノードの場合、トランジスタゲートは、二酸化ケイ素を使用する従来のポリシリコンゲートからhigh-kメタルゲートスタックに変更されました[7、8]。この変更により、デバイスはプラズマによる損傷を受けやすくなり、high-k誘電体層に予期しない潜在的な損傷をもたらす可能性があります。 [9]。 FinFETの最先端の製造プロセスでは、エッチング、堆積、洗浄プロセスなどの多数のRFプラズマステップが避けられず、プラズマによって誘発される充電イベントの頻度が高くなります[10]。金属構造に正と負の両方の帯電が発生する可能性があります。これらの電荷は、既存の金属線で作られた導電経路を介して、接点を介して流れるため、回路の脆弱な部分、特にトランジスタのゲート誘電体を介した望ましくない放電は、重大な信頼性の懸念につながる可能性があります。たとえば、ドライエッチングのステップでは、衝突するイオンやスパッタされた材料を反応面で散乱させると、バルクフィンにさらに多くの欠陥が生じます[11、12]。回路に不可逆的な損傷をもたらすプラズマ充電イベントを回避するために、金属構造のサイズを制限する設計規則が示されています。 PIDを軽減する別の例には、プラズマ充電電流を敏感な回路から遠ざける可能性のある保護ダイオードの使用が含まれます[13]。 In-Situ蒸気発生(ISSG)ゲート酸化物の導入により、プラズマ損傷に対する耐性が向上したことが報告されています[14]。さらに、チャンバーのトリミングとPECVD-Ti堆積プロセスの変更により、プラズマによる損傷が軽減されることもわかりました[15]。ただし、これらの方法のほとんどは、回路設計の柔軟性または処理のトレードオフに望ましくない制限をもたらします。

従来、プラズマ誘起損傷(PID)レベルを監視するためにオンウェーハテストパターンが使用されてきました[16]。オンウェーハPIDを監視するために最も一般的で広く使用されているパラメータは、大きなアンテナ構造を持つトランジスタゲートの故障までの時間(TDDB)特性です。ゲート誘電体の潜在的な損傷は、電圧または電流のストレステストでゲート誘電体層の劣化を測定することで明らかになります。したがって、これらのパターンは、プラズマプロセスに関するリアルタイムのフィードバックを提供することはできません[17]。私たちの以前の研究では、オンウェーハプラズマ誘起帯電効果検出器が高度なFinFET技術で実証されています。 PID検出器は、容量結合構造を使用して、フローティングゲートに応答を誘導します[18、19、20]。したがって、従来のPID検出器のようにゲート誘電体層に損傷を与えることはありません。これらの新しい検出器では、シフトするI–V曲線を測定して、アンテナゲートの電荷の強度、持続時間、および極性の両方を調べます。特定の記録部位でのプラズマ強度が臨界レベルを超えると、これらの検出器は飽和効果を受ける可能性があることがわかっています。 PID検出器のダイナミックレンジを拡張するために、この作業では新しいアンテナゲートの設計が調査され、検出範囲の拡大が成功裏に実証されました。

メソッド

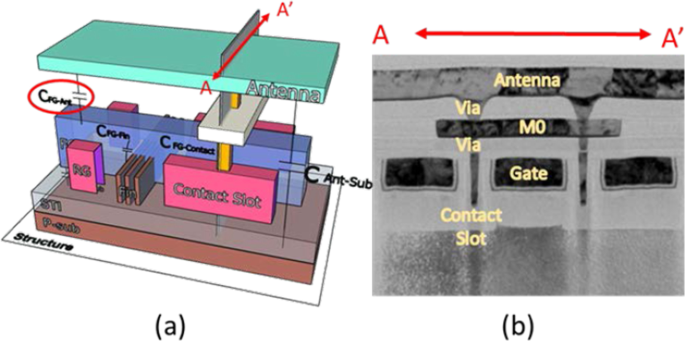

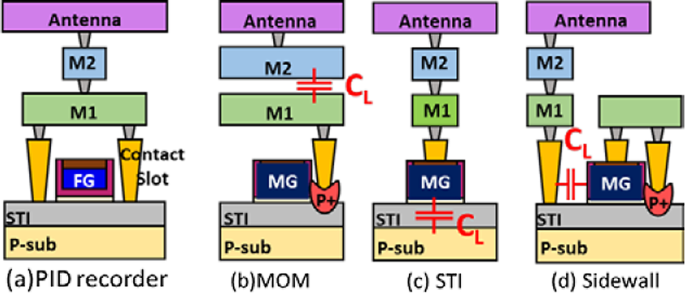

アンテナノードに寄生コンデンサが接続されたプラズマ誘起損傷(PID)検出器の3D概略図を図1aに示します。 PID監視構造とは異なり、この検出器は長い接点スロットを利用してフローティングゲートのアンテナ電圧を結合します。断面TEM写真を図1bに示します。図に示すように、電荷を収集する接点スロットはフローティングゲートに容量結合されています。

a 以前に報告されたその場PID検出器とアンテナコンデンサの3Dイラストは、この構造で強調されています。 b PID検出器のTEM写真。この検出器のゲート長は140nmです

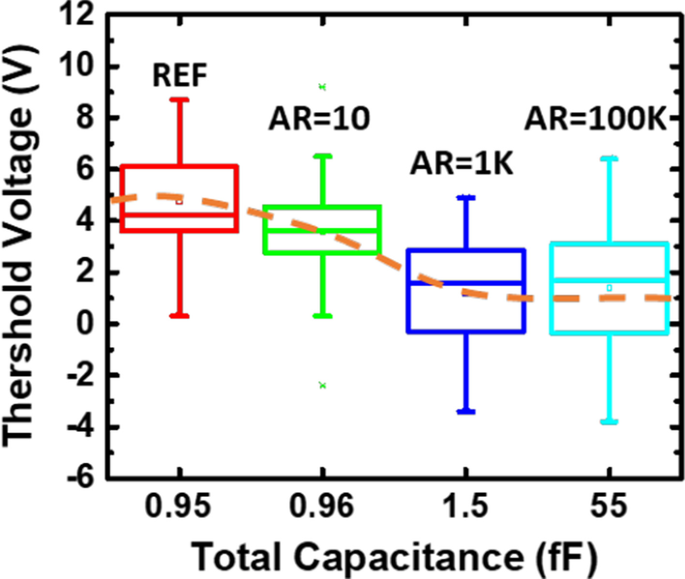

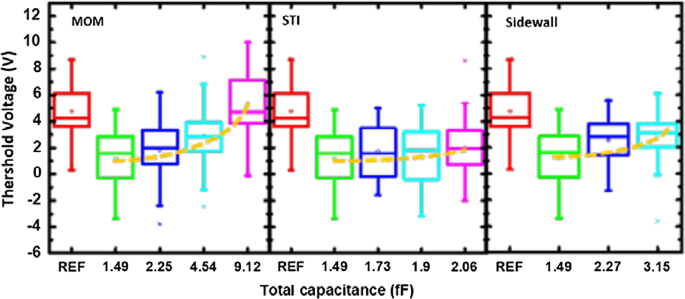

図2は、12インチウェーハ全体でこれらの検出器から記録されたしきい値電圧分布を比較しています。負のしきい値電圧シフトは、負の電荷がアンテナに収集され、正の電荷がフローティングゲートに引き込まれ、負のしきい値電圧シフトが発生したことを示します。アンテナ面積が増加すると、総静電容量が増加するとアンテナ全体の電圧が低下するため、 V のシフトが小さくなることがわかります。 t 。

アンテナのサイズが異なるサンプルのしきい値電圧範囲、および対応するアンテナの総静電容量

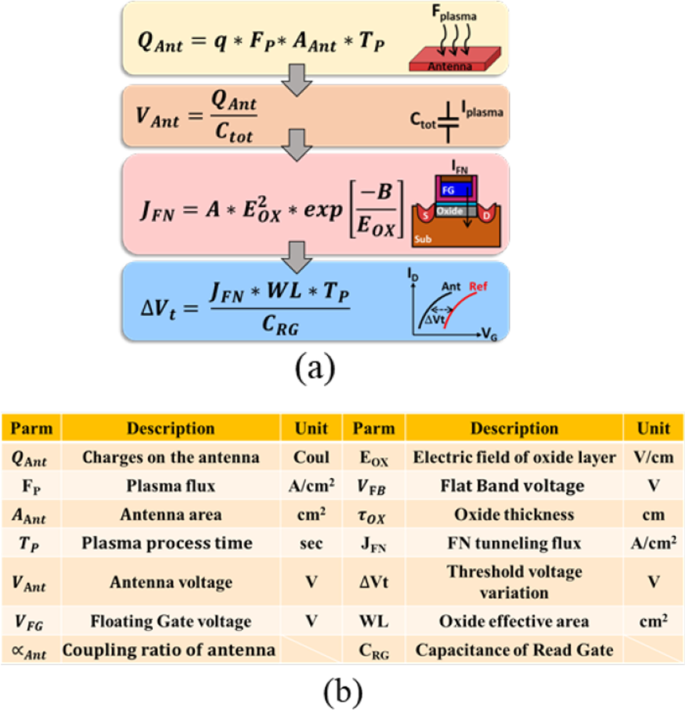

ここで、図3aに、PID検出器の基本的な動作原理を説明するフローチャートの概要を示します。プラズマ電荷として( Q Ant )はアンテナに収集され、アンテナゲートの電位 V Ant 、 不定。 V Ant 次に、フローティングゲート(FG)に結合され、FGへの電子のトンネリングまたはFGからの電子のトンネリングを促進します。プラズマ処理後、 V t これらの検出器のうち、 Q の極性に基づいて、より負または正になる可能性があります Ant 。 V t 図3bにリストされているパラメータを使用して、FNトンネリング電流モデルによって計算できます。

a プラズマ電荷からのフローチャート( Q Ant ) V をシフトするためにアンテナに集められます t 。 FNトンネリングモデルに基づく、Δ V t 計算することができます。 b パラメータとその定義のリスト

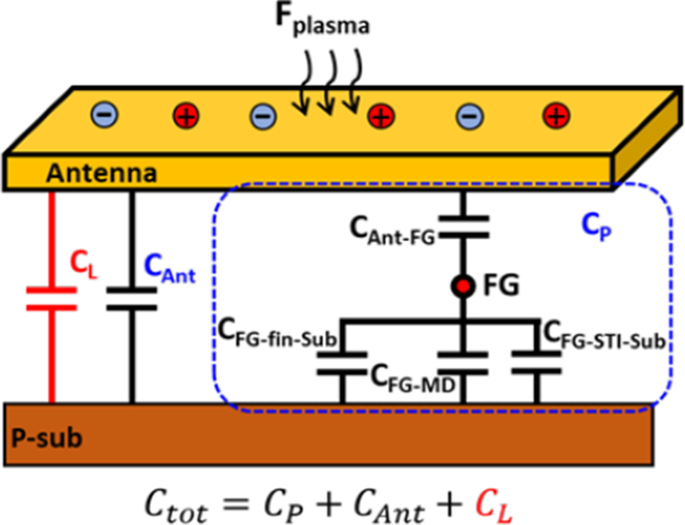

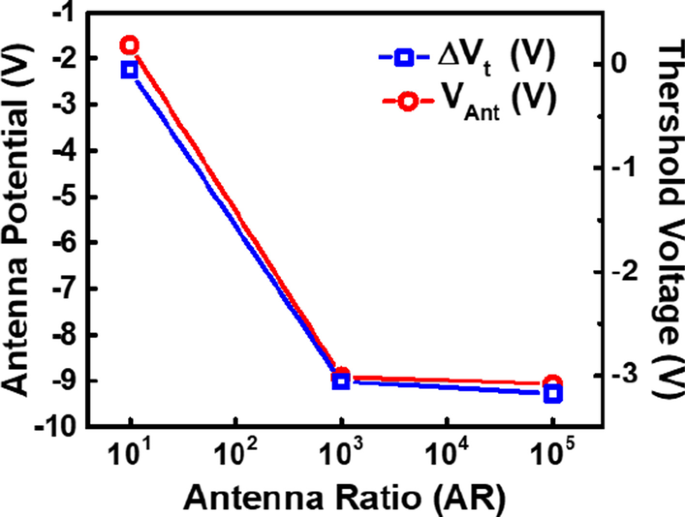

図4は、FGベースのPID検出器で可能なすべての静電容量を示しています。図5から、アンテナ面積が大きくなると、Δ V t 飽和する傾向があります。 V として Ant 最大レベルに達する Q Ant 電圧レベルが高すぎると漏れ始めます。プラズマ磁束レベルが検出器の制限を超えるのを避けるために、アンテナ容量は、総容量に占めるアンテナ容量の割合を減らす可能性のある負荷コンデンサを追加することによって意図的に増加させます。

PID検出器の感度を変更するように設計された追加の負荷コンデンサを使用したアンテナ構造の静電容量の構成。 C P フローティングゲートの全体的な寄生容量です

アンテナ面積が増加すると、しきい値電圧レベルと予測アンテナ電圧レベルの両方がパターンで飽和します

図6aは、以前に報告されたin-situ PID検出器の2D構造を示しており、追加のコンデンサを実現する3つの構造が示されています。それらは、金属層のより大きなオーバーラップ領域を使用して図6bの総静電容量を増加させるMOMコンデンサ、図6cの金属ゲートの長さを調整することによって静電容量を増加させるSTIコンデンサ、および使用するサイドウォールコンデンサです。追加のコンデンサを形成するための金属ゲートと接点のオーバーラップ領域図6d。

a の断面図 その場でのPID検出器、および b によって実現される負荷追加コンデンサを備えたもの MOM、 c STI、および d それぞれサイドウォール

実験結果とディスカッション

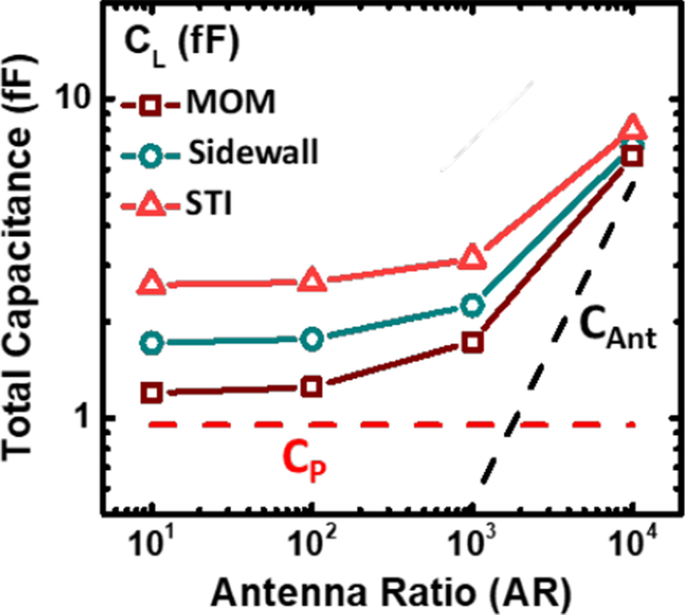

図7は、さまざまなタイプの負荷コンデンサを追加した場合の総静電容量とアンテナ比を比較しています。アンテナ比が1Kを超える場合、総静電容量はアンテナ静電容量によって支配されます。

3種類の負荷コンデンサを追加した場合の総容量とアンテナ比の比較

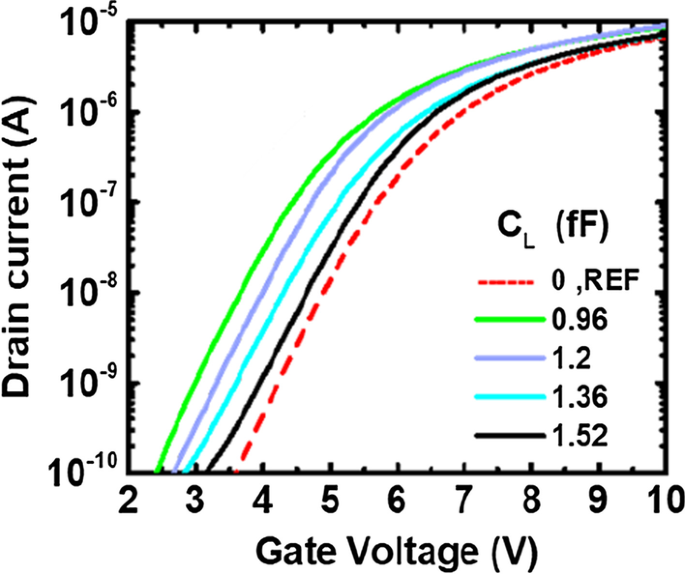

追加された負荷容量がアンテナ容量に匹敵するようになると、総容量は負荷コンデンサの影響を受ける可能性があります。アンテナが収集する電荷の最大量は固定されているため、総静電容量を増やすことにより、Δ V Δ Q によると、減少すると予想されます = C Δ V 。したがって、検出範囲の感度を抑制し、プラズマ充電レベルが元の限界を超えたときの飽和効果を防ぐことができます。異なるSTIコンデンサを備えたAR =10のデバイスのドレイン電流特性を図8で比較します。より大きな負荷コンデンサを追加すると、総容量に占めるアンテナ容量の割合が減少します。同じプラズマ帯電フラックスの下で、一定期間後の総プラズマ帯電はアンテナ面積に比例します。したがって、全体の静電容量が増加すると、 V Ant 低下することが期待され、高いプラズマフラックスレベルの検出を可能にします。図8に示すように、追加の負荷コンデンサを使用したサンプルでは、I-V曲線に小さなシフトが見られます。

AR =10のさまざまなサイズのSTIコンデンサのI–V曲線。外部容量が大きいほど、I–V曲線はリファレンスセルのI–V曲線に近くなります

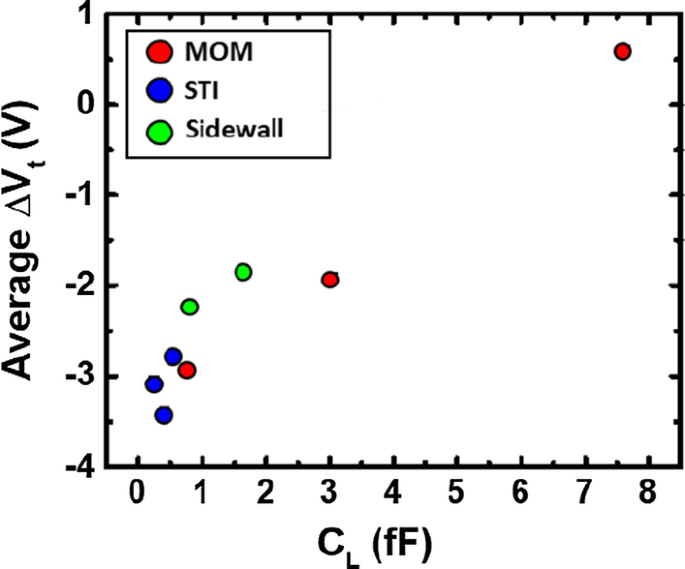

。AR =1 KのサンプルとさまざまなサイズのMOM、STI、およびサイドウォールコンデンサから測定されたしきい値電圧のボックスチャートを図9で比較します。負荷容量を増やすと、平均してしきい値電圧シフトが少なくなります。実験計画では、 C L STI構造では、充電レベルの影響を示すには小さすぎます。図10の比較から、負荷コンデンサを追加する3つの方法でも、プラズマ充電に対する平均応答を効果的に低減できることがわかりました。追加のローディングコンデンサにより、PID検出器の検出範囲を拡大できますが、検出器の感度は低下します。プラズマ充電レベルの広範囲な検出を実現するために、 C のレベルが異なる一連のPID検出器 L ハイエンドとローエンドの両方でプラズマ充電レベルを検出するために、1次元アレイで設計できます。

さまざまなサイズのMOM、STI、およびサイドウォールコンデンサを使用してサンプルで測定されたしきい値電圧が比較されます。すべてのデバイスのARは1Kと同じです

平均Δ V の比較 t 対 C L Δ V である3種類のコンデンサ構造によって実装されます。 t V として定義されます t 検出器セルと参照セルの違い。データは、感度の低下は C として得られることを示唆しています L 増加

結論

この研究では、PID監視検出器のプラズマ誘起充電レベルの検知範囲を拡張するための新しいアンテナゲート設計を調査します。ローディングコンデンサを追加することにより、電荷漏れの影響を受ける高いアンテナゲート電圧を防ぐことができ、より高いレベルの充電レベルをPID検出器に登録することができます。この斬新な設計により、高度なCMOSBEOLプロセスでのプラズマ帯電レベルの検出範囲が効果的に広がります。

データと資料の可用性

該当なし。

略語

- PID:

-

プラズマによる損傷

- V t :

-

しきい値電圧

- Q Ant :

-

アンテナの充電

- V Ant :

-

アンテナ電圧

- MOM:

-

金属-酸化物-金属

- AR:

-

アンテナ比

- C L :

-

負荷容量

- C P :

-

寄生容量

- C Ant :

-

アンテナ容量

ナノマテリアル

- CMOSゲート回路

- Python for ループ

- IBM Researchers Take Home Innovation Prize for Semiconductor Research

- マイクロLEDおよびVCSEL用の高度な原子層堆積技術

- 子宮頸がんにおける抗がん効果を高めるための葉酸受容体を標的としたバイオフラボノイドゲニステインをロードしたキトサンナノ粒子

- MnХFe3−XО4スピネルの構造的および磁気的特性に及ぼす接触非平衡プラズマの影響

- FinFETBEOLプロセスにおけるプラズマ充電効果のリアルタイム検査用のChargeSpliting In Situ Recorder(CSIR)

- BaTiO3 / Nb:SrTiO3エピタキシャルヘテロ接合における強誘電場効果による非対称抵抗スイッチング効果

- 高度なナトリウムイオン電池のアノード材料としてのCuGeO3ナノワイヤの合成と調査

- FinFET CuBEOLプロセスにおける金属間誘電体のプラズマ誘起損傷のテストパターン設計

- リチウムイオン電池のアノードとして使用される麻の茎由来炭素に及ぼす極低温活性化処理の影響