プラズマ化学原子層堆積によるその場で形成されたSiO2中間層を有するHfO2 / Geスタックの界面、電気、およびバンド整列特性

要約

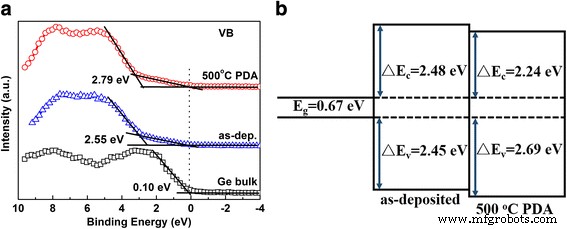

その場で形成されたSiO 2 HfO 2 に導入されました プラズマ強化原子層堆積(PEALD)による中間層としてのGe基板上のゲート誘電体。 HfO 2 の界面、電気、およびバンドアライメント特性 / SiO 2 Ge上のhigh-kゲート誘電体スタックは十分に調査されています。 Si-O-Ge中間層は、その場でのPEALD SiO 2 の間にGe表面に形成されることが実証されています。 堆積プロセス。この中間層は、明らかなHfケイ酸塩の形成なしに、アニーリング中に素晴らしい熱安定性を示します。さらに、GeO 2 を抑制することもできます 劣化。電気的測定では、静電容量に相当する厚さが1.53 nm、漏れ電流密度が2.1×10 -3 であることが示されています。 A / cm 2 V fb のゲートバイアスで アニールされたサンプルでは+ 1Vが得られました。 HfO 2 での伝導(価電子帯)バンドオフセット / SiO 2 PDAがある場合とない場合の/ Geインターフェースは、それぞれ2.24(2.69)および2.48(2.45)eVであることがわかります。これらの結果は、その場でのPEALD SiO 2 高品質のGeベースのトランジスタデバイスを実現するための有望な界面制御層となる可能性があります。さらに、PEALDは、MOCVDよりもはるかに強力な超薄界面制御層堆積技術であることを実証できます。

背景

金属酸化物半導体電界効果トランジスタ(MOSFET)の継続的なスケールダウンにより、SiベースのMOSFETはその物理的および技術的限界に近づいています。ゲルマニウム(Ge)[1、2]やIII-V材料[3–5]などの代替チャネル材料は、最近、高性能ロジックデバイスアプリケーションに大きな関心を集めています。その中で、Geは、本質的に高い正孔キャリア移動度のために、MOSFETのチャネル材料としてシリコンに取って代わる可能性があります[6]。ただし、Ge基板上にhigh-kゲート誘電体を直接堆積すると、多くの場合、高い界面トラップ密度(D it )が発生します。 )およびGeとhigh-k誘電体層の間の不要な界面層の形成[7]。したがって、高速で低電力のGeベースのMOSFETを実現するには、高品質の高品質の k を実現することが非常に重要です。 / Geインターフェース。幸い、SiO 2 の導入など、high-k / Geインターフェースの品質を向上させる多くの方法が報告されています[8]。 [9]、Si [10]、GeO 2 [11]、Al 2 O 3 [12、13]、GeO x N y [14、15]、およびGe基板と高 k の間の界面制御層としての希土類酸化物[16、17] ゲート誘電体。特に、GeO 2 / Ge構造は、優れた界面特性、非常に低い界面状態密度(D it )を備えています。 )1×10 11 未満 cm −2 eV -1 達成することができます[18]。ただし、GeO 2 425°C以上で分解し、水溶性になります。その結果、許容できないD it Ge-MOSコンデンサ(MOSCAP)については常に明らかにされています[6]。幸いなことに、北等。 GeO 2 のキャッピングレイヤーが報告されました GeO 2 を抑制できます 劣化;ただし、キャップ層の材料の選択は非常に重要です[19–21]。たとえば、SiまたはY 2 O 3 HfO 2 よりも効率的に機能します Ge-Oの脱着を遅らせるため。これらの結果は、GeO 2 を抑制するためのhigh-k材料または界面制御層の選択の重要性を示しています。 劣化。中島ほか非常に薄いSiO 2 / GeO 2 物理蒸着(PVD)による二重層は、Geパッシベーション、D it の有望な中間層です。 4×10 11 cm -2 eV -1 ミッドギャップの近くで達成されました[22、23]。 Li etal。 SiO 2 を導入 有機金属化学蒸着(MOCVD)によるGeの中間層、およびSiO 2 中間層は、HfO 2 中のGeの外方拡散を効果的に抑制することができます。 成長とそれに続く堆積後のアニーリングプロセス[9]。したがって、SiO 2 Ge基板の素晴らしい界面制御層になるはずです。ただし、PVDやMOCVDと比較すると、PEALDは、特に極薄の厚さの場合に、はるかに均一なパッシベーション層を提供できます。したがって、PEALDで形成されたSiO 2 高性能Geベースのトランジスタデバイスを実現するための有望な界面制御層である可能性があります。

ここでは、その場でPEALDで形成されたSiO 2 を紹介しました。 HfO 2 に / Geは界面層としてスタックします。 ALD HfO 2 の界面、電気、およびバンドアライメント特性 n型Ge基板上の膜は注意深く調査されています。 SiO 2 PEALDによって界面制御層としてGe基板上に最初に堆積されました。次に、HfO 2 ゲート誘電体は、熱ALDモードによってその場で堆積されました。 N 2 で500°Cで60秒間の堆積後アニーリング(PDA) HfO 2 に対して実行されました / SiO 2 Ge上のhigh-kゲート誘電体スタック。 X線光電子分光分析により、Si-O-Ge中間層とGeO 2 PEALD SiO 2 の間にGe表面に層が形成されます 沈着。このSi-O-Ge中間層は、優れた熱安定性を示すだけでなく、GeO 2 の熱分解を抑制することができます。 。したがって、HfO 2 では良好な電気的特性が達成されました。 / Si-O-Ge / GeO 2 / Geスタック。 MOCVD SiO 2 との比較 中間層、その場でのPEALD SiO 2 大幅に改善された電気的特性を示します。したがって、PEALDは、MOSFET製造の分野で、特に極薄の界面制御層堆積において、MOCVDよりもはるかに強力な技術です。

メソッド

基板には抵抗率0.2〜0.3Ω・cmのN型SbドープGe(100)を使用した。最初に、アセトン、エタノール、イソプロパノール、および脱イオン水中でそれぞれ5分間超音波処理することにより、基板を洗浄しました。次に、HBr溶液を希釈します(H 2 O / HBr =3:1)を使用して、表面の自然酸化物を5分間エッチングしました。湿式化学洗浄後、基板を脱イオン水ですすぎ、純粋なN 2 でブロードライしました。 。その後、基板はすぐにPEALD(Picosun SUNALE TM )に移されました。 R-200)チャンバー。高値の前- k HfO 2 膜の堆積、10サイクルのSiO 2 フィルムは、中間層としてPEALDによって250°Cで堆積されました。1サイクルは、1秒のSiソース注入、10秒のN 2 で構成されていました。 パージ、13.5秒の酸化剤注入、および4秒のN 2 パージ。トリス-(ジメチルアミノ)-シラン(TDMAS)およびO 2 プラズマは、SiO 2 のSi前駆体および酸化剤として使用されました。 それぞれ沈着。 TDMASは室温に保たれました。純粋なO 2 ガス(99.999%)をO 2 として使用しました プラズマ源。プラズマパワーとO 2 ガス流量はそれぞれ2500Wと160sccmでした。 PEALD SiO 2 の成長率 ex situ分光エリプソメトリーにより、約0.7Å/サイクルであると決定されました。次に、厚さ約4nmのHfO 2 フィルムは、熱ALDによって250°Cで40サイクル、その場で堆積されました。1サイクルは、0.1秒のHfソース投与、4秒のN 2 で構成されていました。 パージ、0.1秒H 2 O投与、および4秒N 2 パージ。テトラキス-(エチルメチルアミノ)-ハフニウム(TEMAH)およびH 2 Oは、HfO 2 のHf前駆体および酸化剤として使用されました。 それぞれ沈着。 TEMAHは150°CおよびH 2 で蒸発させました。 Oは室温に保たれた。純粋なN 2 (99.999%)をキャリアガスとパージガスとして使用しました。 PDAはN 2 で実行されました ラピッドサーマルアニーリングを使用して、大気圧下で500°Cで60秒間周囲温度。

フィルムの界面構造と化学的結合は、標準的なAlKα(1486.7 eV)X線源を使用したex situ X線光電子分光法(XPS、Thermo Fisher K-Alpha)によって調査されました。 XPSスペクトルは90°の離陸角度で収集されました。結合エネルギースケールは、Ge 3d 5/2 を使用して較正されました。 29.4eVでピークになります。さらに、XPSスペクトルは、スマートタイプのバックグラウンド減算後にガウス-ローレンツ(G-L)関数に適合しました。面積1.55×10 -4 のPt上部電極 cm 2 HfO 2 の表面に堆積しました 電気測定用のスパッタリング法によるシャドウマスクを使用したフィルム。静電容量-電圧(C-V)および漏れ電流密度-電圧(J-V)の特性は、プローブプラットフォームを備えたKeithley 4200半導体アナライザシステム(カスケードサミット12000B-M)によって測定されました。

結果と考察

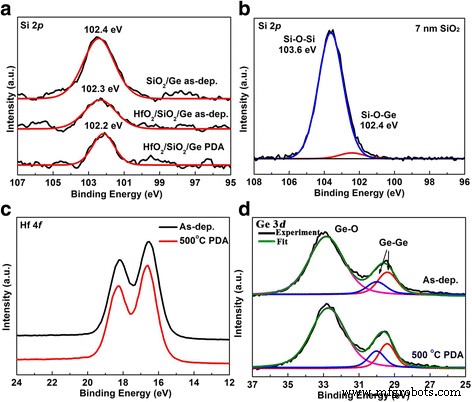

薄いPEALDSiO 2 の場合 (〜0.7 nm)Geで、Si2pはSi-O結合に対応する102.4eVにピークを示し(図1a)、これは理想的なSiO 2 の結合エネルギーよりも小さいです。 [24]。両方の亜酸化ケイ素(SiO x )PEALDプロセス中のGe表面での堆積とSi-O-Ge形成により、Si2pがより低いエネルギーにシフトする可能性があります。したがって、Ge上の厚いPEALD(〜7 nm)のSi2pスペクトルも実行されました。理想的なSiO 2 に対応する103.6eVにメインピークを示すことがわかります。 図1bに示すように、ボンディング。したがって、ここでPEALDによって堆積された酸化ケイ素は理想的なSiO 2 。ただし、強いSi-O-Siピークの他に、約102.4 eVに弱いピークがあります。これは、Ge表面のSi-O-Ge結合に対応しているはずです。したがって、最初のPEALD SiO 2 ではGe表面にSi-O-Geが形成されていると結論付けることができます。 成長。その場で4nm HfO 2 の後 図1aに示すように、堆積すると、Si 2pのピーク強度は明らかな化学シフト(102.3 eV)なしに減少します。さらに、Si 2 p N 2 で500°CのPDAを行った後も、ピークは明らかな化学シフト(102.2 eV)を示しません。 、HfO 2 の良好な熱安定性を示唆しています / SiO 2 HfO 2 中のインターフェース 堆積およびPDAプロセス。堆積したままのHfO 2 のHf4fスペクトル / SiO 2 ゲートスタック(図1c)、16.5および18.2eVのダブレットをHf4f 7/2 に割り当てることができます。 およびHf4f 5/2 HfO 2 のピーク スピン軌道相互作用エネルギーは1.7eVで、HfO 2 の文献値と一致しています。 [25]。 500°CPDA後、Hf 4fスペクトルは明らかな変化を示さず、0.1eVだけがより高いエネルギーにシフトします。これは、PDAプロセス中に形成された明らかなHfケイ酸塩がないことを意味します。図1dでは、堆積したままのサンプルのGe 3dスペクトルは、29.4および30.0 eVにダブレットピークを示しています。これは、スピン軌道相互作用エネルギーが0.6eV。 Ge基板の信号を除いて、Ge-O結合の32.7eVに大きなピークがあります。 Ge-Oピークは、Ge-O-SiとGeO 2 の形成に起因するはずです。 。 GeO 2 層は、PEALD SiO 2 の間に表面酸素プラズマ酸化によって形成されました。 堆積プロセス。したがって、ここで実際に製造された構造はHfO 2 です。 / Si-O-Ge / GeO 2 / Geスタック。さらに、Ge 3dスペクトルは、500°CのPDA処理後に明らかな変化を示さず、HfO 2 の熱安定性を示しています。 / Si-O-Ge / GeO 2 / GeスタックなしのGeO 2 劣化。北らによって報告されています。 GeO 2 のいくつかのキャッピングレイヤー GeO 2 を抑制できます SiやLa 2 などの分解 O 3 [19]。したがって、ここでPEALDによって誘発されたSi-O-Ge中間層は、GeO 2 も抑制することができます。 分解。上記のXPS分析に基づいて、Ge表面に極薄のSi-O-Ge中間層が形成されていると結論付けることができます。さらに、この中間層は、Hf-ケイ酸塩を形成することなく素晴らしい熱安定性を示し、GeO 2 を阻害することもできます。 劣化。

SiO 2 のXPSスペクトル / GeおよびHfO 2 / SiO 2 / Ge構造。 a SiO 2 のSi2pスペクトル 、堆積およびアニールされたままのHfO 2 / SiO 2 Geに。 b 厚いSiO 2 のSi2pスペクトル (7 nm)Geで。 c、d 堆積およびアニールされたHfO 2 のHf4fおよびGe3dスペクトル / SiO 2 / Ge構造

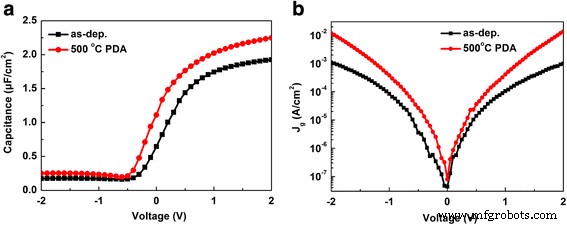

図2aは、HfO 2 の高周波(1 MHz)C-V曲線をプロットしたものです。 / SiO 2 PDAの前後のGeのゲートスタック。フラットバンド電圧( V fb )HfO 2 の値 / SiO 2 PDAの前後の/ Geは、それぞれ0.42Vと0.27Vです。計算された理想的な V fb 値は0.55Vです。わずかに負の V fb シフトは正の固定電荷を示します。これは、誘電体の酸素空孔によって引き起こされる可能性があります[26、27]。不活性雰囲気アニーリングプロセス中に、より多くの酸素空孔が誘発され、わずかに負の V が生じる可能性があります。 fb シフト。 GeO 2 は、多くの報告された文献で実証されています。 アニーリング中の劣化により、正の V が発生します fb シフト。 Ge-Oの脱着プロセスは、追加の負電荷を生成すると考えられています[28、29]。したがって、GeO 2 V からのGe-O-Si中間層により分解が抑制される fb シフト。蓄積容量は、元の1.92から2.25μF/ cm 2 に明らかに増加します。 PDA後。 MOSコンデンサの対応する容量等価厚(CET)値は、ε 0 を使用してC-V曲線の累積容量から計算できます。 ε r A / C acc [30]。したがって、1.10 nmの堆積したままのサンプルと比較して、PDA後に1.53nmの小さいCETが得られます。これは、PDAプロセスの後に、より高密度でより薄いhigh-k層を取得できるという事実に起因する可能性があります。図2bは、HfO 2 のリーク電流特性を示しています。 / SiO 2 PDAの前後のGeのフィルム。 V のバイアス電圧で fb + 1 V、リーク電流密度は2.1×10 -3 A / cm 2 および2.2×10 -4 A / cm 2 それぞれPDAの前後のサンプル。 PDA後のリーク電流密度の増加は、ゲート誘電体の厚さの減少にも起因する可能性があります。

HfO 2 の電気的特性 / SiO 2 500°CPDAの前後のGe基板上のゲートスタック。 a 高周波(1 M Hz)C-V曲線。 b J-V曲線

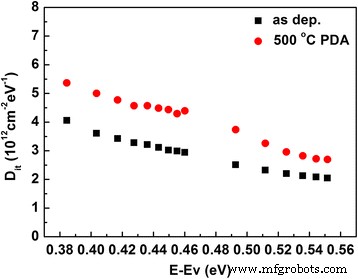

HfO 2 のインターフェース品質を調べるために / SiO 2 / Ge定量的に、界面状態密度( D それ )はコンダクタンス法[31]によって決定されました。図3は、 D の分布を示しています それ E c の下 Pt / HfO 2 の室温でコンダクタンス法によって抽出されたバンドギャップ内 / SiO 2 / Ge500°CPDAの前後。 D それ D から大まかに計算できます それ =2.5×( G p / w ) max / A q、ここで( G p / w ) max はコンダクタンス-電圧特性のピーク値、 f (= w /2π)は周波数、 A は電極面積、 q 電気素量です。したがって、 D それ Pt / HfO 2 の値 / SiO 2 PDAを使用しない場合と使用する場合の/ Ge構造は、4.05×10 12 と決定されます。 eV -1 cm -2 および5.37×10 12 eV -1 cm −2 E-E v で =0.38eV、それぞれ。下の D それ 2.03×10 12 の値 cm −2 eV -1 および2.67×10 12 cm −2 eV -1 PDAを使用しないサンプルと使用したサンプルでは、伝導帯の下部付近がそれぞれ観察されます。

D it の配布 E c の下 Pt / HfO 2 の室温でのバンドギャップ / SiO 2 / Ge500°CPDAの前後

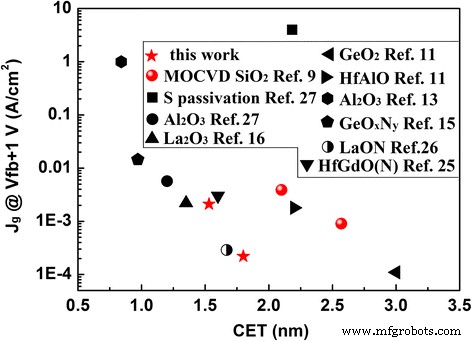

図4は、漏れ電流密度( J )を示しています。 g )-異なる界面制御層を備えたGeベースのMOSコンデンサのCET関係[32、33]。以前の研究[34]で報告された中間層のないS-不動態化Geと比較すると、HfO 2 / SiO 2 この作業の/ Geは、CETが小さく(1.53 vs 2.18 nm)、リーク電流密度(2.1×10 -3 )で大幅に改善された特性を示します。 vs 3.1 A / cm 2 )、および D それ (4.37×10 12 vs8.61×10 12 eV -1 cm −2 )。これは、その場でPEALDで形成されたSiO 2 Geの素晴らしいパッシベーションレイヤーです。さらに、exsituで形成されたSiO 2 と比較して MOCVDによる中間層[9]、その場でPEALDで形成されたSiO 2 を含むサンプル この作業の中間層は、CETが小さい(1.53 vs 1.75 nm)とリーク電流密度(2.1 vs 3.9 mA / cm 2 )の両方で優れた電気的性能を示しています )。これは、SiO 2 PEALDによって堆積されたものは、特に極薄の厚さの場合、MOCVDよりも均一です。

異なる界面制御層を備えたGeベースのMOSコンデンサのリーク電流密度(Jg)とCETの関係

HfO 2 でのバンドアラインメント / SiO 2 / Ge界面は、価電子帯オフセット∆E v を測定することによっても決定されました。 (VBO)XPSを使用します。 VBO値は、コアレベルと基板の価電子帯(VB)エッジの間のエネルギー差が、誘電体膜の堆積の有無にかかわらず一定のままであるという仮定に基づいて取得できます[35]。ここでは、ゲート誘電体スタックとGe基板間のVBOを決定するための基準としてGe基板を選択しました。図5aは、堆積およびアニールされたままのHfO 2 であるクリーンなGe基板のVBスペクトルを示しています。 / SiO 2 / Geスタックは、それぞれ線形外挿法によって決定されます。クリーンなGe基板のVBエッジは0.10eVであると判断されました。そして、堆積およびアニールされたままのHfO 2 のVBエッジ / SiO 2 サンプルは、それぞれ2.55eVと2.79eVであることがわかります。 HfO 2 のVBスペクトルに小さなテールがあることに気付くことができます。 / SiO 2 / Geスタック。これは、Ge基板信号に対応します[36]。この弱いテールのリーディングエッジは0.10eVと測定され、Ge基板のVBエッジと同じです。したがって、HfO 2 のインターフェースにあるVBO / SiO 2 PDAがある場合とない場合の/ Geは、それぞれ2.69および2.45eVと推定されます。伝導帯域オフセット∆ E c (CBO)は、HfO 2 のバンドギャップから基板のVBOとバンドギャップを差し引くことで得られます。 :

堆積およびアニールされたHfO 2 のバンドアラインメント / SiO 2 Geの映画。 a 堆積およびアニールされたままのHfO 2 のGe基板の価電子帯スペクトル / SiO 2 映画。 b 堆積およびアニールされたHfO 2 のバンドアラインメントの概略図 / SiO 2 Geの映画

ここで E g (HfO 2 )および E g (Ge)はHfO 2 のバンドギャップです それぞれ、Ge。 GeとHfO 2 のバンドギャップ それぞれ0.67と5.6eVです。したがって、HfO 2 のインターフェースでのCBO値 / SiO 2 PDAがある場合とない場合の/ Geは、それぞれ2.24eVと2.48eVと推定されます。 CBO値は、以前に報告された1.8〜2.6eVのデータと一致しています[37]。図5bは、堆積およびアニールされたHfO 2 の対応するバンドアラインメントを示しています。 / SiO 2 / Ge構造。明らかに、HfO 2 / SiO 2 Ge上のhigh-kゲート誘電体スタックは、リーク電流を抑制するために大きなバリア高さを持つ大きなVBOおよびCBO値を示します。

結論

要約すると、SiO 2 中間層がHfO 2 に導入されました insituPEALDによるn-Ge基板上のゲート誘電体。 HfO 2 の界面、電気的特性、およびバンド配列を調査しました。 / SiO 2 / GeMOS。 Ge-O-Si中間層とGeO 2 その場でのSiO 2 の間にGe表面に層が形成されます 沈着。このGe-O-Si中間層は、Hf-ケイ酸塩を形成することなく、PDA中に素晴らしい熱安定性を示します。さらに、Ge-O-Si中間層もGeO 2 を阻害する可能性があります アニーリングプロセス中の劣化。 HfO 2 / SiO 2 PDA後の/ Geサンプルは1.53nmのCET値を示し、リーク電流密度は2.1×10 -3 と低くなっています。 A / cm 2 V fb で + 1 V. HfO 2 でのVBO値 / SiO 2 PDAがある場合とない場合の/ Geは2.69および2.45eVであり、CBO値はそれぞれ2.24および2.48eVであると決定されます。 exsituで形成されたSiO 2 との比較 MOCVDによる中間層、その場でPEALDで形成されたSiO 2 のサンプル この作業の中間層は、SiO 2 であるという事実に起因して、改善された電気的性能を示しています。 PEALDによって堆積されたものはMOCVDよりも均一です。したがって、PEALDは、MOCVDよりもはるかに強力な超薄界面制御層堆積技術です。

ナノマテリアル

- マイクロLEDおよびVCSEL用の高度な原子層堆積技術

- 自己整流スイッチ特性を備えたTaO / HfOxおよびTaO / AlO xRRAMの保持モデル

- 原子層堆積によって製造されたPtおよびTiNコーティング基板上のHfO2 / TiO2 / HfO2三層構造RRAMデバイスのバイポーラ抵抗スイッチング特性

- 無電解エッチングで作製したシリコンナノワイヤの光学的および電気的特性

- 原子層堆積と水熱成長によって製造された抗菌性ポリアミド6-ZnO階層型ナノファイバー

- プラズマ化学原子層堆積によって調製されたCo3O4被覆TiO2粉末の光触媒特性

- ナノカーボンフィラーの電界支援配向による複合材料の電気的性質

- 界面層の設計によるZnO膜の表面形態と特性の調整

- 超循環原子層堆積によるZnO膜のフェルミ準位調整

- c面GaN上に堆積した原子層AlNの界面および電気的性質への厚さ依存性

- Ge / Siチャネル形成とデバイス性能に及ぼすエッチング変動の影響