Ge / Siチャネル形成とデバイス性能に及ぼすエッチング変動の影響

要約

シリコンオンインシュレータ(SOI)基板上にGeフィン構造を形成する際に、ドライエッチングプロセスを注意深く制御する必要があることがわかりました。そうしないと、Geのオーバーエッチングまたは望ましくないGeフィンプロファイルの形成につながる可能性があります。エッチングプロセスが適切に制御されていない場合、上部のGe / SOI構造がエッチングで除去され、Siフィン層のみが残ります。この場合、デバイスは異常な特性を示します。エッチングプロセスは、デバイスのスケーリングとパッケージングにおける重要なステップとして浮上しており、パッキング密度を高めてデバイスのパフォーマンスを向上させる試みに影響を与えます。したがって、使用するプロセスパラメータを調整するだけでなく、使用するハードウェアを変更するために、シミュレーションを通じてプラズマ反応器の動作の最適化を実行することをお勧めします。更新された製造パラメータを使用して、Geジャンクションレスデバイスを開発します。さらに、高品質のエピタキシャルGe層の懸垂構造を得るという目標を達成するために、周期的熱アニーリングプロセスを適用することにより、界面でのミスフィット転位を排除するか、貫通転位を減らしたいと考えています。

背景

半導体デバイスの応答速度を上げ、消費電力を削減する1つの方法は、キャリア移動度の高い半導体を使用することです。このような材料の例には、Geとその合金および化合物が含まれます。しかし、別の半導体の基板の上に半導体材料の層を積み重ねて構造を形成すると、問題が発生する可能性があります。例えば、半導体基板と異なる半導体材料の上層の格子サイズの違いは転位を引き起こす可能性があり、それはデバイスの性能に悪影響を与える可能性があります。従来、Si基板を含むGeベースの半導体デバイスを製造するために、より厚いバッファ層または犠牲層(例えば、Si / Geバッファ層)がシリコン基板上に形成される。続いて、Geエピタキシャル層がSi / Geバッファ層上に成長します。次に、異方性エッチングプロセスと等方性エッチングプロセスを順次実行して、バッファ層の一部を除去し、Geエピタキシャル層を保持します。 VLSIデバイスは、待機電力消費量の削減や動的消費電力の削減などの高性能を確保するために、高い駆動電流、低いオフ状態リーク電流、および低い電源電圧を示す必要があります。現在、ひずみが強化された移動度、high-k /金属ゲート、および22 nmノードでの3次元(3D)デバイスアーキテクチャ[1]は、相補型金属酸化膜半導体の連続スケーリングに使用されている技術の一部です( CMOS)Siチャネルを備えたデバイス。高移動度などの特性に加えて、サブの静電制御を改善するには、ゲートオールアラウンド(GAA)[2]や超薄型電界効果トランジスタ(FET)[3]などの新しいデバイスアーキテクチャが必要です。 -10nmノード。反転モード(INV)動作を備えたGeベースのGAA pFET [4]およびnFET [5]が実証されています。ただし、Ge INVデバイスでの接合形成は、ドーパントの溶解度が低く、ドーパントの拡散が速く、熱収支が低いため、重要な問題です。これらの問題を解決するために、ソース/ドレイン(S / D)領域と同じキャリアタイプの高濃度ドープチャネルを使用するジャンクションレス(JL)デバイス[6]が代替案として提案されています。ただし、トランジスタの急速なスケーリングには、最新のトランジスタに追いつくことができる、新しくより効果的なデバイスの開発が必要です。近年、JL-FETは次世代トランジスタとして有望であることがわかっています。 JL-FETは基本的に、モバイルキャリア密度をゲートで制御できる抵抗器です。オン状態では、チャネル領域のドーピング濃度が比較的高いため、大きなボディ電流が存在します。表面蓄積電流がこの電流に追加されます。適切な電流駆動を実現するには、JL-FETのドーピングレベルを高くする必要がありますが、デバイスの断面積は、デバイスの電源をオフにできるように十分に小さくする必要があります。 。ただし、高濃度にドープされたJL-FETの場合、キャリアはかなりの不純物散乱を受け、そのために駆動電流が大幅に低下します[7]。さらに、JL-FETには、INVデバイスとは対照的に、製造が簡単で、電荷移動度が高く、ゲート容量が小さいという利点があります[8、9、10、11、12]。最近、ダブルゲート[13]とボディタイドトライゲート[14] Ge JL-FET pMOSFETが、それぞれゲルマニウムオン絶縁体基板とバルクSiで実証されました。

マイクロエレクトロニクスデバイスが縮小し続け、プロセス要件がますます厳しくなるにつれて、プラズマモデリングとシミュレーションは、プラズマリアクターの設計、制御、および最適化のためのツールとしてますます魅力的になっています[15]。長さと時間スケールの不一致に基づいてプラズマプロセスの動作をシミュレートするために、いくつかの手法が使用されます。シミュレーション手法の1つである数値流体力学(CFD)は、エンジニアリング設計機能の流れ場を予測し、実験の限界を推定するために広く使用されています。そのモデリングは、流動混合現象を調査するために適用されています[16]が、エッチングプロセスにおけるまれな研究です。したがって、この研究では、エッチングプロセス用のプラズマ反応器の熱流場を詳細に特徴付け、次に実験に有益な数値パラメータを推定することを提案しました。

この作業では、エッチングを実行して、デバイス統合用の他の合金半導体と同様に、Si上に浮遊エピタキシャルGe層を形成しました。シミュレーション結果は実験によって検証されます。したがって、初期条件と境界条件、および数値モデルのパラメーターは、データの信頼性を高めるために変更されます。実験とシミュレーションによって最適なパラメータが得られ、エッチング技術が向上し、より高い製造プロセス品質とより低い製造コストを実行することで、このトランジスタ開発を実現できると期待しています。

メソッド/実験

出発基板は、トップ70 nmのシリコン層(p型、9〜18Ωcm)を備えたSOIウェーハでした。ウェーハは、存在する有機物、不要な金属、および粒子を除去するために、RCA標準クリーン1(SC-1)およびRCA標準クリーン2(SC-2)プロセスを使用して洗浄されました。その後、脱イオン水ですすぎ、N 2 で乾燥させました。 。 Ge膜は、10%GeH 4 を使用して、低圧化学蒸着エピタキシャル反応器(Epsilon 2000、ASM)で蒸着されました。 前駆体として。キャリアガスとして水素を使用した。 Ge膜を堆積する前に、その場でHClベースの前処理を850°Cおよび10 Torrで実行して、ウェーハ表面を準備しました。次に、基板温度を400°Cに変更して、10%GeH 4 を使用してSOIウェーハ上にGe膜を成長させました。 。堆積したGe膜の厚さは、透過型電子顕微鏡(TEM、熱放射ショットキータイプ、0.5〜200 kV)を使用して決定しました。 Ge膜の結晶化度は、X線回折(XRD)分析(D8A、Bruker、CuKα放射線、λ=1.5408Å、20–70°)を使用して調べました。さらに、X’Pert MRD(PANalytical)システムを使用して、(004)回折ピークの周囲でΩ–2θスキャンを実行しました。 2つ折りのGe {400}チャネルカットクリスタルコリメータを使用して、CuKα1放射線を選択しました。標準のXRD測定中、サンプルは水平位置に固定され、回折計の光源と検出器のアームはθ–θモードで移動しました。逆格子空間マッピングは、上記の結晶コリメータを使用して中解像度モードで実行されました。シンチレーションカウンターの前の検出器アームには、幅0.4mmのスリットがありました。 Ge層の厚さは、エリプソメトリー測定(M2000、J。A。Woollam Co.、λ=193–1690 nm)によって決定されました。フィンは、Cl 2 を使用した異方性プラズマエッチングによって形成されました。 / HBrガス。 ZrO 2 の形成後 / TiNゲート、S / DにはBが埋め込まれています(1×10 15 cm −2 、15 keV)、550°Cで30秒間の急速熱アニーリングによって活性化されます。

ゲルマニウムメカニズムの高度に選択的なドライエッチング

電子反応と中性反応は等方性ですが、イオン反応は指向性が高く、加えられたバイアスによって変化します。バイアスパワーを調整することにより、イオンを所望の方向に沿って加速し、エッチング反応を助けることができる。 BrはSiと自発的に反応せず、反応が起こるには高エネルギーのイオンが必要であると一般に認められています。イオン支援のBrおよびCl原子は、活性化下でGeまたはSi原子と自発的に反応して、揮発性生成物GeBr 4 を形成します。 、GeCl 4 、SiBr 4 、およびSiCl 4 、基板表面から脱着され、ポンプで排出することができます。 SiとBrのこのイオン支援化学反応は、非常に異方性であることが示されています。バイアスパワーの変動にHBrを使用すると、より高い垂直エッチング速度が得られました。これにより、Cl 2 にHBrを添加したことが確認されます。 エッチング速度を高めることができます[17]。 ClベースおよびBrベースのプラズマはイオン支援メカニズムによってGeおよびSiをエッチングするため、Br + などのイオンのエネルギー 、Br 2+ 、HBr + 、Cl + 、およびCl2 + 基板ホルダーにバイアスをかけることで制御できます。上面とネッキング領域の両方のエッチングのバイアスパワーを変化させても、横方向のエッチング速度に顕著な変化はありません。 Ge / Si界面に沿った欠陥によって横方向のエッチングが強化されたため、ネッキング領域でHBr混合物を使用してエッチングされたフィン構造にアンダーカットが見つかりました。また、マスクは、イオンフラックスからの側壁の衝突により、形状の変化に影響を与える可能性があります。この現象は、プロファイルが深くなり、横方向のイオン速度成分が増加するにつれて増幅されます。 HBr-プラズマエッチングプロセスの角度依存性が高いため[18]、したがって、不適合転位からの部分的に結合した原子と比較的弱いため、結晶構造はGe / Si界面で比較的弱いと結論付けることができます。 Ge-GeおよびGe-Si結合。 HBr / Cl 2 の比率を調整する バイアスパワーにより、Geデバイスの製造中にさまざまなタイプのフィンのような構造を得ることができます。 GeとSiのエッチング特性は非常に似ています。 Siをエッチングするガスは通常、Geをより速い速度でエッチングします。 GeおよびSi結合の強度は、Ge-Ge =263.6±7.1kJ mol -1 であることが示されています。 およびSi-Si =325±7kJ mol -1 [2]。イオンの方向性加速によって垂直エッチング速度を調整するために、異なるバイアスパワーが適用されました。画像は、ゲートスタックプロセスの後に記録されました。垂直エッチング速度は、酸化物基板に対するフィルムの高さから計算された。横方向のエッチング速度は、フィンの2つの部分から決定されました。フィンの上面での横方向のエッチングと、Ge / Si界面に近いネッキング領域でのエッチングです。要約すると、バイアスパワーは、エッチングプロセスにおいて最も重要なパラメータであり、したがって、それに応じてデバイスの特性に影響を与えることが実験的にわかっています。

この研究では、すべてのエッチングプロセスはLamResearchのTCP9600リアクトルで実行されました。これは、コイル(上部電極)の電力と基板(下部電極)のバイアスを別々に制御できるトランス結合プラズマリアクターです。基板の温度をより効果的に制御できるように、ヘリウム裏面冷却が組み込まれました。サンプルは6インチにマウントされました。エッチングチャンバーに導入される前の真空グリースを含むSiキャリアウェーハ。 HBr / Cl 2 化学は異方性エッチングプロセスに利用されました。プロセス圧力は10mTorrに制御されました。詳細な実験のセットアップと条件は、Hsuらの研究に示されています。 [4]。

物理モデル

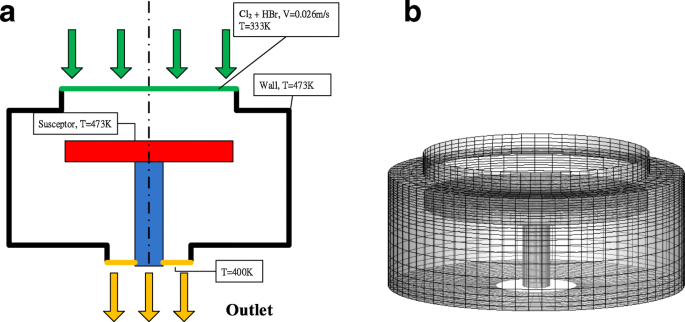

CFDは、反応器内の内部情報にアクセスするために使用され、チャンバー内のクヌーセン数が高いため、流れはすべり境界条件で層流であると見なされます(図1)。現在のシミュレーションでは、プラズマの熱流は運動量方程式の混合物と見なされます。粒子輸送は種支配方程式で考慮され、化学反応はサセプタ壁に関与します。シミュレーションのモデルケースの1つを図3に示します。入口ガスは塩素の混合物です(Cl 2 )および臭化水素(HBR)。入口での混合速度は0.026m / sで、温度は333Kに保たれています。サセプタとチャンバー壁は動作温度473Kに加熱されます。これらのプラズマ流は電位バイアスによって駆動され、サセプタ表面で化学反応を起こします。均一で再現性のある方法で、最終的に反応器から排出されます。 CADソフトウェアでソリッドモデリングを構築した後、メッシュシステムは、図3に示すように、50、000ノードの構造化グリッドで構築されました。スカラー量ϕの輸送の過渡保存方程式は、積分で記述された次の方程式によって示されます。次のように任意の制御ボリュームVの形式[19]:

プラズマ反応器の数値シミュレーションのための物理モデル。 a 所定の境界条件を持つ原子炉チャンバーのスケッチ。 b 数値シミュレーション用メッシュシステム

ここで、ρは密度を示します。 \(\ overset {\ rightharpoonup} {v} \)は速度ベクトルです。 \(\ overset {\ rightharpoonup} {A} \)は表面積ベクトルです。 Vはボリュームです。 Γは、ϕとS ϕ の拡散係数です。 は、単位体積あたりのϕのソース項です。連続の方程式 u の場合、記号ϕは1に置き換えることができます。 、 v 、および w はX、Y、Z方向の運動量方程式であり、Ciはそれぞれ原子炉チャンバー内の種輸送方程式です。式(1 *)は、シミュレーション用の有限体積法アプローチを使用して、一般化座標で表すことができます。境界条件を組み合わせた後、式。 (1 *)は線形化され、代数方程式のセットとして計算領域で表現されます。これは、CFD手法を使用したSIMPLEアルゴリズムによって解くことができます[19]。ほとんどの半導体製造装置は大気圧よりはるかに低い圧力で動作することに注意してください。このような低圧では、流体の流れはすべり領域にあり、速度と温度に通常使用されるすべりのない境界条件は無効になります。非常に低い圧力での現在のプラズマ流は、自由分子流と連続体レジームの間にあるスリップレジームにあります[20]。したがって、流体の流れをモデル化するための速度と温度のすべり境界条件が、数値シミュレーションに課せられます。

半導体材料のSi(s)とGe(s)は、次の表面反応によって支配される加熱されたサセプタ表面にエッチングで除去されます。

$$ {\ mathrm {Cl}} _ 2 + \ mathrm {Si} ={\ mathrm {SiCl}} _ 4 $$(2 * .1)$$ 4 \ mathrm {HBr} + \ mathrm {Si} ={\ mathrm {SiBr}} _ 4 + 2 {\ mathrm {H}} _ 2 $$(2 * .2)$$ 2 {\ mathrm {Cl}} _ 2 + \ mathrm {Ge} ={\ mathrm {GeCl}} _ 4 $$ (2 * .3)$$ 4 \ mathrm {HBr} + \ mathrm {Ge} ={\ mathrm {GeBr}} _ 4 + 2 {\ mathrm {H}} _ 2 $$(2 * .4)化学反応は、式(1)のSiエッチングでも同様です。 (2 * .1)および式。 (2 * .2)、または式のGeエッチング。 (2 * .3)および式。 (2 * .4)。したがって、塩素と臭化水素の混合によるSiエッチングプロセスは、次のシミュレーションで示されます。

結果と考察

材料の特性評価

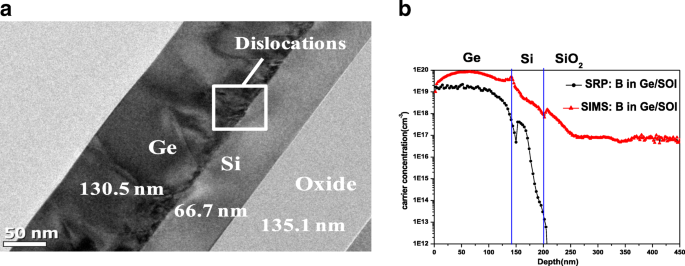

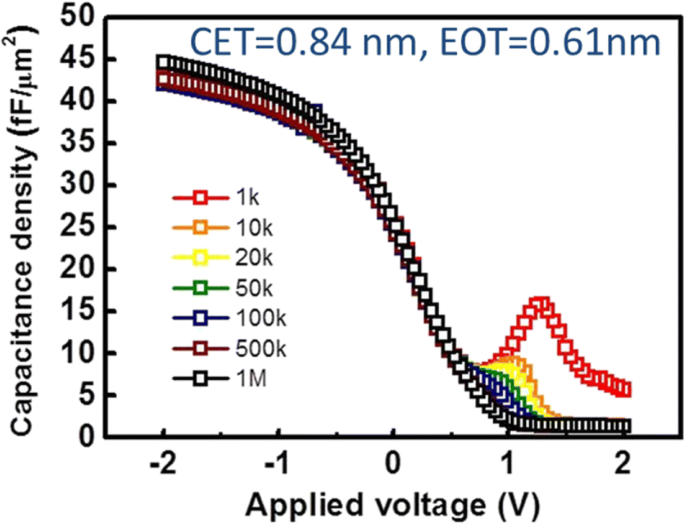

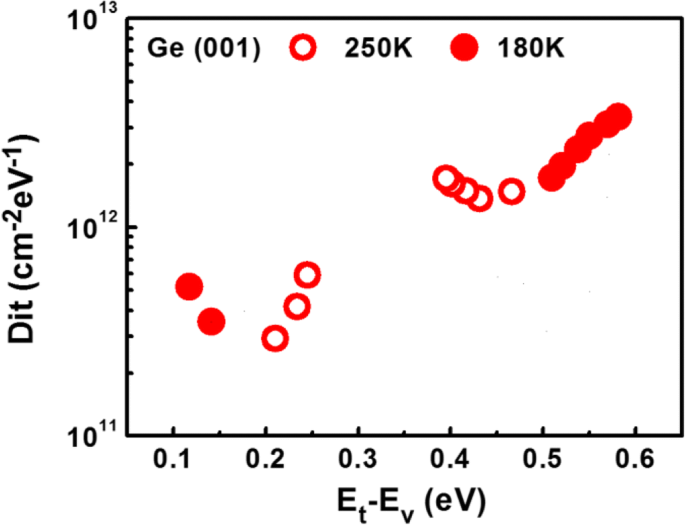

SOI基板上に形成されたGe層の断面TEM画像を図2aに示します。見てわかるように、不適合転位はGe / Si界面に存在します。これらは、次に、エピタキシャルGe膜を横切る貫通転位をもたらす。これらの貫通転位は、GeとSiの間の熱的ミスマッチに対応すると考えられています。ほとんどの貫通転位は、界面から80nm以内で終了しました。しかし、多くはフィルム表面にも伝播しました。ドーパント分布と活性化レベルを調べるために、SOI基板上のエピタキシャルGe膜にホウ素を注入し、続いて活性化しました。 PCOR-SIMSおよび拡散抵抗プロファイリング(SRP)プロファイルに示されているように、Ge層の上部130 nm部分では、ホウ素の活性化率は約85%でした。 (図2bを参照)。 Ge / Si界面近くのGe層の底部では、欠陥の存在とSRPの測定限界のために、正孔濃度が大幅に低下しました。製造されたデバイスの場合、Ge / Si界面付近の欠陥のあるGeは選択的エッチングによって除去されました。したがって、チャネルで実行されるPCOR-SIMSおよびSRP測定は正確である必要があります。 〜の最大アクティベーションレベル 3×10 19 cm -3 従来のアクティベーション制限と完全に一致しています。ホウ素注入中に実行される低温活性化(550°C)のために、寄生Siチャネル付近のS / Dは非常に抵抗性であることに注意してください(図2)。これにより、寄生Si伝導が防止されました。図3に、TiN / ZrO 2 の静電容量-電圧(CV)特性を示します。 / Ge金属-絶縁体-半導体コンデンサ(MISCAP)。不安定なGeO x の形成を防ぐため High-k誘電体堆積および堆積後アニーリングプロセス中の層、窒化物ベースの材料Ge 3 N 4 GeO 2 ではありません NH 3 を介してGe(001)表面に界面層として挿入された / H 2 リモートプラズマ処理。 ZrO 2 層は、原子層堆積によって250°Cで20サイクル堆積されました。測定されたCV曲線は、1KHzから1MHzまでの周波数分散またはストレッチアウトを示しておらず、一貫しています。 ZrO 2 の近くにトラップレベルを作成する損失 / Geインターフェースは、少数キャリア生成の熱活性化エネルギーを、p-Geバンドギャップエネルギーに対応するエネルギーからミッドギャップエネルギーにシフトします。等価酸化物の厚さ(EOT)は0.6 nmで、 D それ (インターフェーストラップ密度)値は〜3×10 12 cm 2 eV -1 低温コンダクタンス法で測定したミッドギャップ付近(図4の挿入図を参照)。

a SOI基板上のp型GeのTEM画像。 b SOI上のその場でのホウ素ドープepi-Ge層のSIMSおよびSRPプロファイル。 Ge / Si界面近くの底部欠陥Geの正孔濃度は低い

TiN / ZrO 2 のC-V特性 / Ge MISCAPs with EOT〜0.6 nm

低温コンダクタンス法で測定したDit

原子炉の運転パラメータのシミュレーション

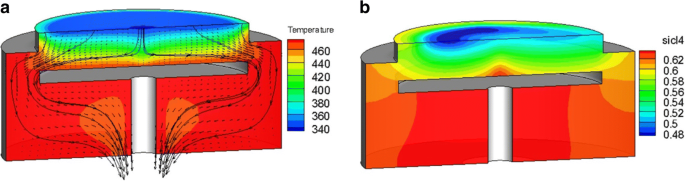

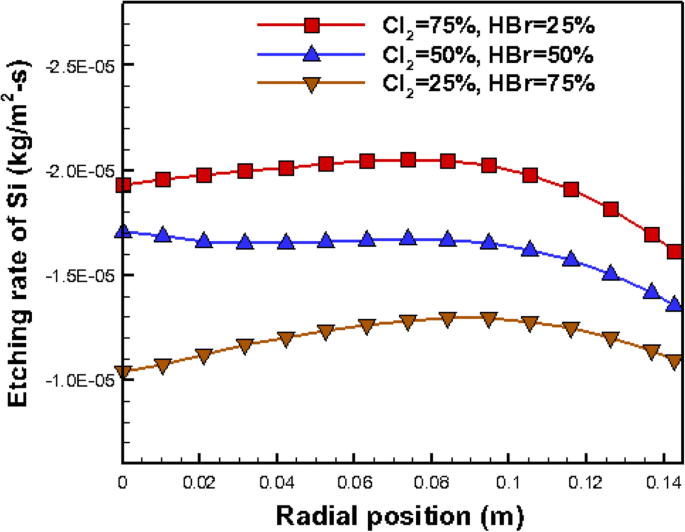

定常層流プラズマ流の典型的なモデルは、高速パーソナルコンピュータでシミュレートされました。入口ガスはCl 2 の混合物です 、質量分率が0.75のHBr、および質量分率が0.25のHBrです。図5aは、低温流入の等高線を示しており、内部の高温で動作し、反応器チャンバー内の粒子経路ラインを示しています。図5bは、生成物SiCl4の質量分率の等高線を示しています。これは、サセプタより上では濃度が低く、サセプタより下では出口までの濃度が高くなっています。その上、Cl 2 のより高い質量分率 エッチングで良好な性能が得られ、このノウハウは図6に示すように現在のシミュレーションによって検証されています。横軸はサセプタの1つの半径方向位置に沿っており、縦軸はエッチング速度(kg / m 2)を示します。 s)のSi。図6は、75%Cl 2 の入口混合物によって、より優れたエッチングプロセスがアーカイブされることを示しています。 と25%HBrであり、この混合物はこの研究の実験を行うために採用されました。

反応器内のプラズマパラメータの等高線。 a 温度分布と粒子経路線r。 b 製品SiCl 4 の質量分率コンター

入口ガスとさまざまなフラクションの混合物からのサセプタ上のSiのエッチング速度

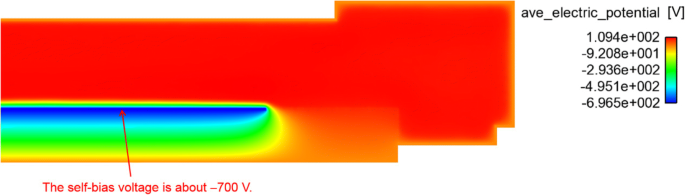

コンピュータ支援実験の実現可能性を示す別の事例は、プラズマエッチング用のチャンバー内の電位分布です。このエッチングプロセスの根底にあるメカニズムに基づいて、図7に示すように、プラズマ出力密度の分布について2Dシミュレーションモデルを開発し、モデルの精度を確認して支援するために、測定データを適合させるために使用しました。実験。

チャンバー内のプラズマエッチングの電位分布のシミュレーション

菅井が提案したように[21]、自己バイアス電圧はRF電極上のシースの静電容量に関連している可能性があります(C K )およびアース電極(C A )、次のように表現されます:

$$ {V} _ {\ mathrm {DC}} =\ frac {C _ {\ mathrm {K}}-{C} _ {\ mathrm {A}}} {C _ {\ mathrm {K}} + {C } _ {\ mathrm {A}}} \ {V} _ {\ mathrm {RF}} $$(3 *)図7に示す現在のシミュレーションによると、自己バイアス電圧は約-700 Vであり、式(1)から計算される理論値-650Vに近い値です。 (3 *)。したがって、使用するプロセスパラメータを調整するだけでなく、使用するハードウェアを変更するために、シミュレーションを使用して最適化を実行することをお勧めします。これにより、実行全体の均一性が確保され、最適化された高品質で低コストのプロセスが実現します。

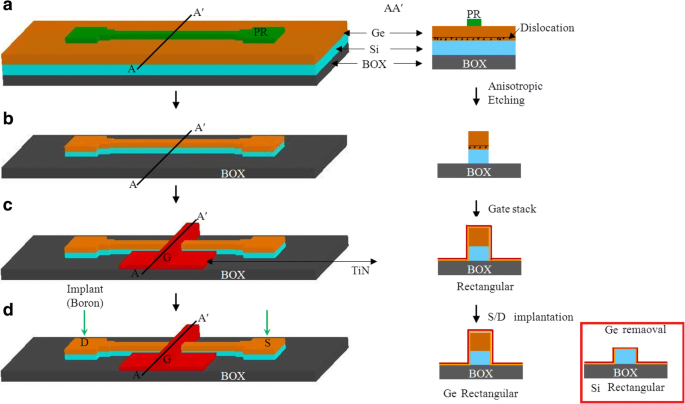

デバイスの製造と特性評価

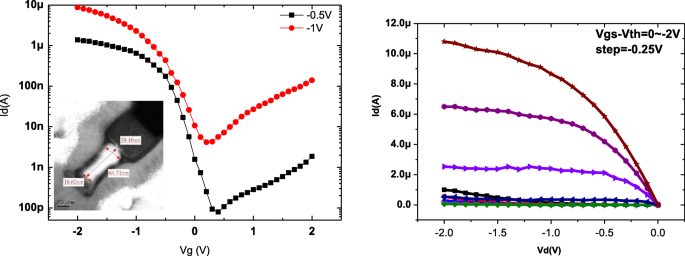

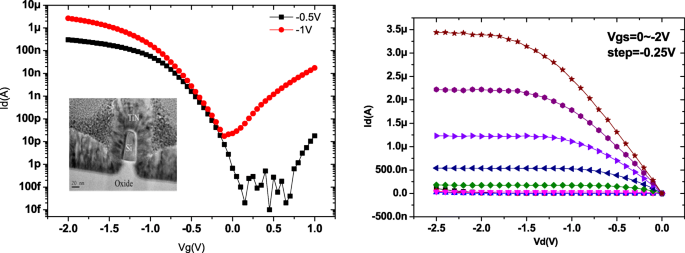

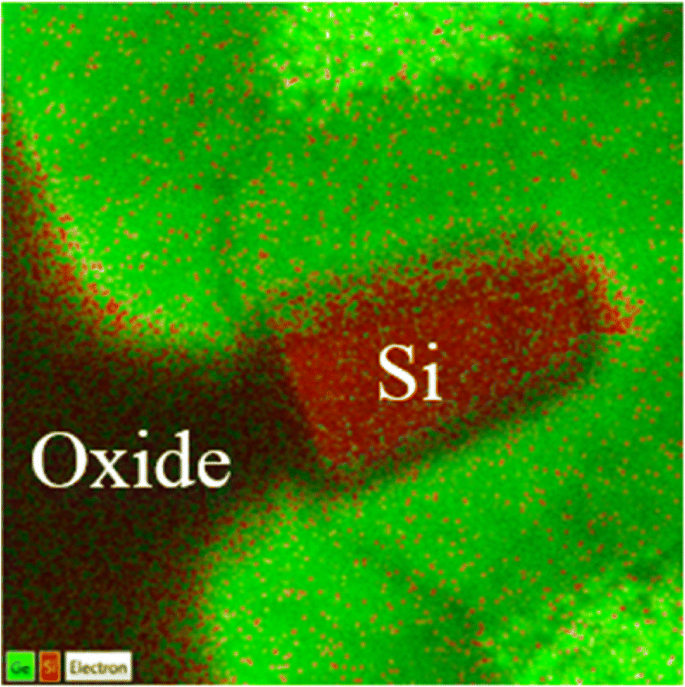

エピタキシャルGe層は、電子ビームリソグラフィーを使用して、目的のフィーチャサイズのフィンにパターン化されました。フィンは、Cl 2 を使用した異方性エッチングによって形成されました。 / HBrベースのプラズマは、Ge / Si界面近くの高欠陥Geをエッチング除去します。 SOI上のフローティングGeフィンは、SiよりもGeのエッチング選択性が高く、欠陥領域のエッチング速度が向上した状態で形成されました[4]。 SiO 2 次に、キャッピング層が堆積され、ゲートパターニング後にスペーサーになりました。アクティブ領域を定義した後、ZrO 2 のゲートスタック 層はそれぞれALDによって形成されました。作製したデバイスのチャネル断面を図8に示します。フィン幅( W fin )は、8×10 19 のチャネル濃度に使用されます。 cm − 3 これは、SOIのブランケットGeエピ層でファンデルパウ法を使用して抽出されます。チャネル濃度の増加と W の増加に伴い、チャネルの可制御性が低下することに注意してください。 fin [12、13]。チャネル濃度が大きい場合は、 W を小さくする必要があります。 fin 低SSを維持します。最後に、ゲート電極が定義され、堆積されました。図9は、フィン幅( W )の三角形GeFinFETの出力および伝達特性を示しています。 fin )18 nm、ゲート長( L g )90nmの。 私 on / 私 オフ GeJL-FETの比率は10 5 と高い サブスレッショルドスイング(SS)は〜100 mVdec − 1 。 SiJL-FETの伝達特性を図10に示します。 I on / 私 オフ Si JL-FETの比率は〜10 8 と高い 、そのSSは90 mV dec − 1 、その L g は80nmで、その W fin 20nmです。図8は、ゲート電圧のスパンΔ V も示しています。 g 、は約0.5 Vで、Geのバンドギャップに近い( E g / q =0.66V)。これにより、 I d – V g 図8に示す曲線は、GeFinFETの場合です。ただし、ゲート電圧のスパン、Δ V g 、図6に示すように、約1.8 Vであり、Siのバンドギャップに近い( E g / q =1.1V)がGeのそれではない( E g / q =0.66V)。したがって、 I d – V g 図9に示す曲線は、GeJL-FETではなくSiJL-FETの曲線です。この観察は、半導体デバイスの物理学に基づいており、実験的に決定された I によってサポートされています。 d – V g GeおよびSiFinFETの曲線、および断面TEM / EDSSiマップ。図11の挿入図から、2つのことが明らかです。挿入図は、Geオーバーエッチング後の予期しないSiJL-FETの出力および伝達特性を示しています。 私 on / 私 オフ このデバイスの比率は10 8 と高いです 。ただし、そのオン電流はわずか17μAμm − 1 − 1Vで。高い I on / 私 オフ 比率は、Ge層ではなく、Si層に起因します。 Si層だけが残っている場合、デバイスは実際にはGeJL-FETではなくSiJL-FETです。

デバイス製造の概略図。 a フィンのパターン化。出発材料はBOX上のGe(130 nm)です。 b 異方性エッチングとフォトレジストストライピング。 c ZrO 2 の原子層堆積によるゲート形成 およびTiNの堆積。 d 良好な接触のためのS / Dへの自己整合ホウ素注入。注:左側は3D回路図であり、右側は対応する断面図です

私 d – V gと I d – V d GeFinFETの曲線

私 d – V gと I d – V d 上部のGeが不注意にエッチングされた後のSiFinFETの場合。 私 on / 私 オフ 10 8 に達することができます 、現在の値は非常に低い

オーバーエッチングプロセスを受けるチャネル構造のTEMマッピング

結論

シミュレーションモデルと測定データの関係を確認します。したがって、使用するプロセスパラメータを調整するだけでなく、使用するハードウェアを変更するために、シミュレーションを使用して最適化を実行することをお勧めします。数値シミュレーションの助けを借りて、レクターの動作パラメーターを決定することにより、エッチングプロセスを改善し、トランジスタの開発を支援するために、Ge / Siチャネルを形成するためのエッチングプロセスのパラメーターを実験を通じて最適化できることを示しました。製造品質の向上と製造コストの削減。実験結果は、Ge FinFET用に開発されたドライエッチング技術が、トールフィンCMOSデバイスの製造にも非常に有用であることを示しています。

ナノマテリアル

- マイクロLEDおよびVCSEL用の高度な原子層堆積技術

- スリーステートエレクトロクロミックデバイスのディップコーティングプロセスエンジニアリングと性能最適化

- プラズマ化学原子層堆積によるその場で形成されたSiO2中間層を有するHfO2 / Geスタックの界面、電気、およびバンド整列特性

- アルミノシリケートミネラルおよび優れた水分解性能のための代替ドーピング

- 無電解エッチングで作製したシリコンナノワイヤの光学的および電気的特性

- Li-Nb-O化合物の調製と光触媒性能に及ぼすLi / Nb比の影響

- 界面層の設計によるZnO膜の表面形態と特性の調整

- 中空構造LiNb3O8光触媒の調製と光触媒性能

- メタマテリアルにおける表面プラズモンポラリトンと磁気双極子共鳴の結合効果

- SiナノワイヤFETセンサーの光伝導率、pH感度、ノイズ、およびチャネル長の影響

- レーザーエッチングとレーザー彫刻