異なるMOS容量の負の容量電界効果トランジスタの比較研究

要約

HfZrO x の負の静電容量(NC)効果を示します 実験におけるベースの電界効果トランジスタ(FET)。改善された I DS 、SS、および G m 制御金属酸化膜半導体(MOS)FETと比較してNCFETの性能が向上しています。この実験では、パッシベーション時間が異なる下部のMISトランジスタは、MOS容量が異なるNCデバイスと同等です。一方、40分のパッシベーションを備えたNCFETの電気的特性は、 C 間の良好なマッチングにより、60分のパッシベーションを備えたNCFETの電気的特性よりも優れています。 FE および C MOS 。 60 mV / decade未満のSSは達成されませんが、ロジックアプリケーションに有益な非ヒステリシス伝達特性が得られます。

はじめに

トランジスタのスケールダウンに伴い、集積回路(IC)の集積度は継続的に向上しています。付随する電力損失の問題は、解決することが急務です。この問題を回避するには、トランジスタの動作電圧を下げる必要があります[1]。 MOSFETのサブスレッショルドスイング(SS)は、室温で60 mV / decadeを下回ることはできません。これにより、しきい値電圧 V の低下が制限されます。 TH および供給電圧 V DD [2]。負の静電容量電界効果トランジスタ(NCEFT)[3、4]、抵抗ゲートFET [5]、ナノ-電気機械型FET(NEMFET)[6、7]、衝突電離金属酸化物半導体(I-MOS)[8、9]、およびトンネルFET [10、11]。その中でも、NCFETは駆動電流を失うことなく急峻なSSを実現できるため注目を集めています[12、13、14、15]。ドープされたHfO 2 (例:HfZrO x (HZO)およびHfSiO x )NCFETで広く使用されています[4、16、17]。 CMOSプロセスと互換性があります[18]。理論的研究によると、強誘電体コンデンサ C が一致しないために、望ましくないヒステリシスが発生することが示されています。 FE 基礎となるMOS容量 C MOS NCFET [19]で。ただし、 C 間のマッチングの効果 FE および C MOS NCFETの電気的特性に関する研究は、実験において依然として懸念事項です。

この作業では、 C 間の異なるマッチングに基づいて、MOS容量が異なるNC GeFETの電気的特性を調べます。 FE および C MOS 。 60 mV / decade未満のSSは現れませんが、ヒステリシスのない伝達特性とより優れた電気的特性が得られます。 C の見かけのピーク FE 対 V FE 曲線は、HZOベースのNCFETのNC効果を示しています。 C のより良いマッチング FE および C MOS SSの急峻化と電流の増加に貢献し、ロジックアプリケーションに有益です。

メソッド

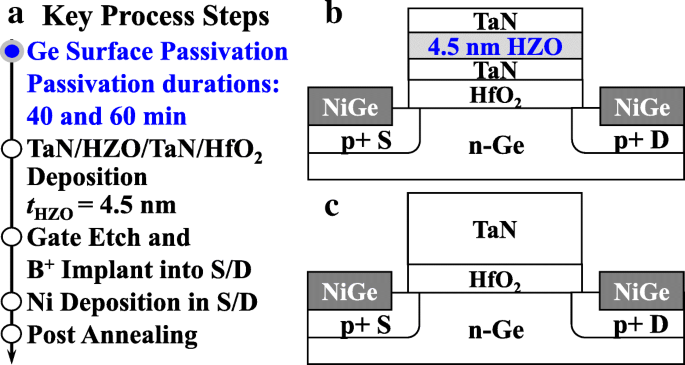

GeNCFETの主要な製造プロセスを図1aに示します。抵抗率が0.088–0.14Ω・cmの4インチn-Ge(001)ウェーハを出発基板として使用しました。ゲート前の洗浄後、Geウェーハを超高真空チャンバーにロードし、Si 2 を使用して表面パッシベーションを行いました。 H 6 。 40分と60分の2つの不動態化期間が使用されました。次に、TaN / HZO / TaN / HfO 2 スタックが堆積されました。 HfO 2 の厚さ 誘電体層とHZOFE層はそれぞれ4.35nmと4.5nmです。ゲートのパターニングとエッチングの後、ホウ素イオン(B + )を使用してソース/ドレイン(S / D)領域を注入しました。 )30keVのエネルギーと1×10 15 の線量で cm −2 。 S / D金属ニッケルは、リフトオフプロセスを使用して形成されました。最後に、450°Cで30秒間の急速熱アニーリングを実行しました。 TaN / HfO 2 でMOSFETを制御する スタックも製造されました。図1bとcは、それぞれ製造されたNCFETと制御MOSFETの回路図を示しています。製造されたNCFETの内部金属ゲートは、MFMIS構造と呼ばれるチャネル表面の電位を相殺します。

a 製造されたNCデバイスの主要なプロセスステップ。製造された b の概略図 NCFETおよび c 制御MOSFET

結果と考察

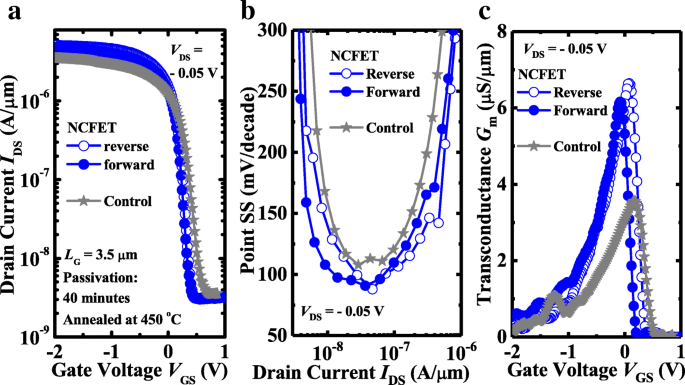

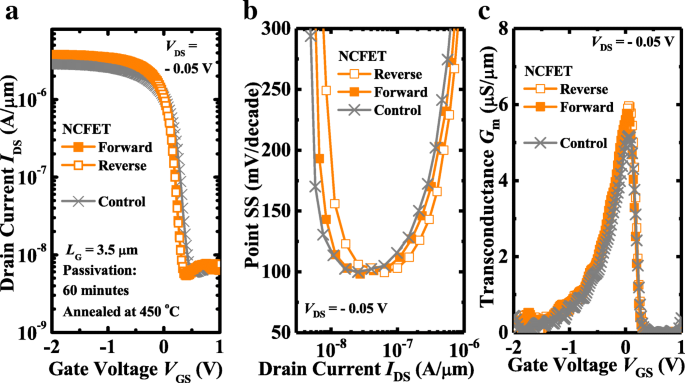

図2aは、測定された I をプロットしたものです。 DS - V GS 表面パッシベーションが40分のNCFETと制御MOSFETのペアの曲線。両方のデバイスのゲート長は L G 3.5μmの。 40分のパッシベーションを備えたNCデバイスでは、 I が大幅に改善されています。 DS 制御MOSFETより。 NCFETの伝達曲線は、非ヒステリシスの特徴を示します。ポイントSSと I DS 図2bの曲線は、NCトランジスタが制御デバイスよりもSSを改善していることを示していますが、サブ60 mV / decadeのSSは表示されていません。図2cは、NCトランジスタが大幅にブーストされた線形相互コンダクタンス G を取得することを示しています。 m V で制御装置を介して DS 図3は、NCFETと制御MOSFETの電気的性能を60分間の表面パッシベーションと比較しています。同様に、 I DS 、ポイントSSと G m NCFETの方が制御MOSFETよりも優れています。

a 測定された I DS - V GS 40分のパッシベーションを使用したNCFETと制御MOSFETの曲線。 b の比較 ポイントSS対 I DS および c G m NCFETと制御MOSFET間の特性

a 測定された I DS - V GS 60分のパッシベーションを使用したNCFETと制御MOSFETの曲線。 b の比較 ポイントSS対 I DS および c G m NCFETと制御MOSFET間の特性

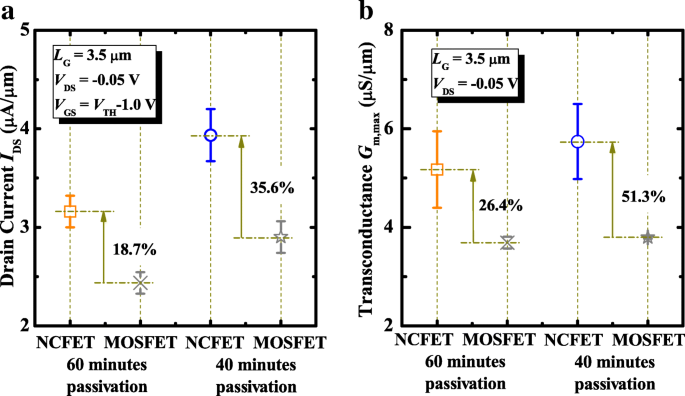

図4aは、 V でのNCFETと制御MOSFETの駆動電流の統計結果を示しています。 DS − 0.05Vおよび V GS - V TH =− 1.0 V.NCFETは、 I で18.7%と35.6%の改善を示しています DS 制御装置と比較して、それぞれ60分および40分の表面不動態化。 40分間不動態化されたNCFETは、 C 間のマッチングが優れていると推測されます。 MOS および C FE 60分でNCデバイスを介して。図4bは、NCFETが最大相互コンダクタンス G で26.4%と51.3%の改善を達成していることを示しています。 m、max 制御装置と比較して、それぞれ60分および40分の表面不動態化。表面パッシベーションが40分間の制御MOSFETの I が高いことがわかります。 DS および G m、max C が大きいため、60分間パッシベーションされたデバイスよりも MOS 等価酸化物の厚さが小さいことによって引き起こされます( E OT )。内部の金属ゲートは等電位面を提供します。デバイスは、容量性分圧器として同等にモデル化できます。総静電容量 C G 一連の C FE および C MOS 。内部ゲート電圧はNC効果により増幅されます。内部電圧増幅係数β =∣ C FE ∣ / ∣ C FE ∣ − C MOS | C のときに最大値を取得します MOS | =| C FE | [20、21]。 C の最適化されたマッチングの実現 FE および C MOS オン電流の改善の前提条件です。

統計的な a 私 DS および b G m パッシベーション持続時間が40分と60分のNCFETと制御MOSFETの結果

抽出された V int 対ゲート電圧 V GS 曲線を図5aに示します。 V int I という仮説により、NCトランジスタの数を抽出することができます。 DS - V int NCトランジスタの曲線は I とまったく同じです DS - V GS 制御装置の曲線。内部電圧増幅係数 dV int / dV GS 図5bに示します。 d V int / d V GS > 1は、 V の広い掃引範囲で達成されます GS 表面パッシベーションが40分のNCFETの場合、局所的な偏波スイッチングが原因で、測定プロセス中に制御デバイスよりもSSが急峻になります[22]。これは、図2bの前述の結果と一致しています。 60分のパッシベーションを持つNCFETの場合、内部電圧増幅係数d V int / d V GS V の範囲で> 1が達成されます GS V のダブルスイープの場合は<0V GS 、これは図3bの上昇したSSと一致しています。

a 抽出された V int V の関数として GS 曲線。 b V に対する内部電圧増幅係数 GS 曲線

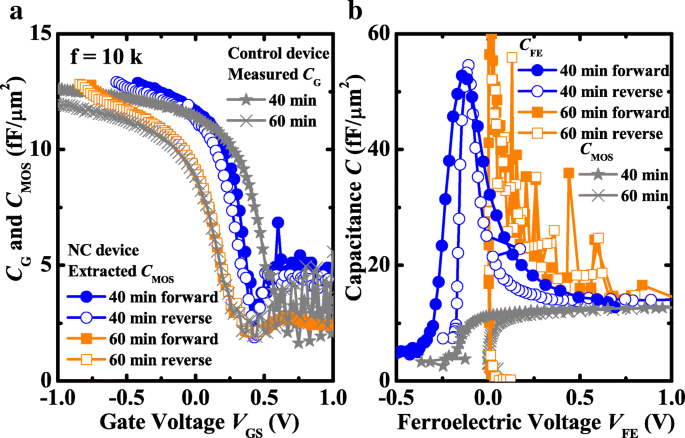

図6aは、抽出された C を示しています。 MOS 対 V GS V に依存しているNCトランジスタの曲線 int - V GS 図5aおよび C G - V GS 制御MOSFETの曲線。抽出された C MOS 測定された C とよく一致しています G。 したがって、計算方法の妥当性が実証されています。 C FE および C MOS 対 V FE 曲線は図6bに示されています。 NC効果の開始から、負の C の絶対値 FE トランジスタのが C を超えています MOS V のダブルスイープ用 GS 図6bでは常に。 | C FE |> C MOS および C FE <0は、ヒステリシスのない特性、および C のマッチングを引き起こす可能性があります。 MOS および C FE ロジックアプリケーションに有益です[23、24]。図1および2のヒステリシスのない特性。 2aと3aは、すべてのドメインマッチングと抑制された電荷トラッピングに起因することが観察されています[25]。安定した偏光スイッチングは、非ヒステリシス特性の原因です[26]。さらに、大きな内部ゲートゲインd V int / d V G > 1は、| C 間のわずかな不一致によるものです。 FE |および C MOS サブスレッショルド領域では、NCデバイスのSSが急になります。一方、 C の間にはより良いマッチングがあります FE および C MOS パッシベーションが60分のNCFETよりもパッシベーションが40分のNCFETの場合。したがって、これは、40分のパッシベーションを持つNCFETが60分のパッシベーションを持つNCFETよりも優れた電気的性能を持っていることを示す直接的な証拠を提供します。 FE分極は V を変更します FE ;したがって、FEの料金は異なります。総電荷は増加します。これは、 V の増分に加えてFE分極に起因します。 GS 。言い換えれば、与えられた V に対して GS 、チャネルの電荷が増加するため、 I DS 改善します。結果として、伝達特性の急なSSが実験に現れます。

a 測定された C G 抽出された C MOS V の関数として GS 。 b C FE および C MOS 対 V FE 曲線

結論

ヒステリシスのない伝達特性は、40分および60分のパッシベーションを持つNCFETで得られます。実験では、パッシベーションが40分のNC Ge pFETは、パッシベーションが60分のNCデバイスよりも優れた電気的特性を備えています。また、HZOベースのNCFETのNC効果も示します。 NCFETの場合、急勾配のSSとd V int / d V GS > 1が得られます。 40分のパッシベーションを備えたNCFETは、 C 間の良好なマッチングを実現しました。 FE および C MOS 、非ヒステリシス特性に寄与します。さまざまなNC動作は、FE薄膜の微視的磁壁スイッチングに関連していると考えられています。

データと資料の可用性

この記事の結論を裏付けるデータセットは、記事に含まれています。

略語

- B + :

-

ホウ素イオン

- E OT :

-

等価酸化物の厚さ

- FET:

-

電界効果トランジスタ

- HZO:

-

HfZrO x

- IC:

-

集積回路

- I-MOS:

-

衝突電離金属酸化物半導体

- MOS:

-

金属酸化物半導体

- NC:

-

負の静電容量

- NCFET:

-

負の静電容量電界効果トランジスタ

- NEMFET:

-

ナノエレクトロメカニカルFET

- S / D:

-

ソース/ドレイン

- SS:

-

サブスレッショルドスイング

ナノマテリアル

- トランジスタ、接合型電界効果(JFET)

- トランジスタ、絶縁ゲート電界効果(IGFETまたはMOSFET)

- 接合電界効果トランジスタ

- 絶縁ゲート電界効果トランジスタ(MOSFET)

- 接合型電界効果トランジスタ(JFET)の概要

- 絶縁ゲート電界効果トランジスタの紹介

- 電気触媒水素発生のための制御された厚さのMoS2

- 低抵抗Auオーミックコンタクトを備えた多層SnSeナノフレーク電界効果トランジスタ

- 分子動力学法によるアブレシブナノメートル切削プロセスに及ぼす衝撃方向の影響の研究

- 異なる粒子サイズのアベルメクチンナノデリバリーシステムの製造、特性評価、および生物活性

- 水性電解質中の対称スーパーキャパシタとしてのカーボンナノファイバーと活性炭の研究:比較研究