ステップチャネル厚のダブルゲートトンネル電界効果トランジスタのシミュレーション研究

要約

ダブルゲートトンネル電界効果トランジスタ(DG TFET)は、リーク電流とサブスレッショルドスロープの制限を拡張することが期待されています。ただし、対称的なソース/ドレインアーキテクチャによる両極動作にも悩まされています。両極電流を克服するには、ソースとドレインの間に非対称性を導入する必要があります。本論文では、2Dシミュレーションを利用して、ステップチャネル厚(SC TFET)を備えたDGTFETの性能を調査します。ソースとドレイン間の非対称性は、ステップチャネルの厚さによってもたらされます。したがって、両極の振る舞いは緩和されることが期待されます。結果は、SCTFETが従来のDGTFETと比較して両極電流の大幅な減少を示すことを示しています。 SC TFETのメカニズムは、物理的な洞察を探求するために徹底的に議論されています。構造パラメータによって導入電圧、サブスレッショルドスロープ、オン状態およびアンビポーラ状態のドレイン電流に生じる影響も、最適な構造を決定する際に示されます。

背景

極端なスケーリングプロセスが続くにつれて、従来のMOSFETを使用したCMOSテクノロジは、リーク電流の増加やサブスレッショルドスロープ( SS )などのさまざまな課題に直面します。 )。バンドツーバンドトンネリング(BTBT)メカニズムを利用するトンネル電界効果トランジスタ(TFET)は、リーク電流と SS の制限を拡張することが期待されています。 [1,2,3,4,5,6,7,8]。シリコンベースのTFETは、高い信頼性や低コストなどの利点を示します。ただし、従来のシリコンベースのTFETは、BTBTレートが制限されているため、MOSFETと比較して比較的低いオン電流を示します[9、10、11]。シリコンベースのTFETの可能性を開発するために、オン状態電流を強化するためのさまざまな新しいTFET構造が最近提案されています。ダブルゲートTFET(DG TFET)は、BTBTレートの向上を示し、オン電流の向上につながります[12、13、14]。ただし、アンビポーラ状態でもBTBTレートの向上が活性化されるため、DGTFETのアンビポーラ電流も増加します[15]。両極電流をさらに克服するには、ソースとドレインの間に非対称性を導入する必要があります[16]。ゲート-ドレインアンダーラップがあり、ドレインドーピング濃度が低いDG TFETは、両極問題を緩和するための一般的な方法です[17、18、19]。ただし、ゲート-ドレインアンダーラップには、より長いS / D距離が必要であり、ドレインドーピング濃度が低いと、直列抵抗が増加します[15]。以前の研究では、ドレインアンダーラップを備えたTFETの両極効果は、low-kスペーサーを使用し、接点を上下の構成に配置することでさらに緩和できることが示されています[15]。 TFETの性能を向上させます。以前の研究では、フィン幅が非対称のFinFETが、FinFETのパフォーマンスを向上させることが実証されています[20]。チャネルの厚さ t も考えられます si DGTFETのBTBT率に大きな影響を及ぼします[21]。したがって、ソースの厚さとドレインの厚さの非対称性により、両極電流がさらに緩和される可能性があり、徹底的に調査する必要があります。

本論文では、ステップチャネル厚(SC TFET)を用いたDG TFETのさまざまな性能を調査し、ソースとドレイン間の非対称性がステップチャネル厚を介して導入されるため、両極電流の低減が期待されます。このホワイトペーパーの残りの部分は、次のように構成されています。セクション2では、デバイスの構造とシミュレーションのセットアップについて説明します。セクション3では、SCTFETのメカニズムについて詳しく説明します。伝達曲線、開始電圧( V )に対する構造パラメータの影響に関する詳細な説明 発症 )、平均 SS オン/アンビポーラ状態のドレイン電流も表示されます。最後に、この論文の調査結果はセクションIVで啓蒙されています。

構造とシミュレーション

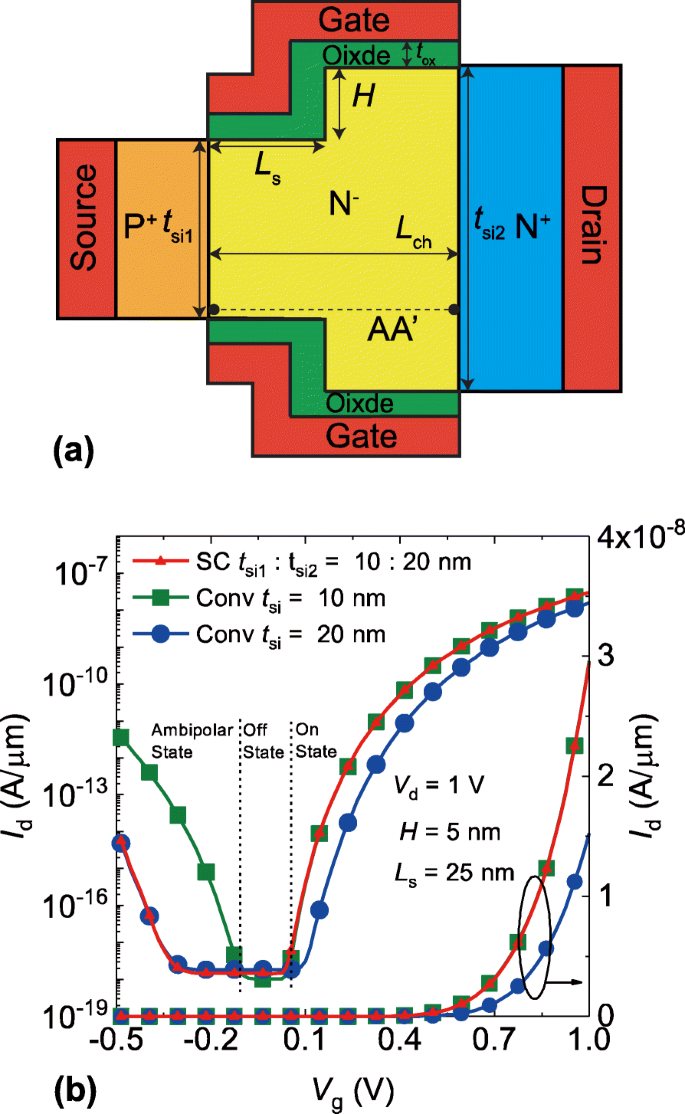

この論文で検討したSCTFETの回路図を図1aに示します。ソース領域の近くのチャネルの厚さは、ドレイン領域の近くのチャネルの厚さと等しくありません。チャネルの厚さは、チャネル領域の特定のポイントで段階的に変化します。ステップの高さとステップの位置は H で表されます。 および L s それぞれ。 t si1 および t si2 は、それぞれソース領域とドレイン領域の近くのチャネルの厚さです。シミュレーションでは、有効酸化物の厚さ(EOT)は1nmです。ソース領域は高度にpドープされています(10 20 原子/ cm 3 )およびドレイン領域は高度にnドープされています(10 20 原子/ cm 3 )直列抵抗を低減するために[15]、チャネル領域は軽くnドープされています(10 17 原子/ cm 3 )。さまざまなチャネル厚の設定で開始電圧を分析するために、金属ゲートの仕事関数は4.5 eVに固定され、ゲート長はチャネル長 L に等しくなります。 ch そして50nmに設定します[22,23,24,25]。シミュレーションは、SentaurusTCADリリースI-2013.12 [26、27]を使用して実行されます。ドーピング依存モデルとフィールド依存モビリティモデルは、それぞれフィリップスユニファイドモビリティモデルとロンバルディモビリティモデルです。フェルミ-ディラック統計、ショックリー-リード-ホールおよびオージェ再結合モデルも利用されます。高濃度にドープされたソース/ドレイン領域を説明するために、バンドギャップ狭小化モデルがアクティブ化されます。 [28]の実験結果で調整されたWentzel–Kramer–Brillouin(WKB)近似に基づく非局所BTBTモデルと密度勾配量子化モデルにより、正確なシミュレーションを実現できます[29、30]。開始電圧は、サブスレッショルド勾配が最大になるゲート電圧として定義されます。平均的な SS オフ状態の電流から I に抽出されます d =10 −11 A /μm。

a SC TFETの2D概略図、 t si1、および t si2は、ソース領域とドレイン領域の近くのチャネルの厚さであり、ソースとドレインの間に非対称性が明らかに導入されています。カットラインAA ’は水平方向に沿ったカットラインです。カットラインとソース領域の表面の間の垂直距離は0.5nmです。 b 対数および線形スケールでのSCTFETおよび従来のDGTFETの伝達曲線

結果と考察

転送曲線とメカニズム

図1bは、SCTFETと従来のDGTFETの伝達曲線をそれぞれ対数スケールと線形スケールで示しています。図1bで、オン状態、オフ状態、および両極状態をマークします。 TFETの場合、オン状態の電流を高くし、両極性状態の電流を低くすることが常に望まれます。これには、 V が必要です。 発症 および SS オフ状態は広い電圧範囲を持つ必要がありますが、ローである必要があります。図1bに示すように、 V 発症 チャネル厚が10nmの従来のDGTFETの場合、チャネル厚が20nmのDGTFETの場合よりも低くなります。抽出された V 発症 t を使用したDGTFETの si =10nmは0.04Vであり、抽出された平均 SS は44.8mV / dec、 V 発症 と平均 SS t を使用した従来のDGTFETの si =20nmはそれぞれ0.1Vと50.6mV / decです。 t を使用した従来のDGTFETのドレイン電流 si =10 nmは、 t を備えた従来のDGTFETと比較して94.7%向上しています。 si =20nm。このドレイン電流の改善の主な理由は、 SS の減少です。 および V 発症 。ただし、 t を使用した従来のDGTFETのオフ状態範囲 si =10nmはわずか0.17Vです。 t を備えた従来のDGTFET si =20 nmは、比較して、0.45 Vのオフ状態範囲を示します。その結果、 t を使用した従来のDGTFETの両極性状態電流 si =20 nmは、 t を備えた従来のDGTFETと比較して3桁減少します。 si =10nm。

公正な比較のために、 t si1 および t si2 SC TFETの数は、それぞれ上記の従来のDGTFETのチャネル厚に等しくなります。より狭いチャネルの厚さ t si1 SCTFETのは10nmで、チャネルの厚さはより広い t si2 SCTFETの20nmです。ステップの位置は、チャネルと L の中央にあると想定されます。 s 25nmです。 SC TFETは、オン状態での高いドレイン電流や広範囲のオフ状態など、有望な特性を示していることがわかります。オン状態のSCTFETのドレイン電流は、 t の従来のDGTFETと比較して類似しています。 si =10 nm、平均 SS は45.8mV / decで、 V 発症 は0.03Vです。ただし、SC TFETのオフ状態範囲は最大123.5%改善され、両極状態電流も、 t を備えた従来のDGTFETと比較して3桁減少します。 si =10nm。その結果、SC TFETのオン状態特性は、チャネル厚が狭い従来のDG TFETと同様であり、SC TFETは、チャネル厚が広い従来のDGTFETとほぼ平行なオフ/アンビポーラ曲線も示します。したがって、SCTFETは低い SS を達成できます。 、 V を減らしました 発症 、および広いオフ状態範囲を同時に。

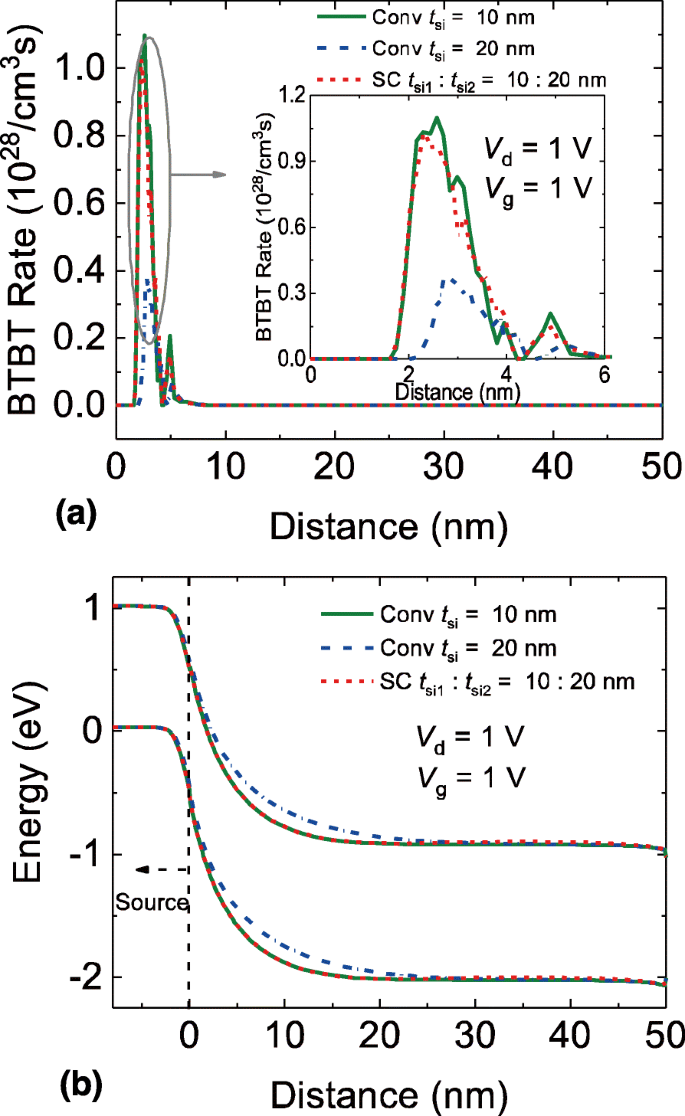

SC TFETの物理的メカニズムを調べるために、オン状態、開始点付近、および両極状態のBTBTレートとエネルギーバンド図をそれぞれ比較します。図2aは、SCTFETと従来のDGTFETのBTBTレートを示しています。 BTBTレートはチャネルの厚さに強く依存していることがわかります。実際、チャネルの厚さとBTBT電流の関係 I BTBT [31]と表すことができます。

$$ {I} _ {BTBT} \ propto \ exp \ left(-\ frac {4 \ lambda \ sqrt {2 {m} ^ {\ ast} {E_g} ^ {2/3}}} {3 \ mathrm {\ hslash} \ left(\ Delta \ Phi + {E} _g \ right)} \ right)$$(1)

a BTBTレートと b オン状態のSCTFETおよび従来のDGTFETのエネルギーバンド図、距離は図1のカットラインAA ’の横方向の位置です

ここでλ =(ε si t si t ox / 2 ε ox ) 1/2 は自然な長さ、ε si およびε ox はそれぞれシリコンと酸化物の誘電率であり、 t ox 酸化物の厚さです。 ΔΦ トンネリングが発生する可能性のあるエネルギー範囲、 E g はトンネル接合のバンドギャップであり、 m *はトンネリング質量です。式(1)は、 I BTBT t として増加するはずです si 減少します。したがって、 t を使用した従来のDGTFETのBTBTレート si =10 nmは、 t を備えた従来のDGTFETよりも大きくする必要があります。 si =20nm。 SC TFETは、 t を使用した従来のDGTFETと同様のBTBTレートの分布を示します。 si =10nm。これは、BTBTが主にオン状態のソースジャンクションの近くで発生するためです。したがって、ソースジャンクションの近くのチャネルの厚さがオン状態のBTBTレートを決定します。図2bは、SCTFETと従来のDGTFETのエネルギーバンド図を示しています。 BTBTレートは基本的にトンネル距離に関係しているため、トンネル距離を明確に示すことができるエネルギーバンド図は、BTBTレートの変動の原因を説明します。図2bでは、SC TFETの最小トンネル距離はソース接合の近くにあり、 t を備えた従来のDGTFETの最小トンネル距離とほぼ同じです。 si =10nm。 t を使用した従来のDGTFETの最小トンネル距離 si =20nmはかなり広いです。したがって、そのBTBTレートは、SCTFETおよびチャネルの厚さが薄い従来のDGTFETと比較して減少します。

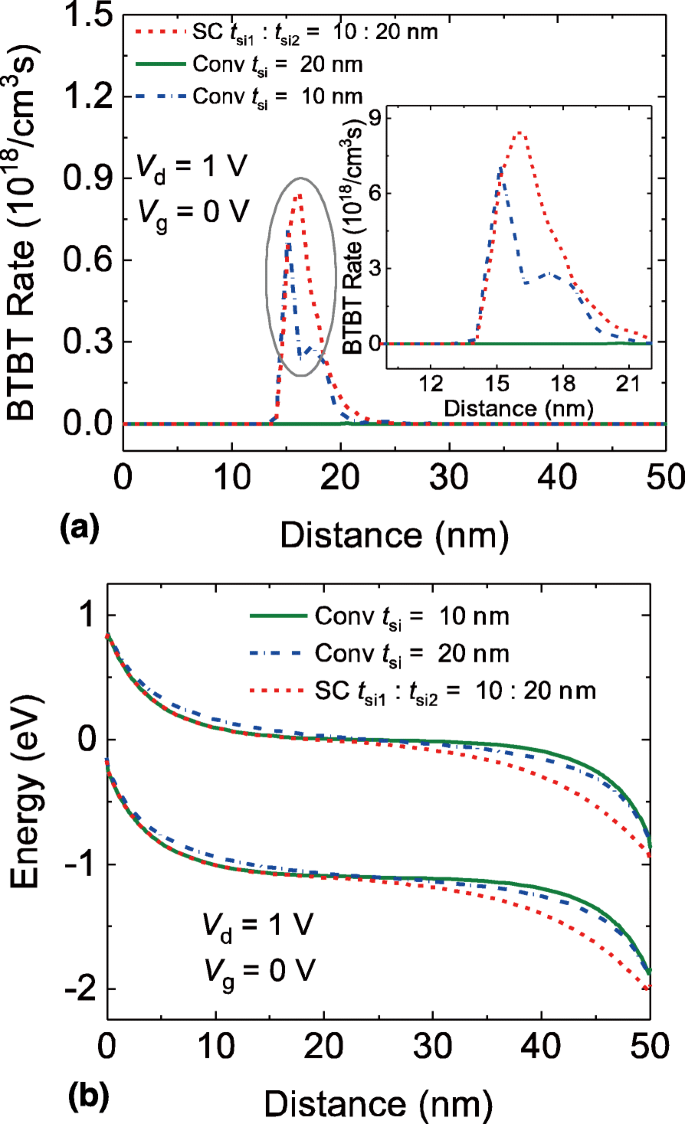

図3aは、ゲート電圧がゼロで開始電圧に近い場合のBTBTレートを示しています。 SC TFETが最も高いBTBTレートを所有し、次に t の従来のDGTFETが続くことがわかります。 si =10nm。 t を備えた従来のDGTFET si =20 nmは、最も低いBTBTレートを示します。図3bは、対応するエネルギーバンド図を示しています。価電子帯から伝導帯までの最小距離の位置がチャネル領域の中心にあることがわかります。また、チャネル厚が広い従来のDG TFETの最小距離は、チャネル厚が薄い従来のDG TFETおよび従来のDG TFETよりも長い。これは、チャネルの厚さも開始点でのBTBTレートに大きな影響を与えることを示しています。したがって、 V 発症 チャネルの厚さにも依存します。もう1つの事実は、SCTFETが t の従来のDGTFETよりも高いBTBTレートを示すことです。 si =最小チャネル厚が等しい場合でも10nm。この現象は、他の研究でも観察できるように、ゲート電極の角によって導入される電位分布の変動に起因します[32、33]。その結果、SCTFETは最低の V を示します 発症 に続いて、チャネルの厚さが薄い従来のDG TFETが続き、チャネルの厚さが広い従来のDGTFETが最も高い V を示します。 発症 。

a BTBTレートと b 開始点に近いSCTFETと従来のDGTFETのエネルギーバンド図。距離は図1のカットラインAAの横方向の位置です

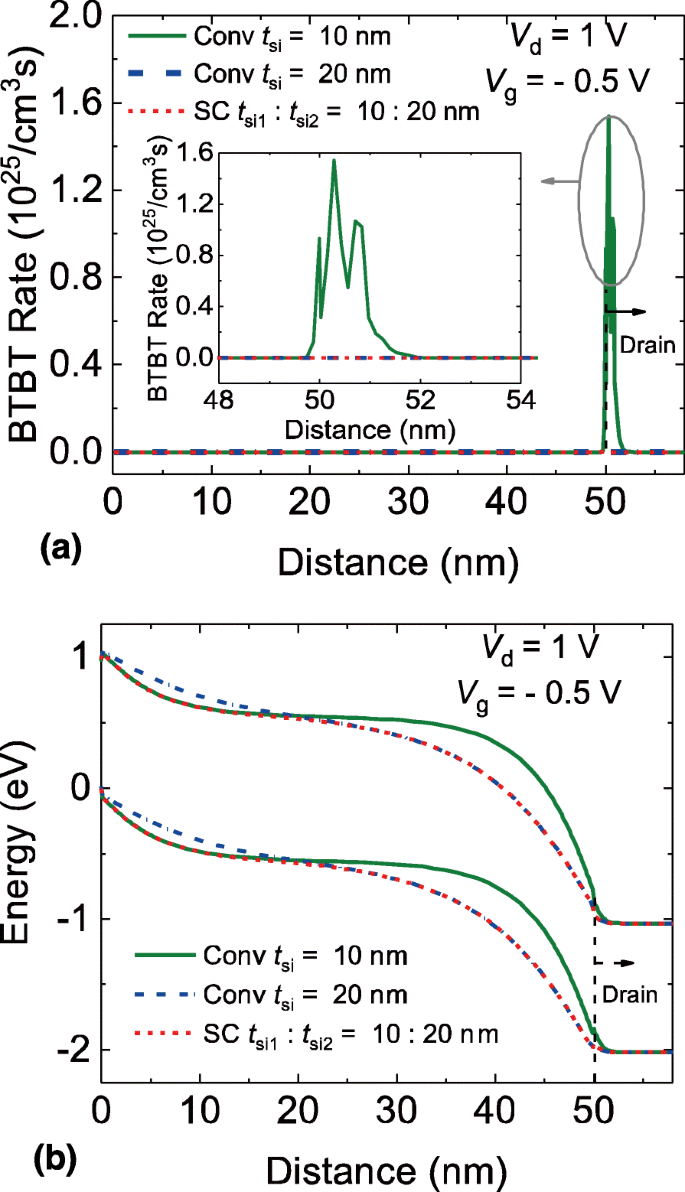

図4aは、両極状態でのBTBT率の比較を示しています。 BTBTレートはチャネルの厚さに強く依存するため、 t を使用する従来のTFET si =10 nmは、他の2つのTFET構造と比較して最も重要なBTBTレートを示しています。ただし、SC TFETは、 t を使用した従来のDGTFETと同様のBTBTレートを示します。 si =20nm。これは、トンネリングが主にドレイン領域の近くで生成され、SCTFETのチャネルの厚さがドレイン領域の近くで広くなっているためです。図4bには、両極状態のエネルギーバンド図も示されています。最小トンネル距離が排水区域の近くにあることがはっきりとわかります。さらに、チャネル厚が広い従来のDGTFETと従来のDGTFETのトンネル距離は、チャネル厚が薄い従来のDG TFETよりも長いため、チャネル厚が広い従来のDGTFETと従来のDGTFETの両極電流は低くなります。

a BTBTレートと b 両極状態のSCTFETおよび従来のDGTFETのエネルギーバンド図、距離は図1のカットラインAAの横方向の位置です

HとLの影響 S DC特性について

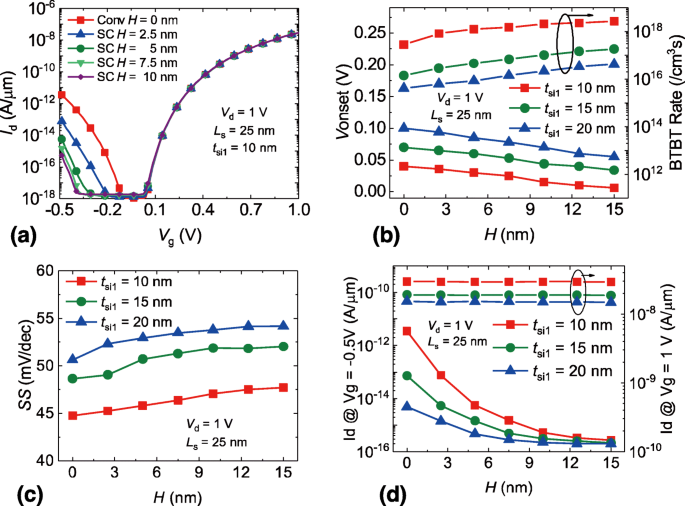

図5aは、さまざまな H を使用したSCTFETの伝達曲線を示しています。 および t si1 =10nm。 H オン状態の電流への影響は少なくなります。ただし、両極電流は H として大幅に減少します。 H の上昇に伴い、オフ状態の範囲が拡大します。 同様に。 H として、両極電流の減少が減少することもわかります。 増加します。この理由は、ダブルゲート構造の結合効果は、チャネルの厚さが大きいほど重要ではなくなる傾向があるためです[31]。したがって、 H として 増加すると、BTBTレートはチャネルの厚さに依存しなくなり、両極電流が飽和します。最適な構造パラメータをさらに調査するために、 H の効果 デバイスの性能は0から15nmまで変化し、抽出されて図5b–dに示されています。図5bは、 V を示しています。 発症 H が異なる場合のBTBTレートの変動 および t si1 。 V 発症 H の増加とともに単調に減少します 。これは、ゲート電極の角がチャネル領域の電位分布の変動をもたらし[32、33]、BTBTレートと V が変化するためです。 発症 。図5bは、BTBTレートが H として増加することを示しています。 改善します。その結果、 V が減少しました 発症 H を増やすと見つかります 。 V も観察できます 発症 t として増加します si1 増加します。主な理由は、 t の増加です。 si1 BTBTレートが弱くなり、 V が高くなります。 発症 。図5cでは、抽出された平均 SS さまざまな H を備えたSCTFETの および t si1 示されています。 SS のトレンド 異なる H V の反対です 発症 。言い換えれば、 SS H として上昇します 増加します。オン状態のドレイン電流は t に依存することを説明しました si1 、異なる H を持つSCTFETが しかし、同じ t si1 オン状態でも同様のドレイン電流が必要です。また、 V 発症 H の増加とともに減少します 。これは、同じドレイン電流を駆動するゲート電圧の範囲が H として改善されることを意味します。 増加します。その結果、平均的な SS H の上昇とともに単調に増加します 。 t の増加もわかります si1 SS を弱体化させます 、これはゲート制御機能の低下によるものです。図5dは、 H が異なるオン状態とアンビポーラ状態のドレイン電流を示しています。 および t si1 、 それぞれ。オン状態の電流は、 H にほとんど依存しません。 、ただし、 t の影響を大きく受けます si1 これは、オン状態のトンネリングが主にソース領域の近くで発生し、ソース領域の近くのチャネルの厚さに強く依存するという以前の結果に対応しています。ただし、両極電流は H として減少します。 増加します。両極状態のトンネリングはドレイン領域の近くで支配的であるため、 H の増加 ドレイン側のチャネルの厚さが改善され、アンビポーラ電流が弱まります。 H の場合、両極電流がより大幅に低下することもわかります。 は10nm未満です。これは、チャネルの厚さが薄いほど結合効果が大きくなるためです。

H の影響 a で 伝達曲線、 b V 発症率とBTBT率、 c 平均 SS 、および d オン/アンビポーラ状態のドレイン電流、 H はステップの高さであり、 H =0 nmは、従来のDGTFETを表します

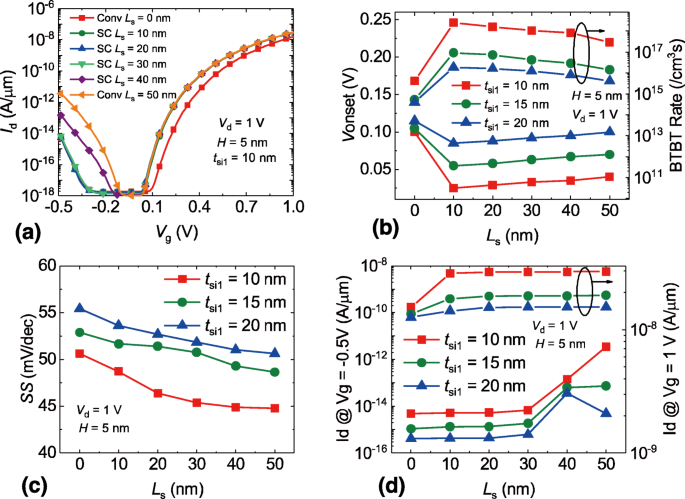

図6aでは、 L が異なるSCTFETの伝達曲線 s それぞれ提示されます。 L s =0 nmは、対応する t を備えた従来のDGTFETを表します si2 および L s =50 nmは、対応する t を備えた従来のDGTFETを表します si1 。ステップの位置が両極電流とオフ状態範囲に大きな影響を与えることがわかります。 L を備えたSCTFET s 30 nm未満では、同様の両極電流とオフ状態範囲が示されます。 L として s 30 nmを超えると、両極電流が大幅に向上します。図6bは V を示しています 発症 さまざまな L によるBTBTレートの変動 s および t si1 、 V のトレンド 発症 t として増加します si1 改善もはっきりと観察できます。 L の変曲点の変化 s =10 nmは、さまざまな t の結果です。 si1 。 L 以降 s =0 nmは、チャネルの厚さが厚い従来のDG TFETであり、BTBTレートが低下し、 V が増加します。 発症 そして減少したオン状態電流。従来のDGTFETの場合を除いて、 V 発症 SC TFETのは、 L として単調に増加します。 s これは、ステップチャネル構造によって引き起こされるBTBTレートの低下によるものです。図6cは、 L の影響を示しています s および t si1 SS で SCTFETの。増加した t si1 その結果、 SS が劣化します 。式によると。 (1)、チャネルの厚さが増加すると、ゲート電極間の結合効果が低下し、ゲート制御能力が低下し、 SS が増加します。 [12]。 L として s ドロップすると、チャネルの厚さが厚い領域が拡大し、全体的なゲート制御機能が弱まります。その結果、 L が減少しました s SS を弱体化させます 図6cではっきりと観察できるSCTFETの数。図6dは、 L が異なるオン状態とアンビポーラ状態のドレイン電流を示しています。 s および t si1 、 それぞれ。 SC TFETのオン状態電流は、対応する t を備えた従来のDGTFETとほぼ等しいことがわかります。 si1 。両極電流に関しては、 L のSCTFET s 30 nm未満は、対応する t を備えた従来のDGTFETと同様の電流を示します。 si2 。 L のとき s 40 nmに増加すると、両極電流が劇的に増加します。実際、 L を備えたSCTFETの場合 s =40nmおよび t si1 =20 nm、その両極電流は、 t を備えた従来のDGTFETの電流よりもさらに大きくなります。 si1 =20nm。これは、特にゲート電極の垂直部分がPN接合に近い場合に、ゲート電極の垂直部分がトンネル領域を強化できるためです[34]。 L s 両極電流を低減するためには、40nm未満にする必要があります。

L の影響 s a 伝達曲線、 b V 発症率とBTBT率、 c 平均 SS 、および d オン/アンビポーラ状態のドレイン電流、 L sは、ソース領域からステップまでの横方向の距離 L s =0 nmは、対応する t を備えた従来のDGTFETを表します si2および L s =50 nmは、対応する t を備えた従来のDGTFETを表します si1。

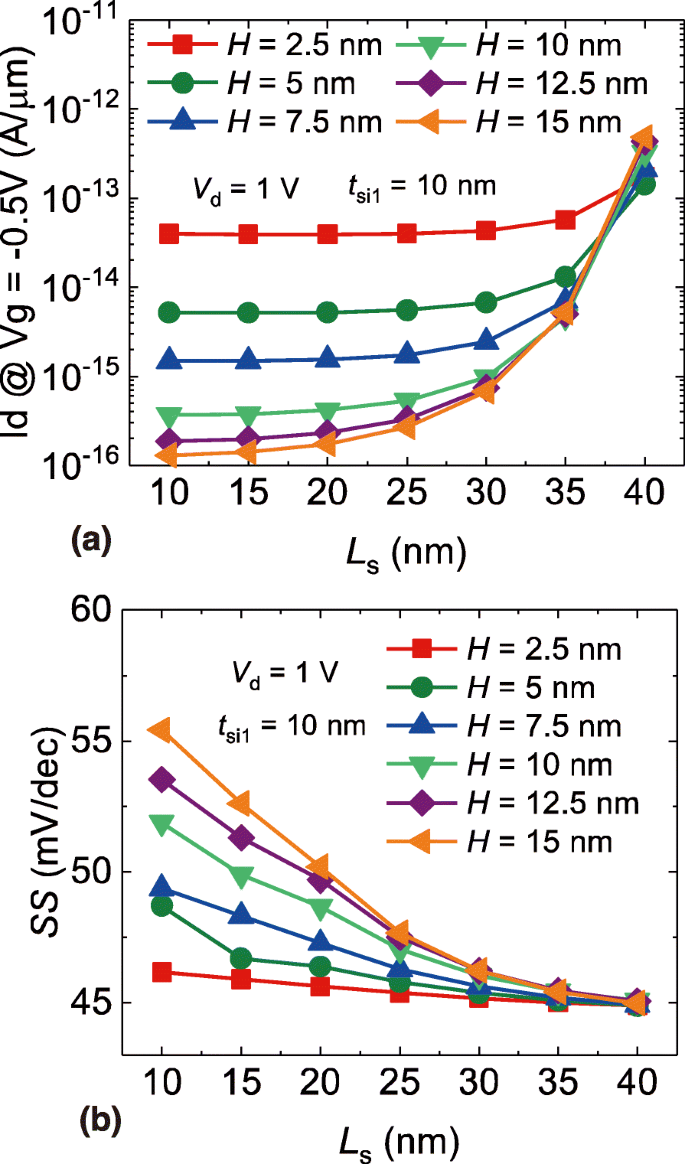

SC TFETの最適な構造パラメータを決定するために、 H の複合効果を調べることによって直交シミュレーションが実行されます。 と L s デバイスのパフォーマンスについて。 t si1 より大きなオン状態電流を実現するために、10nmに固定されています。図7aでは、両極電流が L の関数として抽出されています。 s さまざまな H 。 H として、両極電流が大幅に減少することがはっきりとわかります。 減少します。これは、 H が高いことを示しています。 より低い両極電流を達成するという点で有望です。ただし、 H を大きくすることによるメリットを確認できます。 それほど重要ではありません。したがって、 H H が大きいことを考慮すると、=15nmが最適値になります。 デバイス領域を増やすことしかできませんでした。一方、 L は減少しました s 特に H が大きい場合は、両極電流も低下します。 。したがって、より低い L s 最小の両極電流の目的のために望ましい。それにもかかわらず、より低い L s 図7bに見られるように、サブスレッショルド勾配の増加にもつながる可能性があります。 L が高くなると、サブスレッショルド勾配はゆっくりと増加します。 s ただし、 L が低くなると急速に上昇します s 、 L であることを示します s 約25nmが妥協値になります。その結果、最適なデバイスパラメータは H になります。 =15nmおよび L s =25 nmで、両極電流とサブスレッショルド勾配の両方が比較的低い。

a 両極電流と b L の関数としてのSCTFETのサブスレッショルド勾配 さまざまな H のS

製造方法

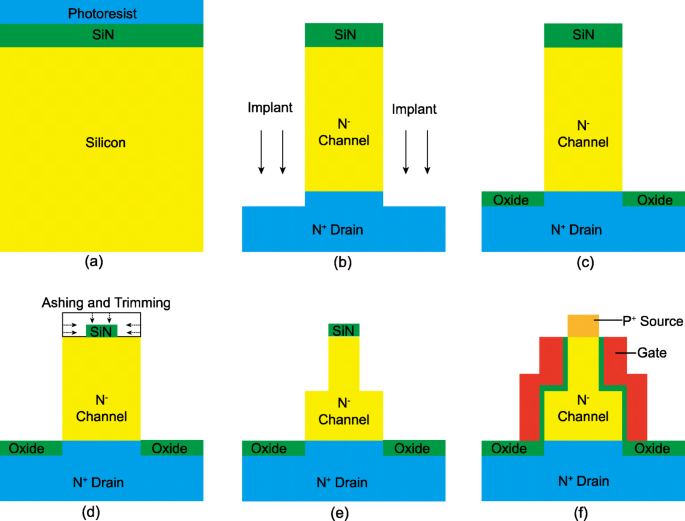

SC TFETの実現可能な製造プロセスを図8に示します。チャネルの形状が独特であるため、垂直構造を採用することにより、ステップチャネルの厚さをより簡単に実現できます。このプロセスは、図8aに示すように、SiNとフォトレジストの堆積でシリコン基板を準備することから始まります。図8bでは、SiNパターニングはリソグラフィによって達成され、続いてエッチングによってチャネル領域が形成され、次にN + 領域は垂直As注入とアニーリングによって導入されます[35]。その後、図8cに示すように、次のプロセスでドレイン領域がエッチングされるのを防ぐために、分離酸化物が堆積されます。図8dでは、反応性イオンエッチング[36]を利用してアッシングとトリミングを採用し、SiNの厚みと幅を小さくしています。次に、図8eに示すように、ステップチャネルの厚さがエッチングによって導入されます。残りのプロセスは、図8fに示すように、ゲート酸化物の形成、ゲートの堆積、シリコンの露出、およびソース領域の注入を含む従来の垂直TFETと同様です[35、37]。

SCTFETの製造プロセス。 a SiNとフォトレジスト蒸着によるシリコン基板の準備。 b エッチング、注入、およびアニーリング。 c 絶縁酸化物の堆積。 d アッシングとトリミングにより、SiNの厚みと幅を縮小します。 e ステップチャネルの厚さが導入されます。 f ゲート酸化物形成、ゲート堆積、ゲート平坦化、およびソース領域注入

結論

2Dシミュレーションを利用して、ステップチャネル厚(SC TFET)のDGTFETの電気的性能を調査します。ソースとドレイン間の非対称性は、ステップチャネルの厚さによってもたらされます。したがって、両極の振る舞いは大幅に軽減されます。 SC TFETは、対応する t を備えた従来のDGTFETと同様のオン状態特性を示します。 si1 対応する t を備えた従来のDGTFETの平行オフ/両極曲線 si2 。その結果、SC TFETは、広いオフ状態範囲、低い両極電流を実現し、低い SS を維持することができます。 同時に。 SC TFETのメカニズムは、物理的な洞察を探求するために徹底的に議論されています。最適な構造を決定するために、開始電圧、サブスレッショルドスロープ、オン状態のドレイン電流、および両極状態の構造パラメータによって導入される影響も調査されます。 H を備えたSCTFET 15nmおよび L s 25nmのは最適な性能を示しています。さらに、ステップチャネルの厚さのアーキテクチャは、代替の非対称方法を提供します。組み合わせた非対称戦略が効果的であることが証明されているので、私たちの仕事はTFETのパフォーマンスをさらに改善する可能性があります。

データと資料の可用性

すべてのデータは制限なしで完全に利用可能です。

略語

- DG TFET:

-

ダブルゲートトンネル電界効果トランジスタ

- SC TFET:

-

ステップチャネル厚のDGTFET

- SS :

-

サブスレッショルドスロープ

- BTBT:

-

バンド間トンネリング

- EOT:

-

有効酸化物の厚さ

- V 発症 :

-

開始電圧

- H :

-

ステップの高さ

- L s :

-

ステップ位置

- L ch :

-

チャネル長

- t si :

-

チャネルの厚さ

- t si1 :

-

ソース領域付近のチャネルの厚さ

- t si2 :

-

ドレイン領域付近のチャネルの厚さ

ナノマテリアル

- 部品の接続:FACE準拠のポータブルコンポーネントとシミュレーション環境の統合

- スイッチとしての接合型電界効果トランジスタ(JFET)

- 短チャネルMOSトランジスタの漏れ電流成分を理解する

- 銅原子の心に合わせて

- 電気触媒水素発生のための制御された厚さのMoS2

- ナノチャネルにおける油輸送に対する表面効果:分子動力学研究

- 新規ナノ粒子増強ワーム状ミセルシステムの研究

- デュアルゲートTFETに基づく無容量1TDRAMのプログラミング最適化

- HfO2欠陥制御層を備えた単層カーボンナノチューブが支配的なミクロンワイドストライプパターンベースの強誘電体電界効果トランジスタ

- V溝キャビティを備えたチャネルプラズモンナノワイヤレーザー

- T型ゲートデュアルソーストンネル電界効果トランジスタのアナログ/ RF性能