垂直トランジスタアプリケーション用のリンドープシリコン/シリコン-ゲルマニウム多層構造の成長と選択的エッチング

要約

垂直ゲートオールアラウンド電界効果トランジスタ(vGAAFET)は、3nmテクノロジノード以降の高度な集積回路製造テクノロジのFinFETに代わる可能性のある候補と見なされています。 Si / SiGe / Siの多層(ML)は、通常、垂直トランジスタを形成するために成長および処理されます。この研究では、Si / SiGe / SiへのPの取り込みと、これらのMLの垂直エッチングに続いて、横方向にSiGeを選択的にエッチングして、vGAAFETの構造を形成することを検討しました。 Si表面上のP原子のアクセスを枯渇させるための水素パージ、および/またはSiまたはSi 0.93 の挿入など、エピタキシーのためのいくつかの戦略が提案されました。 Ge 0.07 PドープSi層の両側にスペーサーを配置し、SiH 4 に置き換えます。 SiH 2 による Cl 2 (DCS)。実験結果は、PドープSiに7%Geを添加することにより、偏析と自動ドーピングも軽減できることを示しました。構造は良好な格子品質を有し、ひずみ緩和はほとんどありませんでした。 PドープSi(またはPドープSi 0.93 Ge 0.07 )およびSiGeについても、ウェットエッチングとドライエッチングを使用して説明しました。さまざまなエッチング方法の性能と選択性も比較されました。この論文は、垂直GAAFET構造におけるエピタキシーとn型層のエッチングの課題または困難に対処する方法についての知識を提供します。

はじめに

相補型金属酸化膜半導体(CMOS)のスケーリングが物理的な限界に達すると、短チャネル効果によってトランジスタの性能が大幅に低下します。これらの問題の解決策は、GAAFET(ゲートオールアラウンド電界効果トランジスタ)などの新しいトランジスタ設計です。これは、3nmテクノロジノードまでのナノスケールトランジスタの最も有望な候補と見なされています[1,2,3 、4、5、6]。 FinFETに代わるInternationalRoadmap for Device and Systems(IRDS)2020によると、横方向および縦方向のナノワイヤー/ナノシートが主要な構造です[7]。垂直GAAFET(またはvGAAFET)は、ゲート長に自由な柔軟性を備えており、集積密度を高める大きな可能性を秘めています[4、8]。垂直ナノワイヤ構造を実装するための2つの主要なカテゴリがあります:ボトムアップとトップダウン。ボトムアップ方式では金属触媒が導入され、プロセスの互換性の問題が発生する可能性があります[9、10]。トップダウン方式は、ナノワイヤ構成の制御が優れており、FinFETとの互換性があるため、業界の主流です[4、11、12、13、14]。垂直GAAFETを製造するトップダウン方式が大きな注目を集めています。正確なゲート長制御を備えた自己整合ゲートは重要な問題でした[15、16]。より効果的なゲート長制御を実現するため、またはばらつきを低減するために、ゲート長は主に、Si / SiGe / Siなどの底面にエピタキシャル成長させたチャネル材料の厚さによって決定でき、SiGeがチャネル材料でした[17、 18,19,20]。さらに、別の重要な統合の課題は、チャネル領域とS / D領域の間のドーピング[16、20、21]、特に鋭い接合制御[20]にあります。従来のソース/ドレイン注入プロセスと比較して、エピタキシープロセスは製造プロセスを簡素化し、表面の損傷を減らし、均一なドーピングプロファイルを実現します。ただし、PドープSi / SiGe / PドープSiサンドイッチ構造は、最も一般的なn型ドーパントであるリンの偏析、自動ドーピング、および外方拡散現象のために、エピタキシャル成長が困難です[22、23]、化学蒸着(CVD)システムのSi / SiGe界面でのヒ素[24、25]、および/またはアンチモン[26、27]。したがって、Si / SiGe界面とSiGe層に集まった偏析したドナー原子がドープされ、リークが大きくなりトランジスタの性能が低下する可能性があります。

ドーパントの分離を妨げる1つの戦略は、非常に低い成長温度を適用することです。分子線エピタキシー(MBE)によるn型ドーピングを成長させるために多くの努力をする一連の報告があります[28]。一方、この方法はCVDには適用されていません。 MBE機器はほとんどがシングルチップ設計であり、高真空と低速スループットが必要です。さらに、MBE機器は、業界で8インチを超えるウェーハサイズと互換性がありません。したがって、MBEテクノロジーは工業用の大量生産アプリケーションには適していません。しかし、RPCVDシステムは強力な生産能力とシンプルな装置構造を備えており、IC産業に適しています[29]。水素はキャリアガスであり、前駆体ガスの反応速度に影響を与える可能性があるため、RPCVD成長の最初のアイデアはチャンバー内の水素の流れを調整することです。 Li et al 。 [23]は、水素が表面のホスト原子の結合構造を変化させ、急速熱CVD(RTCVD)システムで低い成長温度を適用することによって偏析エネルギーを減少させたことを報告しました。ただし、水素の影響は、減圧CVD(RPCVD)システムのSi / SiGe界面では調査されていません。 Suvar et al 。 [30] PドープSiとSiGeの間に30nmの非ドープSiスペーサー層を挿入して、界面のP濃度を4分の1に下げました(8×10 19 cm -3 〜2×10 19 cm -3 )が、Pドーピングピークを排除することはできません。ベネット他。 [31]は、Siのn型ドーピングに対するひずみの影響を研究しています。ドーピングの固溶度は、Siに引張ひずみを導入することによって増加しました。 Christensen et al 。 [32]は、Si 1-x のGe含有量に対するP拡散係数の有意な依存性を発見していません。 Ge x (0≤x≤0.22)。また、P拡散係数は緩和Siと二軸圧縮ひずみSiGeの間にほとんど違いがありませんでした。 Zangenberg et al 。 [33]は、緩和されたSi 0.88 について、825°Cで拡散係数が2倍に向上することを観察しました。 Ge 0.12 。

この論文では、RPCVDを使用してSi / SiGe / Siの多層膜におけるSiへのPの取り込みを改善するためのいくつかの方法が提案されています。実験では、水素パージ、ドープされていないスペーサー層の挿入、SiH 4 からのSi前駆体の変更などのさまざまな戦略があります。 SiH 2 へ Cl 2 (DCS)、およびSi 0.93 を導入することによってひずみプロファイルを変調する Ge 0.07 SiGe層の両側の犠牲層が提示されています。さらに、SiGeの選択的エッチングが薄いSiGe層(チャネル層として意図されている)を形成するために議論されました[6、34]。ウェットエッチングツールとドライエッチングツールのエッチング特性も比較しました。最終的な構造は、将来、サブ10nmテクノロジーノードのvGAAFETに使用されることを目的としています。

メソッド

Si / SiGe / Si多層膜(ML)は、RPCVD(ASM Epsilon 2000)装置を使用して200 mm Si <100>ウェーハ上で成長させました。 Si基板はH 2 の混合溶液で洗浄されました。 SO 4 およびH 2 O 2 、エピタキシーチャンバーのロードロックに挿入する前に、希釈したHFを使用して自然酸化物を除去します。サンプルは、1050°Cでアニーリングして自然酸化物を除去し、高品質のSi表面を得ることにより、その場で洗浄しました。 Si、Ge、およびPの前駆体はSiH 4 でした。 (またはSiH 2 Cl 2 )、10%GeH 4 H 2 で 、および2%PH 3 H 2 で 。エピタキシー中、チャンバー圧力は80 Torrに保たれましたが、成長温度は650°Cでした。一部の実験では、チャンバー圧力を10 Torrに下げて、PドープSi 0.93 を成長させました。 Ge 0.07 ソース/ドレイン(S / D)領域のレイヤー。 SiGeチャネルのGe含有量は0.22に一定に保たれました。選択的エッチング特性を研究するために、50nmの窒化物/ 30nmの酸化物をハードマスクとして堆積させてネザーMLを保護しました。リソグラフィーと乾式異方性垂直エッチングを実行して、別々の直方体パターンを形成しました。選択的エッチング実験は、HF(6%):H 2 のウェットエッチングツールを使用して実行されました。 O 2 (30%):CH 3 COOH(99.8%)=1:2:4およびCF 4 のドライエッチングツール :O 2 :He =4:1:5 [35]。

Si / SiGe / Si MLは、高解像度(Thermo Scientific Talos F200)透過型電子顕微鏡(HRTEM)、エネルギー分散型X線分光法(EDX)、高解像度X線回折(HRXRD)の手法によって特徴づけられました。 、およびBruker JV Delta-xの高解像度相互格子マップ(HRRLM)、日立(日本)の走査型電子顕微鏡(SEM)、および二次イオン質量分析(SIMS)。

結果と考察

PドープSi / SiGe / SiMLのエピタキシー

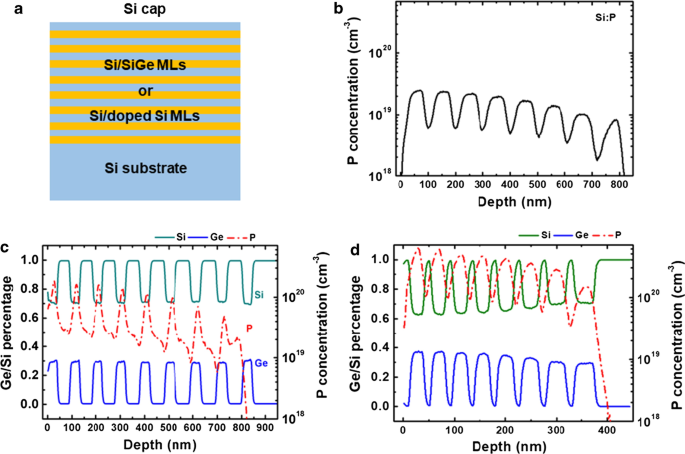

この研究では、SiとSiGeへのPの取り込みが最初に調査されました。 ML構造を図1aに示します。 PH 3 の増加に伴うPドープSi /非ドープSiのML 流れを成長させ、層のプロファイルを図1bのSIMSで調べました。この図は、P濃度が増加し、2.6×10 19 の最高レベルに達することを示しています。 cm -3 。 「PドープSi / Si 0.72 」のプロファイルを持つさらに2つのサンプル Ge 0.28 / PドープSi」および「Si / PドープSi 0.72 Ge 0.28 / Si ’が設計され、Pプロファイルがそれぞれ図1c、dに示されています。図1cでは、PドープSi / Si 0.72 の界面でPパイルアップが観察されています。 Ge 0.28 多層。界面のPパイルアップは、多層膜の下部から上部に向かってP濃度が増加するにつれて増加し、最高濃度は1.6×10 20 です。 cm -3 、これは図1bの濃度の6倍です(2.6×10 19 cm -3 )。ドープされたSi 0.72 Ge 0.28 層(図1d)では、P濃度が著しく高く、界面にピークがありません。ドーピングにより、Geの割合がわずかに増加します。この動作は、SiH 4 の吸着の強化に関連しています。 およびGeH 4 PH 3 の存在下で 。また、ドーピングにより、成長時間が同じ図1c、dでは層の厚さが異なります。これは、PドーピングがSi 0.72 の成長速度を高めることを意味します。 Ge 0.28 層とGeH 4 の吸収 、一方、Siの成長速度はP吸着のために遅くなります。これらの現象は、Refsで報告された結果と一致しています。 [36,37,38]。以上のことから、Si / SiGe界面ではP偏析と自動ドーピング現象が深刻である。 Si / SiGe界面のPドーピングピークは、SiGe層に意図しないドーピングを引き起こします。 SiGeはトランジスタのチャネル層として意図されているため、不均一なドーピングプロファイルまたは高いバックグラウンドドーピングレベルはデバイスアプリケーションを制限します[39]。 Pピークを除去するためのいくつかの方法を以下で説明します。より良い比較のために、すべてのSiGe層が歪んでおり、SiH 4 の流量比が (SiH 2 Cl 2 )およびGeH 4 SiGe層は、すべての実験を通じて変更されたわけではありません。

a PドープSi / SiGe / SiMLの概略図。 b ドープされていないSi / PドープされたSiMLのPドーピング濃度。 c のGe / SiパーセンテージとP濃度 ドープされていないSi 0.72 Ge 0.28 / PドープSi、 d ドープされていないSi / PドープされたSi 0.72 Ge 0.28 ML。パージおよびドープされていないスペーサー層は考慮されませんでした

スペーサーレイヤーの影響

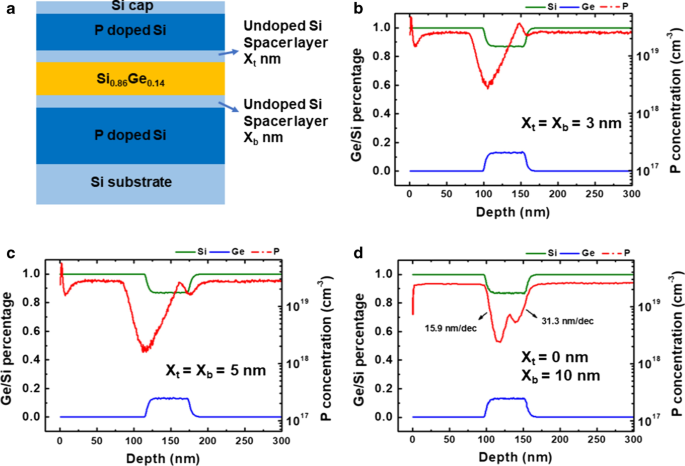

下部にドープされたSi層とドープされていないSiGe層の間に、ドープされていないSiスペーサー層を挿入して、過剰なP原子を吸収しました。図2aは、設計された構造の概略図を示し、図2b–dは、(b)3 nm、(c)5 nm、および(d)10nmの厚さの統合Siスペーサーからのプロファイル結果を示しています。図2b–dのように、Si層のSi / GeパーセンテージとP濃度が一定に保たれている間、Pパイルアップのピークは減少します。 Pパイルアップレベルは4×10 19 から82%減少します cm -3 図2bから7×10 18 cm -3 図2dで、スペーサーの厚さが X の場合 b 3nmから10nmに増加しました。ドープされていないSiスペーサー層の厚さを増やすと、過剰なP原子の吸収が増加します。図2dでは、Si 0.86 でのPプロファイルの傾き Ge 0.14 / Si表面は15.9nm / decですが、Si / Si 0.86 Ge 0.14 インターフェースの傾きは31.3nm / decです。一方、シート抵抗が増加するため、厚すぎるSiスペーサー層は適切な解決策ではありません。したがって、トランジスタの場合、シート抵抗と制御されていないPプロファイルとの間のトレードオフを行う必要があります。図2は、Si / Si 0.86 間のスペーサー層の影響も示しています。 Ge 0.14 レイヤー( X b )Si 0.86 間の層とは異なります Ge 0.14 / Si( X t )。図2b、cでは、Si 0.86 間のスペーサーの厚さ Ge 0.14 / Siは3nmと5nmでしたが、図2dではスペーサー層は挿入されていません。ただし、Si 0.86 でのPプロファイルの傾き Ge 0.14 / Siは同じ(約15.9 nm / dec)ですが、図2dでは上部のスペーサー層が除去されていますが、ドーピングプロファイルへの影響は観察されませんでした。上記の結果から、PピークはSi / Si 0.86 のみでした。 Ge 0.14 おそらく溶解限度によるものである界面。過剰なP原子は、表面でP–Pダイマーを形成し、SiGeキャップ層に組み込まれる可能性があります。さらに、PをドープしたSiの後のSiGe成長中にPの自動ドーピングがあります。そのため、過剰なP原子を除去したり、Siの溶解度を向上させたりする方法が模索されてきました。

a 異なるドープされていないスペーサー層を備えた実験サンプルの概略図。また、PドープSi / Si 0.86 のGe、Si、Pプロファイル Ge 0.14 b のドープされていないSiスペーサー層を備えた/ PドープされたSiML 3 nm、両方のインターフェースで、 c 5 nm、両方のインターフェースで、 d 10 nm、Si 0.86 との1つのインターフェースのみ Ge 0.14

Si / SiGe / SiMLの界面での水素パージの影響

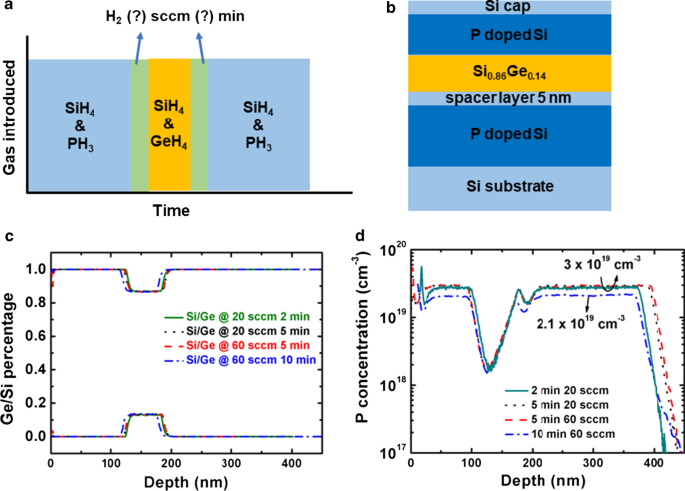

このセクションでは、Siスペーサー層を5 nmに固定し、水素パージを導入して、PドープSi成長後に過剰なP原子を除去しました。図3c、dから、水素流量を20から60 sccmに増やし、パージ時間を2から10分に増やしても、Pピークに明らかな影響がないことがわかります。 Siのドーピング濃度は3×10 19 です。 cm -3 、これは「スペーサーレイヤーの影響」のセクションで説明したものと同じです。界面でのPピーク濃度は、図3dのSiの濃度と同じです。層の厚さは、異なるパージ条件で同じです。 P原子は水素によって除去できません。これは、表面に安定したP錯体が形成されることで説明できます。温度、圧力、パージ時間などのパラメータを変更することで役立ちます[24、40]が、時間コストのためにパージ時間が長すぎると適切ではなく、高温(> 950°C)はSi-Ge相互拡散を引き起こします[41]。 。

a の概略図 H 2 のドーピング戦略 パージ条件、および b Si / SiGe / SiMLの実験構造。 c Ge / Siプロファイルと d PドープSi / Si 0.86 のP濃度 Ge 0.14 / PドープSiML

P-incorporationに対する成長化学の影響

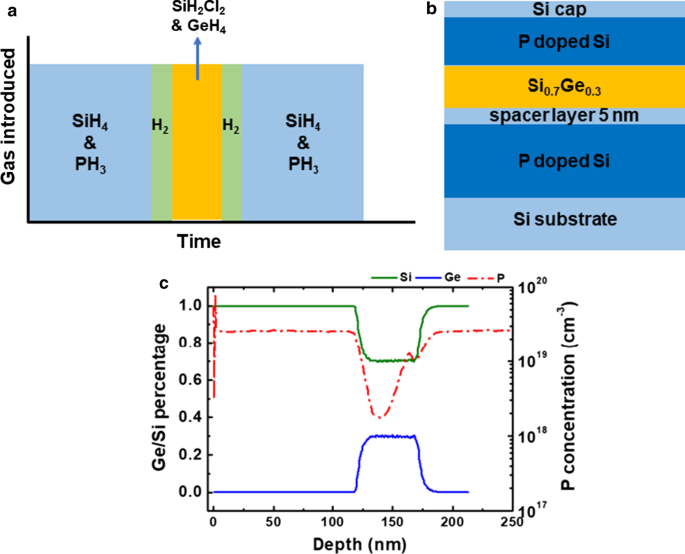

これらの実験では、Si前駆体であるSiH 4 、SiH 2 に置き換えられました Cl 2 (DCS)。これらのサンプルでは、成長パラメータは以前と同じであり、構造には5 nmのSiスペーサー層が含まれており、パージ時間は5分、流量は60sccmです。背後にある考え方は、Clベースの化学がSi表面によって過剰なP原子を除去でき、P-Cl、Si-Cl、またはGe-Clの反応が発生する可能性があるかどうかを調査することです[42]。図4から、Pピーク濃度は2分の1に減少します(2.6×10 19 から) cm -3 〜1.3×10 19 cm -3 )、Si層のP濃度は2.6×10 19 cm -3 。推定Ge含有量は30%であり、SiH 4 を使用したSiGeよりも高くなっています。 。より高いGe含有量は、Clが表面反応で好ましくはSi原子を除去したことを示しています。この結果は、ガス流量比とGe濃度のSiH 4 との異なる関係によっても説明できます。 およびSiH 2 Cl 2 ガス状前駆体[32、43]。別の説明は、Ge原子が水素脱着を増加させ、次に自由核生成サイトを増加させたというものでした[44]。 Si 0.7 のP濃度勾配 Ge 0.3 / Siインターフェースは13.2nm / decで、Si 0.86 よりも少しシャープでした。 Ge 0.14 / Siインターフェース(15.9 nm / dec)。 Si / Si 0.7 でのPプロファイルの傾き Ge 0.3 インターフェースは20nm / decでした。したがって、より多くのHClを導入するか、SiH 2 のガス比を増やすことによって Cl 2 およびGeH 4 、ドープされたSi表面で分離されたP原子は、HClによってエッチングされてP-Clダイマーを形成し、Si / SiGeでのPピーク濃度が低くなる可能性があります[38、45]。

a の概略図 成長化学を変化させるドーピング戦略、 b Si / SiGe / SiMLの実験構造。 SiGe層はDCSで成長しました。パージ時間は5分で、Siをドープした後の流量は60sccmでした。ドープされていないSiスペーサー層は、ボトムドープされたSiとドープされていないSiGeの間で5nmでした。 c PドープSi / Si 0.7 のGe / SiプロファイルとP濃度 Ge 0.3 / PドープSiML

GeコンテンツがPプロファイルに与える影響

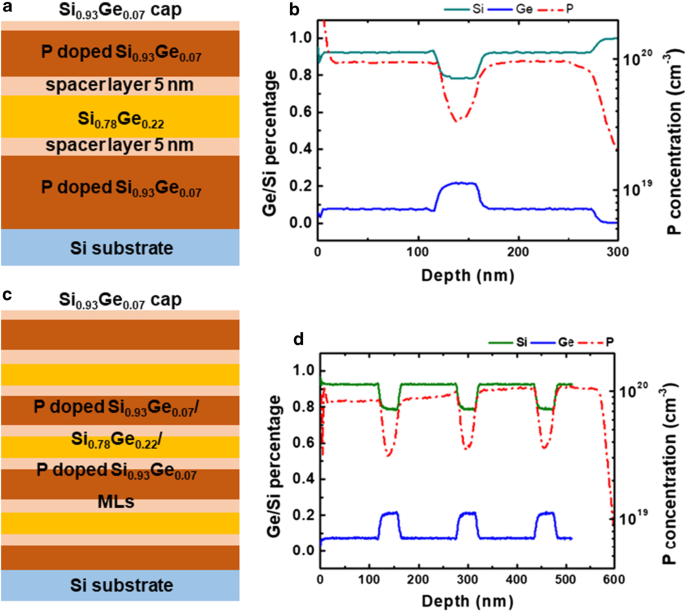

前に説明したように、SiGeへのPの取り込みはSiよりも著しく高かった。したがって、これにより、Siスペーサー(5 nm)に数パーセントのGe(7%)を追加すると、SiへのPの取り込みが改善される可能性があります。ここで言及する価値があるのは、私たちの目的は、PをドープしたSiの特性を大幅に変えることではなく、Si中のPの偏析を妨げることです。これらのサンプルでは、スペーサー層の成長中にチャンバー圧力が10Torrに低下しました。この条件では、ドーピングに依存する成長速度とGeの割合が重要になります。図5bから、上層と下層は110 nm Si 0.93 でした。 Ge 0.07 P濃度が1×10 20 cm -3 、中間層は40 nm Si 0.78 Ge 0.22 P濃度3.5×10 19 cm -3 。 PドープSi 0.93 のP濃度勾配 Ge 0.07 / Si 0.78 Ge 0.22 約33nm / decでした。 2つの層の間のGeパーセンテージの差が十分に大きくなかったため、傾斜は鋭くありませんでした。図5dでは、3層のPドープSi 0.93 Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 MLは、ドーピングの均一性を検証するために成長し、その構造図を図5cに示しました。下層から上層にかけて、P濃度が低下していることがわかります。これは、Pのメモリー効果によって説明できます。チャンバー内の残留P原子または拡散したP原子がフィルム表面に蓄積し、上の自由な活性部位をブロックします。表面[38、39]。 Pピークは排除されましたが、Si 0.78 間の分離 Ge 0.22 およびSi 0.93 Ge 0.07 まだ深刻でした。

a 概略図、 b PドープSi 0.93 の1層のGe / SiおよびPプロファイル Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 ML。 c 概略図、 d PドープSi 0.93 の3層のGe / SiおよびPプロファイル Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 ML

Si / SiGe / SiMLの選択的エッチング特性

ML構造が正常に成長すると(上記の成長戦略を使用)、SiO 2 を使用した垂直エッチングによってNWが形成されます。 ハードマスクとしての/ SiN。その後、SiGe層を横方向にSiに選択的にエッチングして、設計された幅のチャネル層を形成する必要があります。これらの実験では、2種類のML構造が選択されています。PドープSi / SiGe / PドープSi(図2cのサンプル1)とPドープSi 0.93 Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 (サンプル2、図5b)。これらの選択は、Pの外部拡散が(部分的に)抑制されている上記の説明に従って行われ、デバイスアプリケーションの観点も考慮されています。

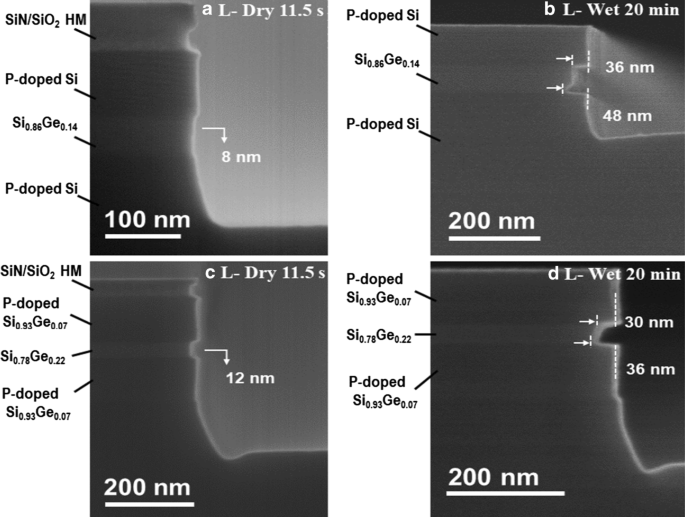

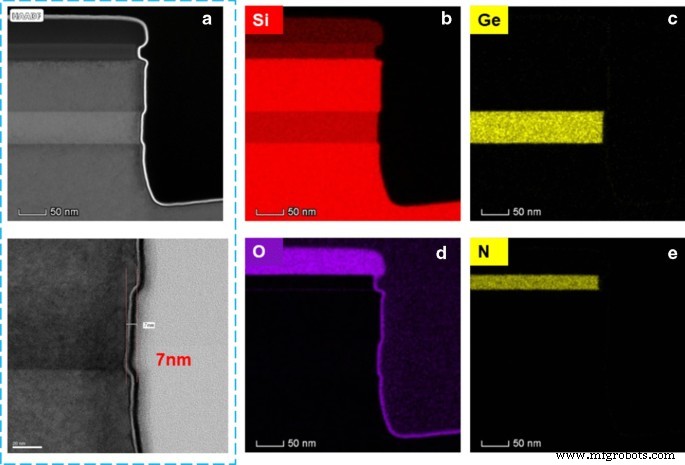

垂直方向のエッチングはドライエッチングによって行われ、横方向のエッチングには選択的なドライまたはウェットエッチングが適用された。サンプル1のエッチングプロファイルを図6a、bに示します。また、図6aのTEM画像とEDSマッピングを図7に示します。これらの実験では、ハードマスクは酸化物/窒化物です。図6aは、CF 4 の11.5秒のドライエッチング後を示しています。 / O 2 /彼。 Si 0.86 のエッチング選択性 Ge 0.14 PドープSiは5.8です。図6bは、HF(6%)/ H 2 の20分のウェットエッチング後を示しています。 O 2 (30%)/ CH 3 COOH(99.8%)。ウェットエッチングによりハードマスク(SiO 2 / SiN)、その結果、Siキャップ層もエッチングされました〜10nm。 「スペーサー層の影響」のセクションで説明したように、PドープSi / Si 0.86 にはPパイルアップがあります。 Ge 0.14 インターフェース。ウェットエッチングはドーピングレベルに敏感です。したがって、最初のインターフェースはより速くエッチングされました。その結果、フロントエッチングインターフェースは垂直ではなく、ファセットまたは角度が付けられています。平均選択性は4.2未満でした。 2つのエッチング方法を比較すると、ドライエッチングはGeの割合に敏感で、SiGeの選択性が高く、ウェットエッチングはドーパント濃度に敏感です。サンプル2のエッチングは、図6c、dでも調べられます。このサンプルでも同様の現象が観察されましたが、Geの割合が高いため、SiGeの選択的なエッチング深度が深くなりました(図6a、c)。ドライエッチングでは、Si 0.78 の選択性 Ge 0.22 およびPドープSi 0.93 Ge 0.07 は6.3でしたが、ウェットエッチングでは、平均選択性は2.5未満でした。したがって、エッチングの均一性と選択性を考慮すると、ドライエッチングの方が適しています。

PドープSi / Si 0.86 のSEM画像 Ge 0.14 図2cの/ PドープSiと a 11.5-sドライエッチング、 b 20分のウェットエッチング、およびPドープSi 0.93 Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 c のML 11.5-sドライエッチング、 d 20分のウェットエッチング。ドライエッチングはCF 4 でした :O 2 :He =4:1:5、ウェットエッチングはHF(6%):H 2 O 2 (30%):CH 3 COOH(99.8%)=1:2:4

a TEM画像、 b – e PドープSi / Si 0.86 のEDSマッピング Ge 0.14 図6aの/ PドープSi、11.5秒のドライエッチング。 b の要素 c のSiです d のGeです はOであり、 e N

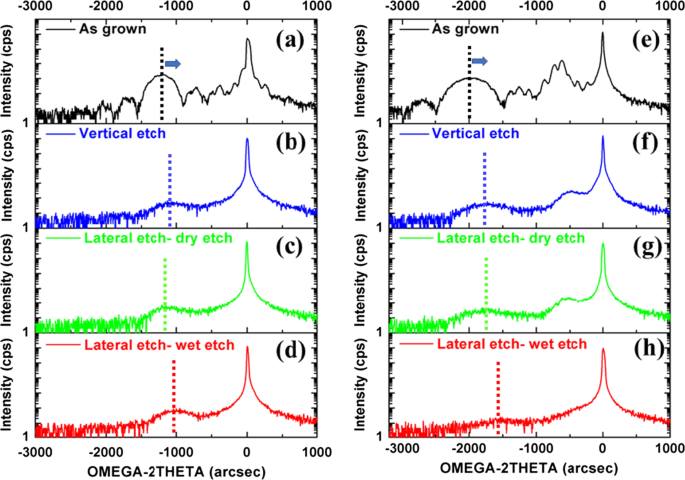

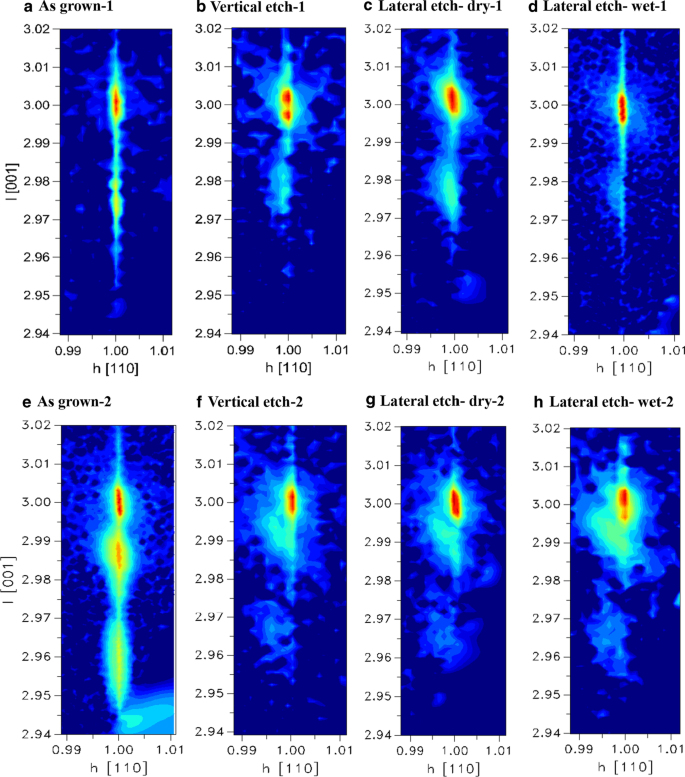

ですサンプル1とサンプル2のエッチングステップ後のひずみを調査するために、さらに分析が行われました。図8a–hは、これらのサンプルの(004)ロッキングカーブ(RC)を次のように示しています。成長時、垂直エッチング後、およびウェットエッチングとドライエッチングを使用したSiGeラテラルエッチング。 RC解析では、広がり(半値全幅またはFWHM)が欠陥密度の指標であり、Siと比較したSiGeピークの位置が層のひずみ量を決定します。ここで強調するのは、ピークの広がりは層の厚さが薄いためでもある可能性があるということです。したがって、欠陥密度の寄与をRC分析と区別することは困難ですが、これらの分析の一部の拡張でFWHMを比較することしかできません。これらのRCでは、サンプル1(図8a〜d)に単一のSiGe層があります。一方、サンプル2(図8e–h)は、7%と22%のGeを表す2つのピークを示しています。成長したままのサンプルでは、X線ビームの干渉が観察され、厚さの層の縞が発生します。これらのフリンジの出現は、高品質のSiGe / Siインターフェースを示しています。サンプル1とサンプル2のRCでは、GeピークがSi基板ピークに向かってシフトしており、ひずみ緩和を示しています。 SiGeの横方向のドライエッチング後、Geピークのそれ以上のシフトは検出されていません。チャネル領域のキャリア移動度は歪みに依存するため、これはトランジスタの性能にとって有望な結果です。一方、ウェットエッチングされたSiGeではひずみが緩和され、基板ピークへのシフトが大きくなっています。これは、ウェットエッチングが横方向のSiGeエッチングに適していないことを示しており、チャネル層を形成しています。

サンプル1の(004)反射周辺のHRXRDロッキングカーブ、PドープSi / Si 0.86 Ge 0.14 a に5nmのスペーサー層を備えた/ PドープSiML – d 、およびサンプル2、PドープSi 0.93 Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 e のML – h 。 2つのサンプルの両方に4つのパネルがあります。成長すると、垂直エッチング後、HF(6%)/ H 2 のSiGe横方向ウェットエッチングが行われます。 O 2 (30%)/ CH 3 COOH(99.8%)20分、CF 4 の横方向ドライエッチング / O 2 /彼11.5秒

図9a〜hのサンプルの欠陥密度に関する詳細情報を見つけるために、さらにX線分析が実行されました。図9a〜hに示すように、ここでは2次元測定に基づくHRRLMが実行されました。 HRRLMの欠陥密度の指標は、ω方向に沿ったSiGe層の広がりです(ωは入射ビーム角です)。 SiとSiGeのピークの位置は、成長方向に平行および垂直なひずみ成分を提供します。サンプル1とサンプル2では、成長したままのSiGe層はわずかなωの広がりを示し、層はSiに整列しており、完全に歪んだSiGe層を示しています(図9a、eを参照)。図9bは、垂直エッチング後のサンプルを示しています。図8bのRCの結果と同様に、SiGeピークがSi基板に向かってシフトしており、ひずみが緩和されていることを示しています。しかし、驚くべきことに、横方向のドライエッチングされたサンプル(図9c)は、Siピークとの位置合わせから外れる方向にある逆格子空間のシフトとともに、SiGeピークの明確なωの広がりを示しています。ただし、ウェットエッチングされたサンプル(図9d)は完全にひずみが整列しており、ドライエッチングされたサンプル(図9c)よりも層の強度が低くなっています。この場合、エッチングプロセスの性質が異なるため、生成された欠陥はこれらのサンプルで異なる原因を持っていると予想されます。サンプル2には2つのSiGe層が含まれています。 Si 0.93 Ge 0.07 ピークは、垂直方向と横方向の両方でエッチングした後も存続しますが、Si 0.78 Ge 0.22 垂直エッチング後に完全なひずみ緩和を示すと消えます(図8f–h)。サンプル2のプロセス安定性が低いのは、ミスフィット転位の形成を促進するPドーピングに起因する可能性があります。

PドープSi / Si 0.86 のHRRLM Ge 0.14 a に5nmのスペーサー層(サンプル-1)を備えた/ PドープSiML – d 、およびPドープSi 0.93 Ge 0.07 / Si 0.78 Ge 0.22 / PドープSi 0.93 Ge 0.07 e のML(サンプル2) – h 。 2つのマッピングには、両方とも4つのパネルがあります。成長すると、垂直エッチング後、HF(6%)/ H 2 の横方向ウェットエッチングが行われます。 O 2 (30%)/ CH 3 COOH(99.8%)20分、CF 4 の横方向ドライエッチング / O 2 /彼11.5秒

結論

この作業では、vGAAFETの初期構造としてこれらのMLをエッチングするとともに、PドープSi / SiGe / PドープSiMLのエピタキシーを調査しました。最初に、Si / SiGe / SiMLへのPの取り込みが研究されました。 Si / SiGeヘテロ構造の界面でのP偏析ピークを排除するために、エピタキシーとML構造のさまざまな戦略が提案されています。実験から、ドープされていないスペーサー層を挿入すると、Pピークが減少する可能性があります。過剰なP原子を除去するための水素パージはあまり役に立たず、安定したP-Pダイマーを完全に除去することはできませんでした。 SiH 4 に置き換える SiH 2 を使用 Cl 2 成長中にCl化学を導入するSi前駆体は、Clの活性表面反応により、分離したPピークを著しく減少させました。 Si 0.93 の影響 Ge 0.07 PドープSi後のスペーサー層も調べた。結果は、これらの層へのPの取り込みが桁違いに改善された一方で、SiGe界面のPピークが消失したことを示しました。この研究の第2部では、Si / SiGe / Si MLの垂直エッチングを実行してNWを形成し、その後、これらのNWでSiGeを選択的にウェットエッチングまたはドライエッチングしました。ウェットエッチングはドーパント濃度に敏感でした。一方、ドライエッチングはGe含有量に敏感でした。ドライエッチングは、均一なエッチングプロファイルとより高い選択性を備えたn型構造に適していました。 PドープSi / Si 0.86 の場合 Ge 0.14 / PドープSiMLの場合、選択性はドライエッチングで5.8、ウェットエッチングで4.2でした。 The selectivity of P-doped Si0.93 Ge0.07 /Si0.78 Ge0.22 /P-doped Si0.93 Ge0.07 MLs was 6.3 with dry etch and 2.5 with wet etch. The strain in SiGe was mostly preserved in Si/SiGe/Si after vertical and lateral etch; meanwhile, this strain in MLs with introduced Si0.93 Ge0.07 spacer layer had poor stability after etch process.

データと資料の可用性

The authors declare that the data supporting the findings of this study are available within the article.

略語

- vGAAFET:

-

Vertical gate-all-around field-effect transistors

- ML:

-

Multilayer

- CMOS:

-

Complementary metal oxide semiconductor

- MBE:

-

分子線エピタキシー

- RPCVD:

-

Reduced pressure chemical vapor deposition

- RTCVD:

-

Rapid thermal chemical vapor deposition

- S/D:

-

Source/drain

- HRTEM:

-

高分解能透過型電子顕微鏡

- HRXRD:

-

高解像度X線回折

- HRRLM:

-

High-resolution reciprocal lattice map

- SEM:

-

走査型電子顕微鏡

- SIMS:

-

Secondary ion mass spectroscopy

- RC:

-

Rocking curve

- FWHM:

-

Full-width-half-maximum

- HM:

-

Hardmask

ナノマテリアル

- CyrusOneのユーザーと顧客のアプリケーションパフォーマンスを向上させる

- 10nmチップ用のエアスペーサー

- 光検出用途のための容易な溶液技術による羽のようなZnO構造の直接成長

- スーパーキャパシター用途の電極としてのグラフェン/ WO3およびグラフェン/ CeOx構造の評価

- Fe3 +用の再開可能な蛍光プローブBHN-Fe3O4 @ SiO2ハイブリッドナノ構造とそのバイオイメージングへの応用

- 反射防止および超疎水性用途のための金属塩-ポリマーナノコンポジットフィルムの相分離によって形成された表面ナノ構造

- アプリケーションに適したロボット溶接プロセスと機器のタイプの選択

- 企業は2019年のビッグテックの変化と課題に備える

- 鋳造、鍛造、旋盤用の垂直旋盤

- 鋳造、鍛造、旋削用の垂直旋盤(2)

- 生産と効率のための VMC 機械