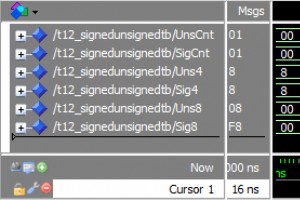

VHDL の符号付きおよび符号なしの型は、std_logic_vector 型と同様にビット ベクトルです。違いは、std_logic_vector はデータ バスの実装には優れていますが、算術演算の実行には役に立たないことです。 std_logic_vector 型に数値を追加しようとすると、ModelSim は次のコンパイル エラーを生成します:中置演算子 + の実行可能なエントリがありません。これは、ベクトルであるこのビットのコレクションを解釈する方法をコンパイラが認識していないためです。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 ベクトルを符号

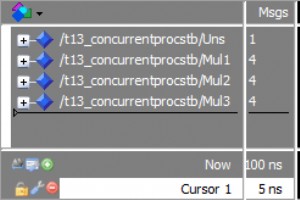

VHDL の並行ステートメントは、アーキテクチャ内のシグナル割り当てですが、通常のプロセス構造の外側にあります。同時実行ステートメントは、同時割り当てまたは同時プロセスとも呼ばれます。 コンカレント ステートメントを作成すると、実際には、明確に定義された特定の特性を持つプロセスが作成されます。並行ステートメントは常に、シグナル割り当て演算子の右側にあるすべてのシグナルがセンシティビティ リストにあるセンシティビティ リストを使用するプロセスと同等です。 これらの簡略表記プロセスは、1 つの信号を割り当てる単純なロジックを作成する場合に役立ちます。センシティビティ リストなどを含む完全なプロ

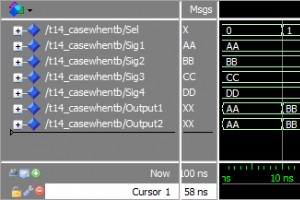

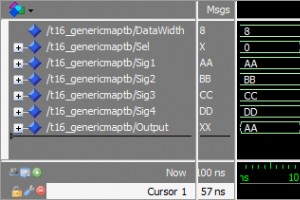

Case-When ステートメントにより、プログラムはシグナル、変数、または式の値に応じて、複数の異なるパスから 1 つを選択します。これは、複数の Elsif を持つ If-Then-Elsif-Else ステートメントのよりエレガントな代替手段です。 他のプログラミング言語にも同様の構造があり、switch などのキーワードを使用します。 、ケース 、または選択 .特に、Case-When ステートメントは、VHDL でマルチプレクサを実装するためによく使用されます。続きを読むか、ビデオを見て方法を確認してください! このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部

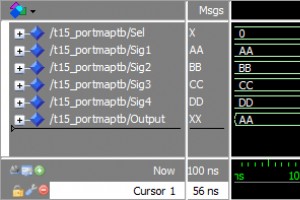

モジュールは、VHDL コードの自己完結型ユニットです。モジュールはエンティティを通じて外界と通信します . 港マップ モジュールのインスタンス化の一部であり、モジュールの入力と出力が接続されるローカル信号を宣言します。 このシリーズの以前のチュートリアルでは、すべてのコードをメインの VHDL ファイルに記述しましたが、通常はそうしません。シミュレーター用ではなく、FPGA または ASIC 設計で使用する目的でロジックを作成します。 シミュレータで実行するために作成された VHDL モジュールには、通常、入力信号も出力信号もありません。それは完全に自己完結型です。だからこそ、私たちのデ

モジュールを作成することは、コードを再利用する優れた方法ですが、多くの場合、設計全体でより小さなバリエーションを持つ同じモジュールが必要になります。これがジェネリックとジェネリック マップの目的です。これにより、モジュールの特定の部分をコンパイル時に構成可能にすることができます。 定数は、同じ値を何度も入力することを避けたい場合に使用されます。これらは、コンパイル時に信号ベクトルのビット幅を定義するために使用でき、一般的な定数にもマッピングできます。定数は、コード内の任意の場所で信号と変数の代わりに使用できますが、それらの値はコンパイル後に変更できません。 このブログ投稿は、基本的な VH

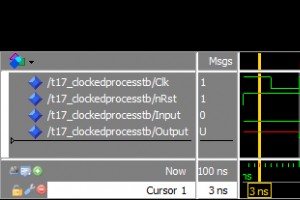

VHDL デザインの大部分は、クロック ロジックを使用しています。 、同期ロジックとも呼ばれます またはシーケンシャル ロジック .クロックされたプロセスは、他の入力信号が変化したときではなく、マスター クロック信号によってのみトリガーされます。 クロック ロジックの基本的なビルディング ブロックは、フリップフロップと呼ばれるコンポーネントです。 .これにはさまざまなバリエーションがあり、このチュートリアルでは、ネガティブ リセットを備えたポジティブ エッジ トリガー フリップフロップに焦点を当てます。 フリップフロップはサンプルアンドホールド回路です。つまり、クロック信号の立ち上が

基本的な VHDL チュートリアル シリーズのチュートリアル 12 ~ 17 を完了した後、この VHDL クイズで進捗状況をテストしてください! 署名された型について正しいステートメントはどれですか? できるunsigned 型よりも高い値を表す 左端のビットは 1 で、値は負でなければなりません オーバーフローは実行時エラー 正しい!違う! - この並行プロセスに相当するものはどれですか? 正しい!違う! - このコードを実行した後の Output の値は? 0000 0001 UUUU

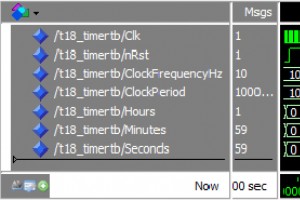

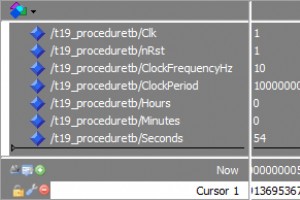

以前のチュートリアルでは、wait for を使用しました シミュレーションで時間を遅らせるステートメント。しかし、生産モジュールはどうですか? wait for ステートメントはそのために使用できません。回路内の電子に特定の時間一時停止するように指示することはできないため、これはシミュレーションでのみ機能します。では、設計モジュールで時間を追跡するにはどうすればよいでしょうか? 答えは単純にクロック サイクルをカウントすることです。すべてのデジタル設計は、既知の固定周波数で発振するクロック信号にアクセスできます。したがって、クロック周波数が 100 MHz であることがわかっている場合、1

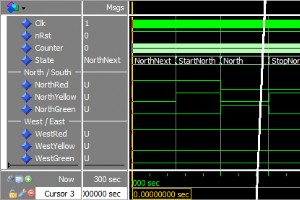

プロシージャは、コードの繰り返しを避けるのに役立つ VHDL のサブプログラムの一種です。場合によっては、設計全体のいくつかの場所で同じ操作を実行する必要が生じることがあります。モジュールの作成はマイナーな操作にはやり過ぎかもしれませんが、多くの場合、手順が必要です。 プロシージャは、任意の宣言領域内で宣言できます。プロシージャのスコープは、宣言されている場所、アーキテクチャ、パッケージ、またはプロセスに限定されます。プロシージャを呼び出すたびに、プロシージャのコードが呼び出された場所に挿入されたように動作します。 プロシージャは関数のように値を返しませんが、out を宣言することで値を返

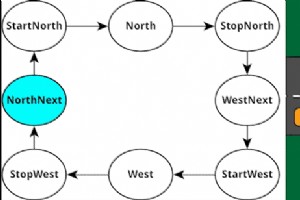

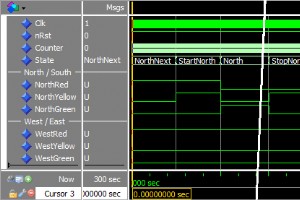

有限状態マシン (FSM) は、出力が入力の現在の状態だけでなく、過去の入力値と出力値にも依存するメカニズムです。 VHDL である種の時間依存アルゴリズムを作成する必要がある場合、または FPGA にコンピューター プログラムを実装する際の問題に直面した場合、通常は FSM を使用して解決できます。 VHDL のステート マシンは、ステート信号の値によって出力が制御されるクロック プロセスです。状態信号は、前の反復で何が起こったかの内部メモリとして機能します。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 この交差点の信号機の状態を考えてみましょう:

関数は、頻繁に使用されるアルゴリズムを実装するために使用できる VHDL のサブプログラムです。関数は 0 個以上の入力値を取り、常に値を返します。戻り値に加えて、プロシージャと関数を区別するのは、Wait ステートメントを含めることができないことです。これは、関数が消費するシミュレーション時間が常にゼロであることを意味します。 他のプログラミング言語の関数やメソッドに精通している場合、VHDL 関数は簡単に理解できるはずです。 VHDL では、戻り値を省略したり void を返したりすることはできません。関数は常に何かを返す必要があり、戻り値を何かに割り当てる必要があります。 このブログ

不純な関数は、そのスコープ内の任意のシグナルを読み書きできます。また、パラメーター リストにないシグナルも読み書きできます。関数には副作用があると言います . 副作用とは、関数が同じパラメーターで呼び出されるたびに同じ値を返すことが保証されていないことを意味します。関数がパラメーター リストにないシグナルを読み取ることができる場合、戻り値はこれらのシャドウ パラメーターにも依存する可能性があります。また、関数は戻り値から割り当てられていない外部シグナルを変更している可能性があります。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 通常の純粋な関数を宣言でき

プロシージャから外部信号を駆動することができます。シグナルがプロシージャのスコープ内にある限り、パラメーター リストに記載されていなくても、読み取りまたは書き込みのためにアクセスできます。 アーキテクチャの宣言領域で宣言されたプロシージャは、外部信号を駆動できません。これは、コンパイル時にスコープにシグナルがないためです。一方、プロセス内で宣言されたプロシージャは、プロセスが認識できるすべてのシグナルにアクセスできます。 このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。 このような手順は、同じ操作が複数回発生するプロセスでアルゴリズムを整理するために使用できま

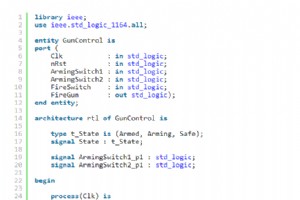

基本的な VHDL チュートリアル シリーズのパート 4 を完了したら、この VHDL クイズで進捗状況をテストしてください! VHDL でリアルタイムを測定するにはどうすればよいですか? を使用して「1 ns 待つ」ステートメント カウントによるクロック周期 悪用する伝搬遅延 正しい!違う! - プロシージャに Wait ステートメントを含めることはできません 手順パラメーター常に入力です 使用時プロシージャでは、return キーワードは値なしである必要があります 正しい!違う! - この火器管制システムの根本的な欠陥を説明しているのはどれで

連結リストは動的データ構造です。リンクされたリストは、要素の総数が事前にわからない場合に使用できます。含まれるアイテムの数に応じて、メモリ内で拡大および縮小します。 リンク リストは、オブジェクト指向プログラミング言語のクラスを使用して実装するのが最も便利です。 VHDL には、実装の複雑さをユーザーから抽象化するために使用できるオブジェクト指向の機能がいくつかあります。 この記事では、VHDL でリンク リストを実装するために、アクセス タイプ、レコード、および保護されたタイプを使用します。すべてのリンク リスト コードを記述する新しい VHDL パッケージを作成します。 パッケージ

セルフチェック テストベンチは、オペレータが出力を手動で検査することに依存せずに、被試験デバイス (DUT) の正確性を検証する VHDL プログラムです。セルフチェック テストベンチは完全に単独で実行され、最後に「OK」または「失敗」メッセージを出力します。 すべての VHDL モジュールには、関連付けられたセルフチェック テストベンチが必要です。すべてのモジュールが意図した動作をしていることをいつでも確認できることが重要です。たとえば、DUT、サブモジュール、またはインターフェイス モジュールに変更を加える場合です。壊れる可能性があることは誰もが知っています。これらの問題を検出するための

対話型テストベンチは、テストベンチの実行中にオペレータが被試験デバイス (DUT) への入力を提供するシミュレータ セットアップです。ほとんどの場合、これはシミュレータ コンソールにコマンドを入力して DUT に刺激を与えることを意味します。 常にセルフチェック テストベンチを作成する必要がありますが、対話型テストベンチは優れた補足になります。セルフチェック テストベンチのコードを変更するよりも、インタラクティブなテストベンチを使用してアドホック テストを実行する方が簡単です。 多くの場合、テストベンチで試してみたい問題がラボで見つかります。インタラクティブなテストベンチを使用すると、観察

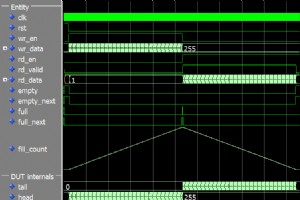

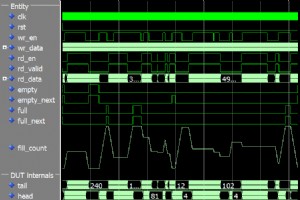

循環バッファーは、シーケンシャル プログラミング言語でキューを作成するための一般的な構造ですが、ハードウェアに実装することもできます。この記事では、ブロック RAM に FIFO を実装するために、VHDL でリング バッファーを作成します。 FIFO を実装する際には、多くの設計上の決定を行う必要があります。どのようなインターフェースが必要ですか?リソースによって制限されていますか?オーバーリードとオーバーライトに対する回復力が必要ですか?遅延は許容範囲ですか?これらは、FIFO の作成を依頼されたときに頭に浮かんだ質問の一部です。 無料の FIFO インプリメンテーションがオンラインで

制約付きランダム検証は、テスト対象デバイス (DUT) の疑似ランダム トランザクションの生成に依存するテストベンチ戦略です。目標は、DUT とのランダムな相互作用を通じて、多数の定義済みイベントの機能範囲に到達することです。 Open Source VHDL Verification Methodology (OSVVM) は、制約付きランダム テストベンチを作成するための便利なパッケージを多数含む無料の VHDL ライブラリです。この記事で使用する RandomPkg と CoveragePck に特に関心があります。このライブラリの機能の詳細については、OSVVM GitHub ページ

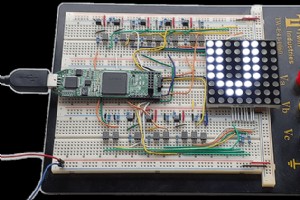

過去 6 か月間取り組んできた VHDL と FPGA のコースが完成し始めたことを発表できることを嬉しく思います。このコースは現在ベータ版で、今年の秋に初めて開始する予定です。 FPGA コースの対象者は? FPGA コースは、他のプログラミング言語の知識はあるが、VHDL と FPGA は初めての開発者を対象としています。このコースでは、初級または中級レベルから、高度な VHDL コーディング構造を理解して使用できるようになります。 このコースは、FPGA 開発を任されたプロのソフトウェア エンジニアに最適です。ハードウェア設計に興味があり、FPGA 開発への転職を考えている学生やフリ

VHDL