サブ10nmノード用の新しいサンドイッチオーミック接触を備えた高性能2次元InSe電界効果トランジスタ:理論的研究

要約

2次元(2D)InSeベースの電界効果トランジスタ(FET)は、実験レポートで顕著なキャリア移動度と高いオンオフ比を示しています。理論的調査はまた、弾道限界のサブ10nmノードで高性能を十分に維持できることを示しています。しかし、実験経験と理論計算の両方で、高品質のオームを達成することが高性能2DFETの主な制限要因になっていることが指摘されています。この作業では、InSe FET用のインジウムとの新しいサンドイッチオーミック接触を提案し、abinitio法に基づいて材料とデバイスの観点からその性能を包括的に評価しました。材料特性は、トンネル構造、ショットキー障壁、効果的なドーピングを含むオーミック接触の基本的な問題のすべてが、サンドイッチ構造を導入することによって十分に懸念され、優れた接触抵抗が達成されたことを示しています。デバイスの性能レベルでは、ゲート長が7、5、および3nmのデバイスが調査されました。挟まれた接触デバイスのすべてのメトリックは、国際半導体技術ロードマップ(ITRS)の要件をはるかに超えており、従来の構造と比較して明らかな推進力を示しています。ゲート長が7、5、および3 nmのデバイスでは、それぞれ69.4%、50%、および49%の電流の最大ブーストが達成されます。一方、20.4%、16.7%、および18.9%の固有遅延の最大削減が達成されます。さらに、他の2D FETに対するエネルギー遅延製品(EDP)のベンチマークが提示されます。オーミック接触が挟まれたすべてのInSeFETはMoS 2 を上回ります FETとITRS2024の要件。最良の結果は、理想的なBP FETの上限に近づき、次世代の相補型金属酸化膜半導体(CMOS)テクノロジーにおけるInSeFETのサンドイッチ構造の優位性を示しています。

はじめに

二次元(2D)半導体は、次世代の相補型金属酸化膜半導体(CMOS)技術への魅力的なアプリケーションにより、電子デバイスに大きな関心を集めています[1、2]。それらの超薄型の厚さと優れた誘電特性は、よく知られている短チャネル効果を抑制するための優れた静電ゲート制御を提供できます[3]。さらに、2D材料の層は通常、ぶら下がり結合のない滑らかな表面を持っているため、従来の半導体と比較して、2D材料の優れたキャリア移動度を極薄ボディシステムで十分に維持できます[4]。ギャップレスグラフェンを除いて、遷移金属ジカルコゲナイド(TMD)、黒リン(BP)、インジウムセレン化物(InSe)などの合成2D半導体のほとんどは、ゼロ以外のバンドギャップを持ち、電界効果トランジスタ(FET)に適していることが実証されています。 )。 TMDベースのFETは、10 8 もの高いオンオフ比を示しています。 短チャネルデバイスのリーク電流が低く、有効質量が大きいというメリットがあります[5]。 BPベースのFETは、〜1000 cm 2 の高い移動度により、優れた電流およびスイッチング特性を示します[6]。 / Vsと異方性輸送特性[7]。最近、InSeは〜2000cm 2 の優れた移動度を示すことが実証されました 室温で/ V s [8、9]、InSeに基づくFETは、10 8 の高いオンオフ比を示しました。 [10]。第一原理計算では、InSe FETが弾道限界でサブ10 nmまで十分にスケールダウンできることも確認されました[11、12]。ただし、接触抵抗を無視し、大量のドーピングを行うという仮説があるため、実際のアプリケーションでは理論上の限界に近づくことは依然として困難です。実際、信頼性の高いドーピング方法と高品質のオーミック接触への道がまだ不足しているため、InSeを含む2D材料に基づくFETは通常ショットキーバリア(SB)FETです[13、14、15、16]。活性領域のSBは大きな接触抵抗をもたらし、ドーピングレベルが低いと電流密度がさらに低下します。十分にドープされた活性領域で低い接触抵抗を達成することは、高性能を達成するための2D材料ベースのFET(2D FET)の主な制限要因になっています[17、18、19]。

上記の問題を目指して、InSeFET用の新しいサンドイッチオーミックコンタクトを提案しました。インジウムが電極金属として選択されたのは、最近の実験的および理論的研究により、インジウムが良好な性能を達成するためのInSeFETの有望な候補である可能性があることが示唆されているためです[20、21、22]。国際半導体技術ロードマップ(ITRS)[23]の枠組みに従って、ゲート長が7、5、および3nmのデバイスのオーミック接触の品質と性能を理論的に評価しました。 ITRSは国際半導体技術ロードマップ(IRDS)[24]に置き換えられましたが、ITRS2013はトランジスタの明確なスケーリング傾向を示しており、最近の研究でも採用されています[25、26]。この原稿は次のように構成されています。最初に、サンドイッチ型および従来型(上部)の接点の電気的特性を調査します。次に、オン状態の電流や固有の遅延などのデバイスパフォーマンスメトリックが評価され、ITRSの要件と比較されます。最後に、電力遅延積と固有遅延のベンチマークを示して、他の2D材料ベースのデバイスと比較します。

メソッド

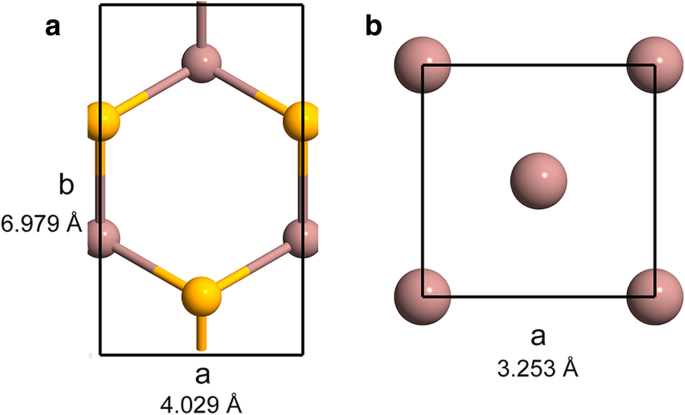

すべての原子構造はVASPによって最適化されました[27]。すべての計算で335eVのエネルギーカットが採用されました。 InSeのユニットセルは、SCANのMetaGGAのフレームワークの下で0.01eV /Åの応力基準で緩和されました[28]。金属インジウムの格子定数は、化学物理学ハンドブック[29]から入手しました。図1に示すように、InSeの格子定数は4.029Åであり、実験報告[30、31]と非常によく一致しています。

InSeのユニットセルの上面図( a )およびインジウム( b )、それぞれ

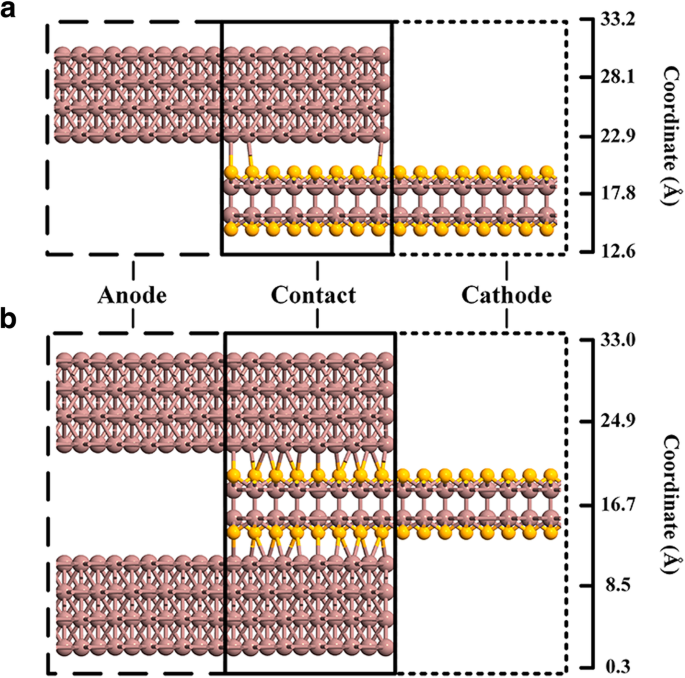

InSe上のインジウムの初期構造は、それぞれ4×1×1および5×2×1のInSeおよびインジウム(001)表面のユニットセルで構築されました。平均絶対ひずみは1.32%であり、これは材料の固有の特性を維持するのに十分です。図2a、bに示すように、サンドイッチ構造はインジウム/ InSe /インジウム層で構築されており、底面と上面のインジウムはInSeの中心と鏡面対称になっています。両方のハイブリッド構造は、各原子にかかる力の基準が0.02eV /Å未満のoptb88のファンデルワールス(vdW)関数で緩和されました[32、33]。最終的な接触面積は16.19Å×6.41Åです。次に、オーミック接触の抵抗を、図2a、bに示すように2プローブデバイスで評価しました。半導体の非接触領域からの不要な抵抗を取り除くために、カソードのInSeは1×10 14 で高濃度にドープされました。 e / cm 2 トップコンタクトとサンドイッチコンタクトの両方に。

接触抵抗の評価に使用される接触および関連する2プローブデバイスの原子構造。 a 、 b それぞれ上部接点とサンドイッチ接点用です。 座標は、面外方向の原子の位置を示します

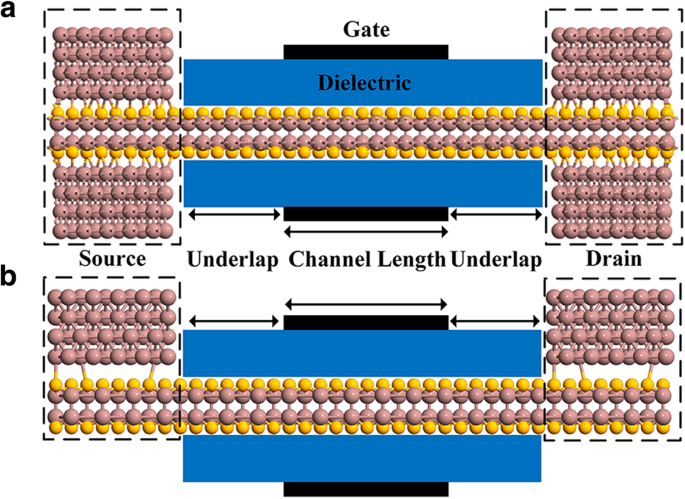

デバイス性能の評価については、サンドイッチ接点とトップオーミック接点を備えたInSe FETの形状をそれぞれ図3a、bに示します。すべてのデバイスとノードの名前は、それぞれITRSとIRDSの要件に従います。デバイスパラメータを表1に示します。バンド内トンネリングを抑制するために、ゲート長3nmで1nmアンダーラップ(UL)を適用しました。オーミック接触モデリングとは対照的に、デバイスのどの部品も意図的にドープされていません。デバイスは、輸送方向に沿ってソース、ドレイン、およびチャネルをマージすることによって構築されました。チャネルとアクティブ領域との2つのインターフェイスは、固定のソースとドレインでさらに緩和されました。すべてのシミュレーションは、非平衡グリーン関数(NEGF)理論に基づいており、完全に自己無撞着な計算[34,35,36]を使用してQuantumATKによって実行されました。これは、通常、サブ10nmノードのトランジスタの設計と調査に使用されました[17 、37、38、39]。二重ゼータ分極基底関数系は、90リュードベリのメカカットオフで採用されました。 Monkhorstパックのkポイントメッシュは、8 /Å -1 の密度でサンプリングされました。 ×11 /Å -1 ×180 /Å -1 。効率を上げるために、並列共役勾配ソルバーがポアソンソルバーとして選択されています。次に、Landauer-Büttikerの式[40]を解くことにより、すべてのデバイスの電流を取得できます。

$$ I \ left({V} _ {\ mathrm {Bias}} \ right)=\ frac {2e} {h} \ int T \ left(E、{V} _L、{V} _R \ right)\ left [{f} _ {\ mathrm {R}} \ left(E、{V} _R \ right)-{f} _L \ left(E、{V} _L \ right)\ right] dE $$ <図>

サンドイッチされたInSeFETの形状( a )とトップ( b )連絡先

<図>ここで、 V バイアス はバイアスであり、次の方法で実現できます: V バイアス = V R ‐ V L 、 T ( E 、 V L 、 V R )はキャリアの透過係数 f R ( E 、 V R )および f L ( E 、 V L )は、それぞれカソード(ドレイン)とアノード(ソース)のフェルミディラック分布関数です。

結果と考察

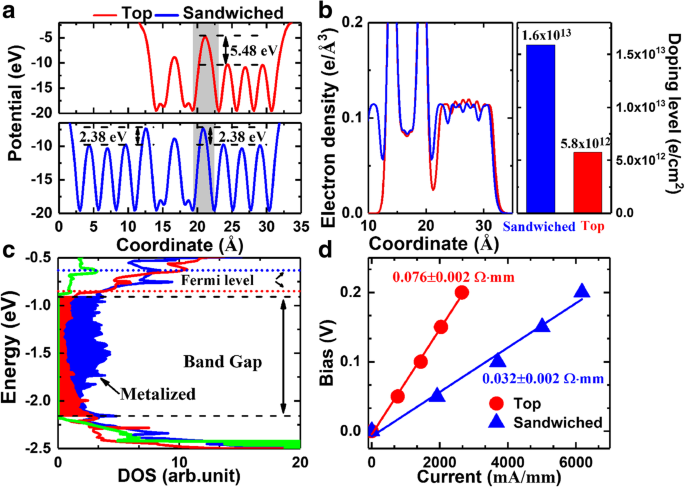

一般に、2D材料のオーミック接触品質に関連する3つの重要な要素があります。つまり、vdWギャップ、電極と半導体間の軌道の重なり、およびSBの高さに由来するトンネル障壁と距離です。まず、トンネル障壁と距離を図4aに示す実効ポテンシャルで表した。トップコンタクトと比較して、サンドイッチコンタクトの導入は、ボトムサイドに追加の輸送経路を提供するだけでなく、トンネル障壁を5.48から2.38 eVに減少させ、56.6%の減少をもたらします。一方、界面距離も0.66Åとわずかに低くなり、トンネル障壁の幅も狭くなっていることを示しています。第二に、軌道の重なりは、図4bのバランス電荷分布から評価できます。挟まれた接触は、上部の接触と比較して、界面領域でより多くの価電子を持っていることがわかります。これは、インジウムとInSeの間の軌道の重なりが強いことを示しています。この機能は、InSeにドーピング効果を導入するのにも役立ち、マリケン電荷分布解析を使用して過剰電子数を計算できます。サンドイッチ構造とトップコンタクト構造のInSeの電子の総数をそれぞれ抽出しました。次に、孤立したInSeの正味電荷は常にゼロである必要があるため、電子数を接触領域の面積で割ることによってドーピングレベルを取得できます。図4bの右側のパネルに示されているように、サンドイッチ接点は1.6×10 13 の非常に高いドーピングレベルをもたらします。 e / cm 2 、これはトップコンタクトの約2.8倍です。このような高レベルは、通常、金属酸化物半導体FETよりもはるかに重いドーピングレベルを主張する2DトンネリングFETのシミュレーションの仮説に近づいています。第三に、元の状態、サンドイッチ構造、および上部接触構造におけるInSeの状態密度(DOS)を図4cに示します。界面領域でのインジウムとInSeの軌道の重なりは、InSeのバンドギャップを金属化し、1つを挟むとより高いレベルになります。この機能は、バンドギャップの金属化状態が追加のトンネルチャネルを提供するため、界面領域のvdWトンネル障壁を介したキャリア注入を大幅に強化します。さらに、フェルミ準位は伝導帯の最小値より上に固定されているため、上部接点とサンドイッチ接点でそれぞれ約0.07と0.27eVのエネルギー縮退が発生します。したがって、インジウムとInSeの間のSBは完全に排除されます。第四に、オーミック接触抵抗は、2プローブデバイスから得られたバイアス電流曲線に基づいて計算され、すべての結果が図4dに示されています。線形進化により、両方の接触がオームであることがわかります。理論レベルでは、つまり、表面粗さ、界面不純物などを無視すると、サンドイッチ構造は0.032±0.002Ωmmの非常に低い接触値になり、上部接触の抵抗の半分以上が減少します。上記の議論に基づいて、接触領域が2倍になると、常にオーミック接触が2倍以上改善されることに注意してください。インジウムとのトップコンタクトは最近実験的にInSeベースのデバイスの性能を高めるのに効果的であることが確認されたため[21、22]、サンドイッチ構造はInSeFETの魅力的なオーミックコンタクトソリューションになり得ます。

a 輸送方向に垂直な実効ポテンシャル。座標は原子の位置に対応し、図1で定義されています。暗い領域はvdWギャップに対応します。 b 輸送方向に垂直な平面平均電子分布。右のパネルはドーピングレベルです。座標は原子の位置に対応し、図1で定義されています。 c InSeのDOS。緑は手付かずのInSeに対応します。 d 2つのプローブデバイスの電流依存バイアス。赤と青はすべて、それぞれ上部とサンドイッチの接点に対応しています

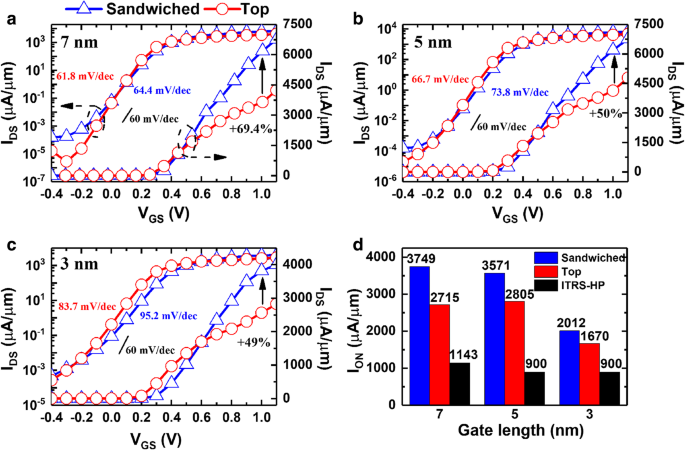

次に、デバイスの性能を評価し、2019、2021、および2024ノードでのInSe FETの伝達特性を図5に示しました。すべてのノードのサブスレッショルドスイング(SS)が100 mV / dec未満であることがわかります。 、および2019ノードのSSは、トップおよびサンドイッチ接触デバイスでそれぞれ61.8および64.4 mV / decのほぼ理想的なスイッチング特性を示し、InSeFETの優れた静電制御を示しています。さらに、挟まれた接触デバイスは、I DS の明らかな改善につながります 2019、2021、および2024ノードでそれぞれ最大69.4%、50%、および49%の増加が達成された上位のものと比較して。さらに、I ON ITRSの高性能(HP)の要件に従って抽出されました。図5dに示すように、I ON すべてのシステムの中で、HPの要件をはるかに上回っています。トップコンタクトデバイスと比較して、サンドイッチシステムは、2019、2021、および2024ノードでそれぞれ38.2%、27.3%、および20.5%のプロモーションを示しています。

ノードでのInSeFETの伝達特性。 a 2019年、 b 2021、および c それぞれ2024ノード。 d I ON の比較 ITRSのHP要件に従う

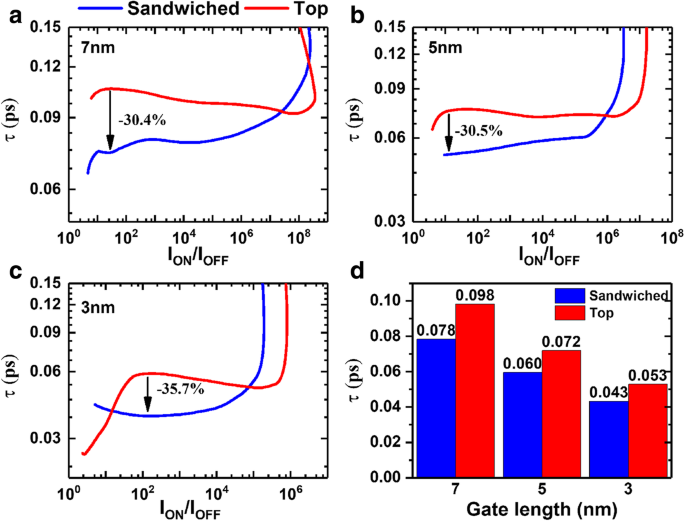

FETのもう1つの重要なメトリックは、論理回路のスイッチング速度の上限を示す固有遅延(τ)です。 τはτによって得られました =(Q ON − q オフ )/ I ON 、ここでQ ON およびQ OFF それぞれオン状態とオフ状態での料金です。オンとオフの状態は| V DS で制限されます | =0.68、0.64、および0.64 V(2019、2021、および2024ノードの場合)。オンオフ比の関数としての固有の遅延を図6に示します。低いゲート電圧でのトンネリングに由来する大きな遅延での非単調な変化にもかかわらず[41]、すべての遅延は0.15 ps未満であり、 0.44〜0.46psのITRS要件。さらに、挟まれた接触デバイスは、I ON の領域で30%以上の削減をもたらします。 / I オフ ≤10 7 、10 6 、10 5 それぞれ2019、2021、および2024ノードの場合。図6dに示されているHP要件に基づいて、挟まれた接触デバイスは、2019、2021、および2024ノードでそれぞれ20.4%、16.7%、および18.9%のスイッチング速度を促進できます。

ノードでのオンオフ比の関数としての固有の遅延。 a 2019年、 b 2021、および c それぞれ2024ノード。 d ITRSのHP要件に続く固有の遅延の比較

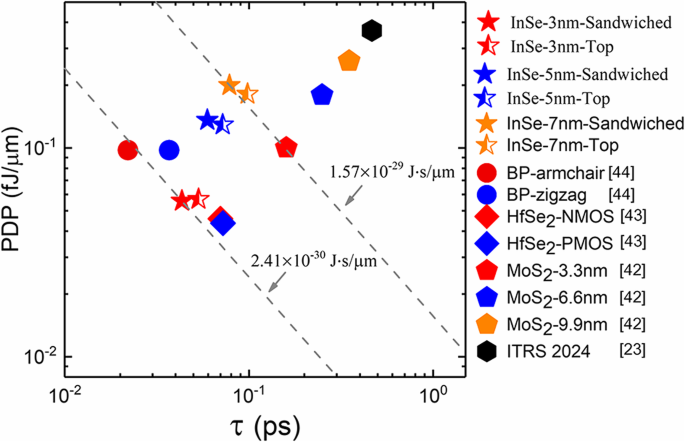

デバイスのパフォーマンスをより直感的に評価するために、電力遅延積(PDP)と固有の遅延が抽出されます。 PDPは、単一のスイッチングイベントでの消費電力に対応し、PDP =(Q ON − q オフ )V DS ITRSのHP要件から派生したすべてのパラメータを使用します。結果と他の2DFETとの比較を図7に示します。最初に、すべての2D FETは、実験レポートでトランジスタとして事前に検証されているというルールに基づいて選択されました。これは、CMOSテクノロジにとってさらに一歩進んだものです。次に、InSeとMoS 2 を除く [42]、他のすべてのデバイスは、アクティブ領域に高濃度にドーピングし、オーミック接触抵抗を無視してシミュレートされた[43、44]。したがって、結果は性能の上限に対応します。ご覧のとおり、すべてのエネルギー遅延製品(EDP)はITRS 2024要件を下回っており、2DFETの魅力的な未来を示しています。 EDPの最大値はMoS 2 に属します 9.9 nmのFETであり、最良のものはBPFETからのものです。 InSe FETに関しては、サンドイッチ型接触デバイスは、すべてのノードで常にトップコンタクト型デバイスよりも優れた性能を発揮します。サンドイッチ接触デバイスの最高EDPは、ゲート長7 nm(2019ノード)であり、すべてのMoS 2 を超えています。 FET。最も低いものはゲート長3nm(2024ノード)であり、優れた輸送特性でよく知られているアームチェア方向のBPFETの上限にさえ近づいています。したがって、InSe FETのEDPは、挟まれた接触デバイスが2DFET間で十分な競争力を示すことを意味します。

電力遅延積とInSeおよびその他の2DFETで構成される固有遅延。灰色の破線のガイドラインは特定のEDPに対応しています

結論

この作業では、インジウムとの新しいサンドイッチオーミック接触がInSeFET用に提案されました。挟まれたオーミック接触は、接触領域を2倍にするだけでなく、接触品質を2倍以上向上させ、優れた接触抵抗をもたらします。ゲート長7、5、および3 nmのデバイス性能レベルでは、オーミック接触が挟まれたInSe FETは、従来のトップコンタクトデバイスと比較して、普遍的な性能向上を示します。 ITRSからのHPの要件の下で、オン状態の電流と固有の遅延は、それぞれ38.2〜20.5%と20.4〜16.7%に改善されています。他の2DFETに対するEDPのベンチマークでも、オーミック接触が挟まれたInSeFETが他の2DFETよりも優れていることがわかります。私たちの研究は、高性能InSeFETへの新しいルートを提供します。

データと資料の可用性

現在の研究中に使用および/または分析されたデータセットは、合理的な要求に応じて対応する著者から入手できます。

略語

- 2D:

-

二次元

- CMOS:

-

相補型金属酸化膜半導体

- TMD:

-

遷移金属ジカルコゲナイド

- BP:

-

黒リン

- InSe:

-

セレン化インジウム

- FET:

-

電界効果トランジスタ

- SB:

-

ショットキーバリア

- 2D FET:

-

2D材料ベースのFET

- ITRS:

-

半導体の国際技術ロードマップ

- vdW:

-

ファンデルワールス

- UL:

-

アンダーラップ

- NEGF:

-

非平衡グリーン関数

- DOS:

-

状態密度

- SS:

-

サブスレッショルドスイング

- HP:

-

高性能

- τ:

-

固有の遅延

- PDP:

-

電力遅延積

- EDP:

-

エネルギー遅延製品

ナノマテリアル

- 10nmチップ用のエアスペーサー

- Nexamが高性能PETフォーム用の特性を向上させるNexamiteをDiabに供給

- スーパーキャパシター用の高性能電極としての廃綿手袋に由来する階層的ナノ構造を有する活性炭繊維

- 低抵抗Auオーミックコンタクトを備えた多層SnSeナノフレーク電界効果トランジスタ

- 新規ナノ粒子増強ワーム状ミセルシステムの研究

- 粗い表面の通常の荷重による接触面積の変化:原子スケールから巨視的スケールまで

- 薄膜トランジスタ用の酸化インジウムナノフィルムの原子層堆積

- 高性能スーパーキャパシタ用の2次元VO2メソポーラスマイクロアレイ

- HfO2欠陥制御層を備えた単層カーボンナノチューブが支配的なミクロンワイドストライプパターンベースの強誘電体電界効果トランジスタ

- 光起電デバイス用の反射防止および超疎水性特性を備えた新しいナノコーンクラスター微細構造

- アトラジンの高感度検出のための新しい磁気弾性ナノバイオセンサー