読み取り専用メモリ(ROM)は、「ラッチ」メカニズムが1回限りの(または制限された)操作用に作成されていることを除いて、静的または動的RAM回路と設計が似ています。最も単純なタイプのROMは、2つのバイナリ状態を表すために選択的にブローまたはそのままにしておくことができる小さな「ヒューズ」を使用するものです。明らかに、小さなヒューズの1つが飛んだら、それを再び完全にすることはできないので、そのようなROM回路の書き込みは1回だけです。 これらの回路は一度だけ書き込む(プログラムする)ことができるため、PROM(プログラム可能な読み取り専用メモリ)と呼ばれることもあります。ただし、すべての書き

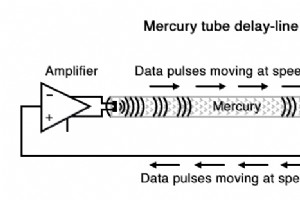

おそらく最も独創的なテクニックは、ディレイラインのテクニックでした。 。遅延線は、パルスまたは波動信号の伝播を遅らせるあらゆる種類のデバイスです。峡谷や洞窟で音が前後にエコーするのを聞いたことがある場合は、音声の遅延線が発生しています。ノイズ波は音速で伝わり、壁で跳ね返り、進行方向が逆になります。 信号が定期的に強化されていない場合、遅延線は非常に一時的にデータを「保存」しますが、データを保存するという事実自体が、メモリ技術に悪用される現象です。 初期のコンピューター遅延線は、音波が管の長さに沿って伝わる物理的媒体として使用された液体水銀で満たされた長い管を使用していました。電気/音響トラ

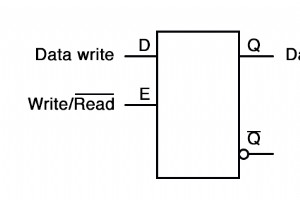

これで、特定の種類のデジタルストレージデバイスの調査に進むことができます。まず、可動部品を必要としない技術のいくつかを探求したいと思います。これらは、おそらく最新のテクノロジーではありませんが、将来的には可動部品テクノロジーに取って代わる可能性があります。 非常に単純なタイプの電子メモリは、双安定マルチバイブレータです。 1ビットのデータを保存できるため、揮発性(メモリを維持するために電力が必要)であり、非常に高速です。 Dラッチは、メモリ使用量の双安定マルチバイブレータの最も単純な実装であり、D入力はデータの「書き込み」入力として機能し、Q出力は「読み取り」出力として機能し、イネーブル入力

ある種の回路やデバイスに情報を保存する場合、情報を保存して取得する方法だけでなく、場所を正確に特定する方法も必要です。 それがデバイスにあります。 すべてではないにしても、ほとんどのメモリデバイスは、一連のメールボックス、ファイルキャビネット内のフォルダ、または情報をさまざまな場所に配置できるその他のメタファーと考えることができます。 メモリデバイスに保存されている実際の情報を参照する場合、通常はデータと呼びます。 。ストレージデバイス内のこのデータの場所は、通常、アドレスと呼ばれます。 、郵便サービスを彷彿とさせる方法で。 一部のタイプのメモリデバイスでは、特定のデータが格納されている

多くの教科書がデジタルメモリ技術の優れた入門書を提供していますが、私はこの章を、過去と現在の両方の技術をある程度詳細に提示するという点でユニークにするつもりです。これらのメモリ設計の多くは時代遅れですが、それらの基本原則は依然として非常に興味深く教育的であり、将来のメモリ技術に再適用される可能性さえあります。 デジタルメモリの基本的な目標は、バイナリデータ(1と0のシーケンス)を格納してアクセスする手段を提供することです。情報のデジタルストレージは、情報のデジタル通信がアナログ通信よりも優れているのとほぼ同じように、アナログ技術よりも優れています。 これは、デジタルデータストレージがアナロ

実際のプロセスの監視と制御が頻繁に迅速かつ設定された時間に行われる必要がある産業用制御ネットワークの主な考慮事項は、あるノードから別のノードへの最大通信時間を保証することです。 デジタルネットワークを使用して原子炉冷却材バルブの位置を制御している場合は、バルブのネットワークノードが適切なタイミングで制御コンピュータから適切な位置決め信号を受信することを保証できる必要があります。そうしないと、非常に悪いことが起こる可能性があります! ネットワークがデータの「スループット」を保証する機能は、決定論と呼ばれます。決定論的ネットワークには、ノードからノードへのデータ転送の最大時間遅延が保証されてい

物理ネットワークの問題(信号の種類と電圧レベル、コネクタのピン配置、ケーブル接続、トポロジなど)は別として、ネットワーク内の複数のノード間で通信を調停する標準化された方法が必要です。 2ノードのポイントツーポイントシステムとして。ノードがネットワーク上で「通信」するとき、ノードはネットワーク配線上で信号を生成します。これは、高低のDC電圧レベル、ある種の変調されたAC搬送波信号、またはファイバー内の光のパルスですらあります。 「リッスン」するノードは、(送信ノードからの)ネットワーク上で適用された信号を測定し、それを受動的に監視しているだけです。ただし、2つ以上のノードが同時に「通信」すると、

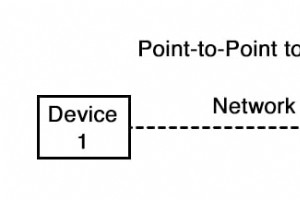

ポイントツーポイント 2つのデジタルデバイスをネットワークに接続すると、「ポイントツーポイント」と呼ばれる一種のネットワークができます。 ネットワーク配線は、2つのデバイス間の単一の線として表されます。実際には、ツイストペア線、同軸ケーブル、光ファイバー、さらには7芯のBogusBusの場合もあります。現在は、技術的にはトポロジと呼ばれるネットワークの「形状」に焦点を当てているだけです。 このネットワーク上にさらに多くのデバイス(ノードと呼ばれることもあります)を含めると、ネットワーク構成のいくつかのオプションから選択できます。 バストポロジ ネットワークのすべてのノ

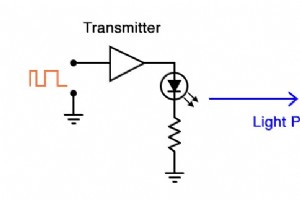

電圧信号を介して(バイナリ)デジタル情報を送信する代わりの最新の方法は、光(光)信号を使用することです。デジタル回路からの電気信号(高/低電圧)は、LEDまたは固体レーザーを使用して個別の光信号(光または光なし)に変換できます。同様に、光信号は、ゲート回路の入力に導入するためのフォトダイオードまたはフォトトランジスタを使用して、電気的な形式に戻すことができます。 光学形式でのデジタル情報の送信は、離れた場所にある光検出器にレーザーを向けるだけで、屋外で行うことができますが、温度逆転層、ほこり、雨、霧、およびその他の障害物の形でのビームとの干渉が存在する可能性があります重要なエン

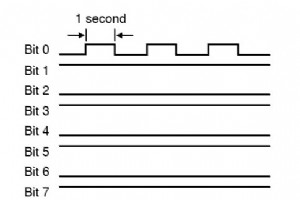

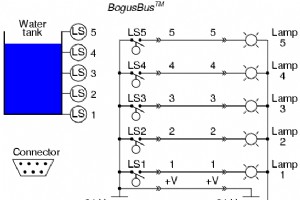

BogusBusを使用すると、信号は非常にシンプルでわかりやすくなりました。各信号線(1〜5)は、1ビットのデジタルデータを伝送しました。0ボルトは「オフ」を表し、24ボルトDCは「オン」を表します。すべてのビットが同時に宛先に到着したため、BogusBusを 並列と呼びます。 ネットワークテクノロジー 。 バイナリエンコーディング(送信機側)とデコード(受信機側)を追加してBogusBusのパフォーマンスを向上させ、より少ないワイヤでより多くの解像度のステップを利用できるようにした場合でも、並列ネットワークになります。 ただし、送信機側にパラレルからシリアルへのコンバーターを追加し、受信

バスとネットワークは、相互接続された個々のデバイス間で通信が行われるように設計されています。ノード間の情報またはデータの流れは、さまざまな形をとることができます。 単方向通信では、すべてのデータフローは一方向です。指定された送信機から指定された受信機へ。 BogusBusは、送信機がリモートの監視場所に情報を送信したが、水タンクに情報が返送されない単方向通信の例です。 情報を一方向に送信するだけであれば、シンプレックスで十分です。ただし、ほとんどのアプリケーションはより多くを要求します: 二重通信 二重通信では、情報の流れはデバイスごとに双方向になります。

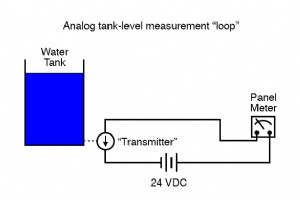

タンクと監視場所の間の配線は、バスまたはネットワークと呼ばれます。 。これらの2つの用語の違いは、技術的な用語よりも意味論的であり、2つはすべての実用的な目的で交換可能に使用できます。私の経験では、「バス」という用語は通常、コンピュータデバイスのエンクロージャ内のデジタルコンポーネントを接続する一連のワイヤを指し、「ネットワーク」は物理的に広く普及しているものを指します。 しかし、近年、「バス」という言葉は、長距離にわたる個別の計装センサーの相互接続に特化したネットワークを表す際に人気が高まっています(「フィールドバス」と「プロフィバス」は2つの例です)。いずれの場合も、2つ以上のデジタルデ

大規模で複雑なデジタルシステムの設計では、多くの場合、1つのデバイスで他のデバイスとの間でデジタル情報を通信する必要があります。デジタル情報の利点の1つは、アナログメディアでシンボル化された情報よりも、送信および解釈されたエラーに対してはるかに耐性がある傾向があることです。 これは、デジタルエンコードされた電話接続、コンパクトなオーディオディスクの明確さ、およびデジタル通信技術に対するエンジニアリングコミュニティの熱意の多くを説明しています。ただし、デジタル通信には独自の落とし穴があり、送信する方法には互換性のないさまざまな方法が多数あります。 この章で、デジタル通信の基本、その長所、短所

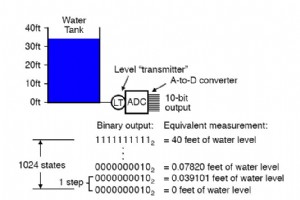

おそらく、ADCの最も重要な考慮事項は、その解像度です。 。分解能は、コンバータによって出力されるバイナリビットの数です。 ADC回路は、連続的に変化するアナログ信号を取り込み、それを多くの個別のステップの1つに分解するため、これらのステップの合計がいくつあるかを知ることが重要です。 たとえば、10ビット出力のADCは、最大1024(2 10 )を表すことができます。 )信号測定の独自の条件。 0%から100%までの測定範囲で、コンバーターによって正確に1024個の一意の2進数が出力されます(0000000000から1111111111まで)。 11ビットADCは、出力の2倍の状態(20

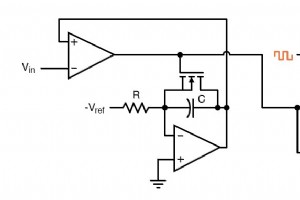

より高度なADCテクノロジーの1つは、いわゆるデルタシグマまたはΔΣ(適切なギリシャ文字表記を使用)です。数学と物理学では、ギリシャ文字の大文字のデルタ(Δ)は違いを表します。 または変更 、大文字のシグマ(Σ)は合計を表します :複数の用語を一緒に追加します。このコンバーターは、同じギリシャ文字で逆の順序で参照されることがあります:sigma-delta、またはΣΔ。 ΔΣコンバータでは、アナログ入力電圧信号が積分器の入力に接続され、入力の大きさに対応する出力で電圧変化率またはスロープを生成します。次に、このランピング電圧は、コンパレータによって接地電位(0ボルト)と比較されます。 コン

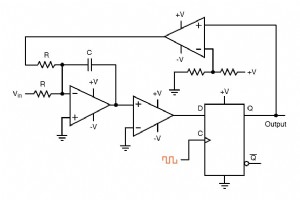

これまでのところ、ADC回路の一部としてDACを使用することによってのみ、フラッシュコンバーターの膨大な量のコンポーネントから逃れることができました。ただし、これが唯一の選択肢ではありません。アナログランプ回路とデジタルカウンタを正確なタイミングで置き換えると、DACの使用を回避できます。 これは、いわゆるシングルスロープの背後にある基本的な考え方です。 、または統合 ADC。ランプ出力のDACを使用する代わりに、積分器と呼ばれるオペアンプ回路を使用します。 のこぎり波を生成し、コンパレータによってアナログ入力と比較されます。 鋸歯状波形が入力信号電圧レベルを超えるのにかかる時間は、正確な

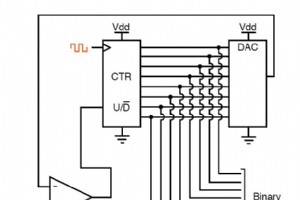

カウンターDACベースのコンバーターテーマの3番目のバリエーションは、私の推定では、最もエレガントです。 DACを駆動する通常の「アップ」カウンターの代わりに、この回路はアップ/ダウンカウンターを使用します。 カウンタは連続的にクロックされ、アップ/ダウン制御ラインはコンパレータの出力によって駆動されます。したがって、アナログ入力信号がDAC出力を超えると、カウンタは「カウントアップ」モードになります。 DAC出力がアナログ入力を超えると、カウンタは「カウントダウン」モードに切り替わります。いずれにせよ、DAC出力は常に追跡するための適切な方向にカウントされます 入力信号。

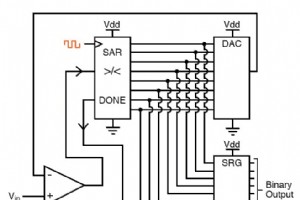

デジタルランプADCの欠点に対処する1つの方法は、いわゆる連続近似です。 ADC。この設計の唯一の変更点は、逐次比較レジスタとして知られる非常に特殊なカウンタ回路です。 。 このレジスタは、バイナリシーケンスでカウントアップする代わりに、最上位ビットで始まり最下位ビットで終わるビットのすべての値を試行することによってカウントします。カウントプロセス全体を通じて、レジスタはコンパレータの出力を監視して、バイナリカウントがアナログ信号入力よりも小さいか大きいかを確認し、それに応じてビット値を調整します。 レジスタのカウント方法は、10進数から2進数への変換の「トライアルアンドフィット」方式と同

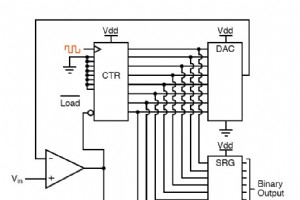

階段ランプとも呼ばれます 、または単にカウンター A / Dコンバーター、これもかなり理解しやすいですが、残念ながらいくつかの制限があります。 基本的な考え方は、自走バイナリカウンタの出力をDACの入力に接続し、DACのアナログ出力をデジタル化するアナログ入力信号と比較し、コンパレータの出力を使用してカウンタに停止するタイミングを指示することです。カウントしてリセットします。次の概略図は、基本的な考え方を示しています。 カウンタが各クロックパルスでカウントアップすると、DACはわずかに高い(より正の)電圧を出力します。この電圧は、コンパレータによって入力電圧と比較されます。

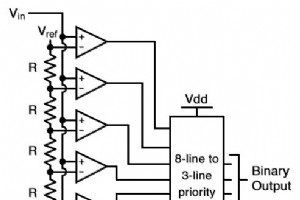

パラレルとも呼ばれます A / Dコンバータ、この回路は最も理解しやすい回路です。これは一連のコンパレータで構成されており、各コンパレータが入力信号を固有の基準電圧と比較します。コンパレータ出力はプライオリティエンコーダ回路の入力に接続され、プライオリティエンコーダ回路はバイナリ出力を生成します。次の図は、3ビットフラッシュADC回路を示しています。 V ref は、回路図には示されていない、コンバータ回路の一部として高精度電圧レギュレータによって提供される安定した基準電圧です。アナログ入力電圧が各コンパレータのリファレンス電圧を超えると、コンパレータ出力は順次ハイ状態に飽

産業技術