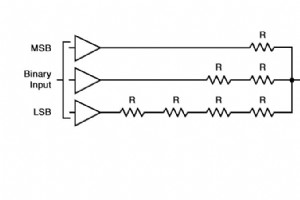

R / 2R DAC回路は、使用する固有の抵抗値が少ないバイナリ加重入力(R / 2nR)DACの代替です。 R / 2RDACとR / 2nR DAC 以前のDAC設計の欠点は、いくつかの異なる正確な入力抵抗値が必要なことでした。バイナリ入力ビットごとに1つの一意の値です。組み立て前に購入、在庫、および並べ替えるさまざまな抵抗値が少ない場合は、製造が簡素化される可能性があります。 もちろん、複数の抵抗を直列に接続することで、バイナリ加重入力DAC回路を変更して、単一の入力抵抗値を使用するようにすることもできます。 残念ながら、このアプローチは、あるタイプ

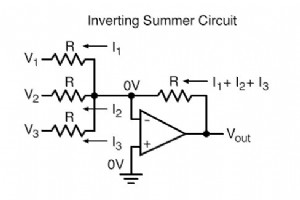

R / 2nR DAC回路とは何ですか? R / 2nR DAC回路、別名バイナリ加重入力 DACは、反転加算オペアンプ回路のバリエーションです。 (「合計」回路は「夏」回路と呼ばれることもあることに注意してください。) 思い出してください。古典的な反転加算回路は、制御されたゲインに負帰還を使用するオペアンプであり、複数の電圧入力と1つの電圧出力を備えています。出力電圧は、すべての入力電圧の逆(反対の極性)の合計です: 単純な反転加算回路の場合、すべての抵抗は同じ値である必要があります。入力抵抗のいずれかが異なる場合、入力電圧は出力に異なる程度の影響を及ぼし、出力電圧は真の

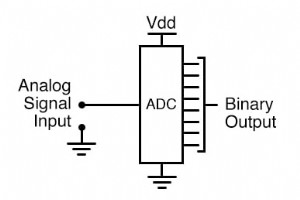

センサーデバイス自体が本質的にデジタルである場合、デジタル回路をセンサーデバイスに接続するのは簡単です。スイッチ、リレー、およびエンコーダーは、信号のオン/オフの性質により、ゲート回路と簡単に接続できます。 ただし、アナログデバイスが関係する場合、インターフェイスははるかに複雑になります。必要なのは、アナログ信号をデジタル(バイナリ)量に、またはその逆に電子的に変換する方法です。 アナログ-デジタル変換器 、またはADCは、デジタル-アナログコンバーターの間に前者のタスクを実行します 、またはDACは、後者を実行します。 ADCは、電圧や電流などのアナログ電気信号を入力し、2進数を出力しま

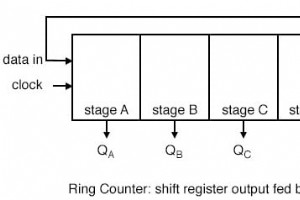

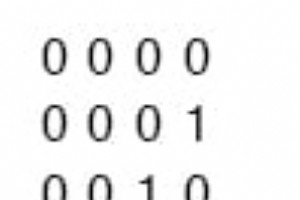

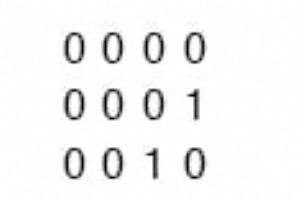

シフトレジスタの出力が入力にフィードバックされる場合。リングカウンタが発生します。シフトレジスタに含まれるデータパターンは、クロックパルスが印加されている限り再循環します。 たとえば、データパターンは、次の図の4クロックパルスごとに繰り返されます。ただし、データパターンをロードする必要があります。 すべて 0 のまたはすべての 1 はカウントされません。このような状態からの連続論理レベルは役に立ちますか? 以下のリングカウンタとして構成されたパラレル入力/シリアル出力シフトレジスタにデータをロードするための準備をします。 任意のランダムパターンをロードできます。最も一

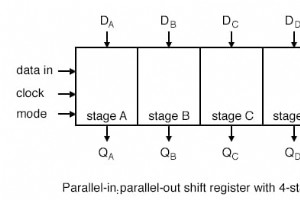

パラレルイン/パラレルアウトシフトレジスタの目的は、パラレルデータを取り込み、シフトしてから、以下のように出力することです。 ユニバーサルシフトレジスタは、パラレルイン/パラレルアウト機能に加えて、すべてを実行するデバイスです。 上記では、4ビットのデータを D A のパラレル入力/パラレル出力シフトレジスタに適用します。 D B D C D D 。複数の入力である可能性のあるモード制御は、並列ロードとシフトを制御します。 モード制御は、一部の実際のデバイスでシフトの方向を制御する場合もあります。データは、クロックパルスごとに1ビット位置にシフトされます。

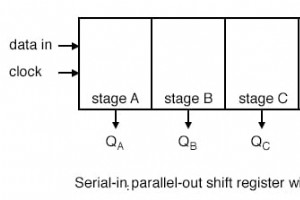

シリアル入力、パラレル出力のシフトレジスタは、データを内部ストレージ要素にシフトし、シリアル出力、データ出力、ピンでデータをシフトアウトするという点で、シリアル入力、シリアル出力のシフトレジスタに似ています。 これは、すべての内部ステージを出力として使用できるようにするという点で異なります。したがって、シリアル入力、パラレル出力のシフトレジスタは、データをシリアル形式からパラレル形式に変換します。 シリアル入力、パラレル出力のシフトレジスタの使用例 以下のデータ入力時に、4つのデータビットが1本のワイヤを介して4つのクロックパルスでシフトインされると、データは4つの出力Q A で同時

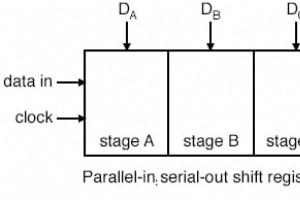

パラレル入力/シリアル出力シフトレジスタは、以前のシリアル入力/シリアル出力シフトレジスタが行うすべてのことと、すべてのステージへの入力データを同時に実行します。 パラレル入力/シリアル出力シフトレジスタは、データを格納し、クロックごとにデータをシフトし、ステージ数にクロック周期を掛けた分だけ遅延させます。 さらに、パラレル入力/シリアル出力は、シフトが始まる前にすべてのステージにデータを並列にロードできることを意味します。 これは、パラレルからデータを変換する方法です。 シリアルにフォーマットする フォーマット。パラレルフォーマットとは、以下に示すように、データビットがデータビットごと

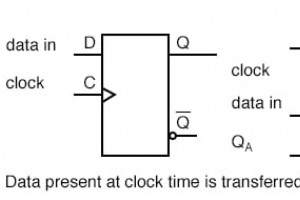

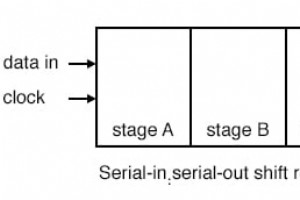

シリアル入力、シリアル出力のシフトレジスタは、ステージごとに1クロック時間ずつデータを遅延させます。 レジスタごとに少しのデータを格納します。シリアル入力、シリアル出力のシフトレジスタの長さは1〜64ビットで、レジスタまたはパッケージがカスケード接続されている場合はさらに長くなります。 以下は、レジスタクロックに同期されていないデータを受信する単段シフトレジスタです。 D の「データ入力」 タイプ D のピン FF (フリップフロップ)は、クロックがローからハイに変化してもレベルを変更しません。 デジタル論理回路の信頼性を向上させるために、データを回路基板のシステム全体のクロック

シフトレジスタは、カウンタと同様に、シーケンシャルロジックの形式です。 。 シーケンシャルロジックは、組み合わせロジックとは異なり、現在の入力だけでなく、以前の履歴の影響も受けます。 つまり、シーケンシャルロジックは過去のイベントを記憶します。 シフトレジスタは、デジタル信号または波形の離散遅延を生成します。 クロックに同期した波形 、繰り返される方形波は、「n」だけ遅延します 「n」の個別のクロック時間 はシフトレジスタのステージ数です。 したがって、4ステージシフトレジスタは、「データ入力」を4クロック遅延させて「データ出力」します。 シフトレジスタのステージは遅延ステージです

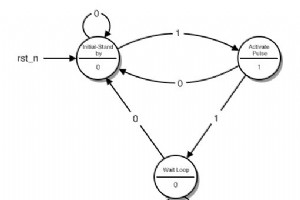

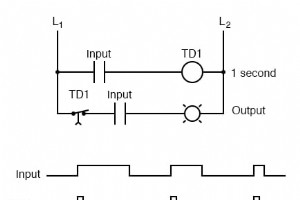

これまで、提示されたすべての回路は組み合わせでした 回路。つまり、その出力は現在の入力のみに依存します。そのタイプの回路の以前の入力は、出力に影響を与えません。 ただし、回路に「メモリ」が必要なアプリケーションはたくさんあります。以前の入力を記憶し、それらに従って出力を計算します。出力が現在の入力だけでなく入力の履歴にも依存する回路は、シーケンシャル回路と呼ばれます。 。 このセクションでは、このような順序回路を設計および構築する方法を学習します。この手順がどのように機能するかを確認するために、例を使用して、トピックを学習します。 それで、時計で動作し、手動ボタンから入力を読み取るデジタ

不完全

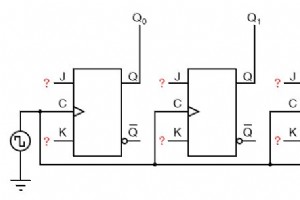

同期とは カウンター? 同期カウンター 、非同期カウンターとは対照的 は、出力ビットがリップルなしで同時に状態を変化させるものです。 J-Kフリップフロップからこのようなカウンタ回路を構築する唯一の方法は、すべてのクロック入力を接続して、すべてのフリップフロップがまったく同じクロックパルスをまったく同時に受信するようにすることです。 さて、問題は、JとKの入力をどうするかということです。バイナリシーケンスでカウントするには、同じ2分周周波数パターンを維持する必要があります。このパターンは、フリップフロップの「トグル」モードを使用して最もよく達成されるため、 JとKの入力は両

前のセクションでは、11から10、01から00までの2ビットのバイナリシーケンスで逆方向にカウントされる1つのJ-Kフリップフロップを使用する回路を見ました。 前方を数えることができる回路を持つことが望ましいので 逆方向だけでなく、順方向のカウントシーケンスをもう一度調べて、そのような回路を構築する方法を示す可能性のあるパターンをさらに探すことは価値があります。 バイナリカウントシーケンスはオクターブ(2倍)の周波数分割のパターンに従い、「トグル」モード用に設定されたJKフリップフロップマルチバイブレータはこのタイプの周波数分割を実行できることがわかっているので、回路を想像できます。いくつ

0000から1111までの4ビットのバイナリカウントシーケンスを調べると、0から1までのビットの「振動」に明確なパターンが明らかになります。 最下位ビット(LSB)がカウントシーケンスのすべてのステップで0と1の間で切り替わるのに対し、後続の各ビットは前のビットの半分の周波数で切り替わることに注意してください。 最上位ビット(MSB)は、16ステップのカウントシーケンス全体で1回だけトグルします:7(0111)と8(1000)の間の遷移時。 4ビットバイナリで「カウント」するデジタル回路を設計する場合、必要なのは一連の分周回路を設計することだけです。各回路は、方形波パルスの周波数を

単安定マルチバイブレータの使用例はすでに見てきました。フリップフロップの回路内で使用されるパルス検出器で、クロック入力信号がローからハイまたはハイからローに遷移するときにラッチ部分を短時間有効にします。 。 パルス検出器は、 1 しかないため、単安定マルチバイブレータとして分類されます。 安定した状態。 安定 、私は、デバイスが外部からのプロディングなしで永久にラッチまたは保持できる出力の状態を意味します。 双安定デバイスであるラッチまたはフリップフロップは、「セット」または「リセット」状態のいずれかを無期限に保持できます。セットまたはリセットされると、外部入力によって変更するように求めら

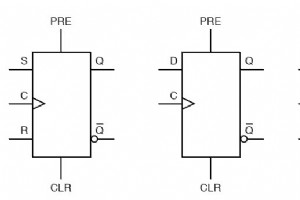

フリップフロップへの通常のデータ入力(D、SとR、またはJとK)は、出力(Qと非Q)に段階的に、または同期してのみ影響を与えるため、同期入力と呼ばれます。クロック信号が遷移します。 私が今あなたに注意を向けているこれらの追加の入力は、クロック信号のステータスに関係なくフリップフロップを設定またはリセットできるため、非同期と呼ばれます。通常、これらはプリセットおよびクリアと呼ばれます: プリセット入力がアクティブになると、同期入力またはクロックに関係なく、フリップフロップが設定されます(Q =1、Q =0ではありません)。クリア入力がアクティブになると、同期入力またはクロックに

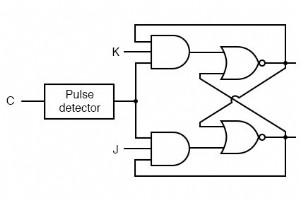

双安定マルチバイブレータをテーマにしたもう1つのバリエーションは、J-Kフリップフロップです。基本的に、これは「無効」または「不正」な出力状態のないS-Rフリップフロップの修正バージョンです。次の図をよく見て、これがどのように達成されるかを確認してください。 JおよびK入力 以前はS入力とR入力でしたが、現在はそれぞれJ入力とK入力と呼ばれています。古い2入力ANDゲートは3入力ANDゲートに置き換えられ、各ゲートの3番目の入力はQ出力と非Q出力からフィードバックを受け取ります。 これにより、回路がリセットされたときにのみJ入力が有効になり、回路が設定されたときにのみK入力

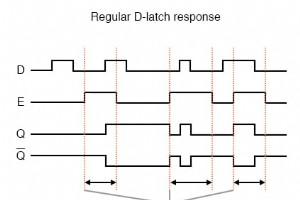

これまで、イネーブル入力を備えたS-RおよびDラッチ回路の両方を研究してきました。ラッチは、イネーブル入力がアクティブになっている場合にのみデータ入力(S-RまたはD)に応答します。ただし、多くのデジタルアプリケーションでは、ラッチ回路の応答性を、イネーブル入力がアクティブ化される期間全体ではなく、非常に短い期間に制限することが望ましいです。 マルチバイブレータ回路を有効にする1つの方法は、エッジトリガーと呼ばれます。 、ここで、回路のデータ入力は、イネーブル入力が遷移している間だけ制御できます。 ある州から別の州へ。 通常のDラッチとエッジトリガーのタイミング図を比較してみましょう:

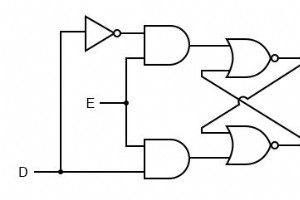

ゲートSRラッチのイネーブル入力は、SまたはRのステータスに関係なくQ出力と非Q出力をラッチする方法を提供するため、これらの入力の1つを削除して、「不正な」入力のないマルチバイブレータラッチ回路を作成できます。状態。 このような回路はDラッチと呼ばれ、その内部ロジックは次のようになります。 R入力が古いS入力の補数(反転)に置き換えられ、S入力の名前がDに変更されていることに注意してください。ゲートSRラッチと同様に、有効にすると、Dラッチは信号入力に応答しません。入力は0です。最後の状態でラッチされたままになります。ただし、イネーブル入力が1の場合、Q出力はD入力の後に続き

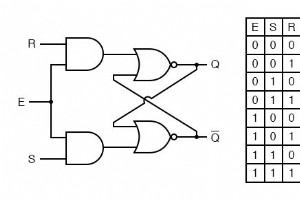

論理回路では、SおよびR入力状態に関係なく、特定の条件が満たされた場合にのみ状態を変更するマルチバイブレータがあると便利な場合があります。 条件付き入力は enable と呼ばれます 、および文字Eで表されます。次の例を調べて、これがどのように機能するかを確認してください。 ゲートSR-ラッチ真理値表 E =0の場合、SまたはRの状態に関係なく、2つのANDゲートの出力は強制的に0になります。その結果、回路はSとRが両方とも0であるかのように動作し、Q出力と非Q出力をラッチします。最後の状態で。 イネーブル入力がアクティブになっている場合(1)にのみ、ラッチはSおよ

産業技術