エンジニアリングのミスは決して避けられません。これらの間違いが、PCB 設計能力の低レベルまたは卓越性の欠如を表していると信じるのは愚かなことではありません。しかし、エンジニアが犯しがちな過ちのほとんどは、システム効率、シグナル インテグリティ、低エネルギー消費、およびコスト削減に関する過剰な考慮に由来しています。言い換えれば、それらの間違いは「優しさ」の結果です。したがって、「親切」を意識し、それらの間違いをタイムリーに回避することは、プロジェクトの円滑な実施に非常に役立ちます。 システム効率 間違い 1:CPU のランダムな変更 一部のエンジニアは、基本周波数が 100M の CPU

情報技術の絶え間ない発展に伴い、電子製品はその機能、カテゴリ、および構造の点でますます複雑になり、PCB 設計は多層化および高密度化の方向に進んでいます。その結果、PCB 設計の EMC (Electromagnetic Compatibility) に多くの注意を払う必要があります。PCB の EMC 設計は、ボード上のすべての回路の正常で安定した動作を保証するだけでなく、相互に干渉しないようにするためです。また、回路が外部の放射と伝導によって干渉されるのを防ぐために、PCB の放射透過と伝導放射を効果的に減少させます。干渉は EMC の最大の敵です。しかし、エンジニアの皆さん、この記事

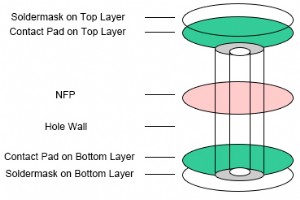

高速信号は、通信業界にとって避けることのできないホットなトピックです。伝送される情報量と伝送速度の増加に伴い、信号の高速化がますます重要になってきています。高速 PCB は高速信号のロード ボードであり、その材料の選択、製造技術、配線設計のすべてが高速信号の品質に影響します。 Non-Functional Pad (別名 NFP) は高速 PCB を製造する技術的手法であり、挿入損失は信号品質を示す最も重要なパラメーターの 1 つです。 NFP を削除するか保持するかは、エンジニアとメーカーの間で避けられない議論のトピックでした。この記事では、高速信号の挿入損失に対する NFP の影響を製造手

断熱材の説明 通常の 380V AC 配電システムでは、制御電源は通常 DC 電源システムから得られます。発電所の重要な待機電源および制御電源として、DC システムの最も一般的で危険な欠陥は、DC アースの欠陥にあります。よくある絶縁不良から、DC制御電源の絶縁低下につながる一連の原因を探ります。 欠陥の検索と原因の分析 • ループ紹介 この記事の次の部分で説明する 2 次回路は、主に 380V AC システムに準拠しています。スイッチ二次側回路では、交流制御電源から漏電保護装置内の漏電保護補助電源端子と変流器部を介して制御電源を得ています。この記事の次の部分で言及される端子 5 と

これまで、スマートフォンは、毎日のコミュニケーションと活動の 3 分の 1 以上がスマートフォンで完了し、その価値が毎年急速に上昇している、なくてはならない電子製品になりました。 2020 年までに、言語機能を備えた携帯電話は 23.5% の割合で減少すると推定されています。逆に、低価格で低機能のスマートフォン、中程度のスマート フォンを含むすべてのレベルのスマートフォンは、2020 年までに 8.0% の成長傾向を維持します。携帯電話とハイエンドのスマートフォン。 今日のスマートフォンは、音声通話やメールなどの通常の機能は別として、Web ページの閲覧、オンライン コミュニケーションやサ

信号に対する相対遅延の影響 差動信号線で伝送される信号には、信号の差動モード成分とコモンモード成分が含まれています。 差動信号の量は、式 Vdiff に従う 2 つの信号間の差を指します。 =V1 - V2 .コモンモード信号の量は、次の式の 2 つの信号の合計の半分を指します。 .したがって、単一のラインの電圧変化は、ディファレンシャル モード信号とコモン モード信号に同時に影響を与えます。次に、グラフ ソフトウェアを使用して関数図を作成し、ディファレンシャル モード信号とコモン モード信号への影響をそれぞれ調べます。研究の便宜上、シグナルは同じアッパータイムとダウンタイムを持つ台形波

現在、高速シリアル伝送を応用した高性能コンピュータ相互接続ネットワークの伝送速度は、初代SDR(Single Data Rate、2.5Gb/s)から第4世代のFDR(Fourteen Data Rate、14Gb/s)へと発展しています。 s)、DDR (ダブル データ レート、5Gb/s)、および QDR (クアッド データ レート、10Gb/s)。インターネットの形成に不可欠な相互接続やスイッチボード、インターフェイスカードを備えた PCB (Printed Circuit Board) の設計は、FDR の高速および高周波分野に参入しました。 FDR 信号の立ち上がり時間が 10ps

近年のスイッチング電源技術は、チップの高集積化に伴い、小型化、高周波化、高効率化が進んでいます。設計ソフトウェアによってはスイッチ電源の設計が比較的容易なため、高度に統合された制御チップにより、必要な周辺コンポーネントが簡素化されます。しかし、高集積化の問題は、設計の自由度の低下、チップの入手可能性の低下、および低価格につながります。各メーカーが開発した設計ソフトウェアは、いくつかの種類の固有のチップをシミュレートすることができます。実際のアプリケーションでは、優れた動作条件で製品の要求に適合するスイッチ電源を設計することが重要です。 RFID 用電源モジュールの要件に基づいて、スイッチ電源は

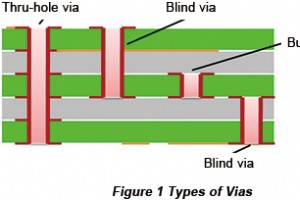

システム オブ サーキットにおける大規模および超大規模集積回路のアプリケーションの増加に伴い、回路基板は、チップの集積規模の拡大、体積の縮小、ピンのエスカレーション、および増加により、多層化および複雑化への発展傾向を示しています。速度率の。高速多層 PCB のほとんどは、スルーホール ビアを介して層間接続を実装します。ただし、上から下に循環しない電気接続では、冗長なスルーホール ビア スタブが発生し、PCB の伝送品質に悪影響を与える可能性があります。したがって、高性能で要件の高い一部の高速デジタル システムに関しては、冗長スタブの影響を無視することはできません。コストとパフォーマンスのバラン

電子製品の改良は、電子技術の進歩と密接に関係しています。電子技術の急速な発展に伴い、電子製品は、電源とグランドが最も重要な部分である PCB 電磁適合性 (EMC) 設計に多くの干渉をもたらす小型化と高密度化に向かって発展しました。したがって、電子製品の開発と電磁設計の干渉に直面し、EMC 干渉の確実性に基づいて EMC 設計の最適化を実施する必要があります。 電磁両立性における電源と接地の干渉に関する分析 電源回路は電子回路と電力網を接続する媒体であり、ノイズは電磁適合性設計を妨害する主な理由です。 PCB設計の発展に伴い、電磁適合性設計における電圧も回路の不安定性につながる主要な要素です

電子科学と技術の今後の発展に伴い、IC チップによって構成される電子システムは、大規模、小型、高速に向かって急速に発展しています。同時に、電子システムの体積の縮小は回路の配線密度の増大につながり、信号周波数は常に上昇し、信号のエッジターンオーバー時間が短くなるという問題も生じます。信号の相互接続遅延が信号ターンオーバー時間より 10% 大きい場合、ボード上の信号リードは伝送線路の影響を示し、信号の反射やクロストークなどの一連の問題がますます顕在化します。高速化問題の出現は、ハードウェア設計に大きな課題をもたらし、ロジックの観点から正しいと見なされる設計が不適切に処理されない場合、設計全体が失敗

今日、あらゆる種類の電子製品が人々の生活の隅々に浸透しており、電子機器の中核である PCB の急速な発展につながっています。電子機器が正常に、安全に、安定して動作するかどうかは、PCB の設計に大きく依存します。 PCB 設計のプロセスにおいて、最も重要なリンクは、電子製品の接地と干渉防止に関する設計です。これまで、特定の PCB の設計者は、接地と干渉防止に関して独自の意見を持っており、接地と干渉防止に関する方法と技術の両方が時々進歩しており、電子デバイスに常に安定したセキュリティ動作に大きな保証を提供します。この記事では、PCB の干渉防止と接地の戦略について説明します。 デジタル信号とア

近年、デジタルビデオやデジタルモバイル通信に関連する電子製品の急速な発展に伴い、この種の製品の開発により、PCB は軽量、薄型、小型、多機能、高密度、高信頼性の面で開発が進んでいます。 PCB の配線スペースが限られているため、ビア、ワイヤ、ワイヤ、ビア間の制限が厳しくなり、ビア銅充填技術が出現して、PCB の密度が約 10% から 30% 向上します。図 1 は、ビア銅充填に基づく HDI (高密度相互接続) ボードを示しています。 配線スペースを大幅に削減できるビア設計や、銅埋め込みブラインドビアの信頼性が高いことから、銅埋め込みめっきブラインドビアには多くのメリットがあります。さ

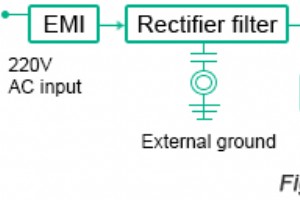

新世代の電子技術は、コンポーネントのエッジ速度の高速化につながります。回路の動作速度の向上により、PCB 設計に対する要件がますます厳しくなっています。 PCB 設計の品質は、コンポーネントと回路全体の動作性能を決定します。特に、コストや PCB 面積、包括的な回路の機能を考慮すると、EMI (電磁インターフェース) の発生源は複雑なメカニズムでますます広範になります。 EMI メカニズムとソリューション EMI の主な要素には、電磁干渉源、伝送経路、および干渉対象が含まれます。 EMI の発生につながる要素を特定した上で、解決しやすい要素と、PCB 設計の過程で部分的にしか解決できない要素

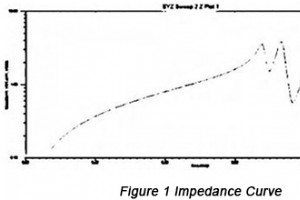

PCB 設計の複雑さの増大に伴い、安定した信頼性の高い電源は、高速 PCB 設計に関する研究の新しい傾向になっています。特に、スイッチング部品の数が絶えず増加し、Vcore が減少し続ける場合、電力の変動はシステムに致命的な影響を与える傾向があります。したがって、電源システムの安定性を維持することは、高速 PCB 設計の重要なポイントとなっています。 しかし、電源系インピーダンスが存在する結果、電源系インピーダンスに負荷過渡電流による比較的大きな電圧降下が発生し、システムが不安定になります。各コンポーネントに最初から最後まで正常な電力が供給されるようにするためには、電力システムのインピーダ

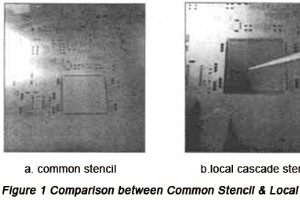

電子製品の小型化の傾向は、製品の複雑な構造につながり、マルチチップモジュールの普及を促進します。コア モジュールの登場は、SMT の新たな課題です。ただし、大規模な基板と熱理論のために、誤溶接や連続スズ電着などの問題が新製品の搭載時に発生します。 回路モジュールのSMTはんだ付け信頼性に関する研究 仮溶接とは、スズで固定されていない溶接部の表面にスズ層が十分にめっきされていない、コンポーネントの溶接面と PAD の間に金属合金が生成されていない、圧力によってコンポーネントが緩んで故障する可能性がある状況を指します。はんだ付けポイントの最小高さは、はんだ付けポイントの最小高さとはんだ付け可能な

PCBソルダーマスクの製造工程では、シルクスクリーン印刷ネイルベッドによるPCB連続両面印刷液体ソルダーマスクの技術が大規模に適用されています。基板の厚さ、パターン分布、ビア径、ビア分布などの設計上の違いは基板ごとに比較的大きな差が生じるため、シルクスクリーン印刷によるネイルベッドの製造は非常に困難です。ネイルベッド上の銅ネイルの分布が合理的ではない場合、はんだマスクの厚さの均一性が簡単に発生します。悪い結果は、はんだマスクの外観の色収差、悪いはんだマスク イメージング、または壊れた抵抗によるはんだブリッジのいずれかであり、再加工またはスクラップにつながります。したがって、ネイル ベッドの品質

電子技術の急速な発展は、電子部品の高密度化に貢献しており、PCB 設計者に干渉防止機能が求められています。 PCB 設計のプロセスでは、設計者は PCB 設計の一般原則と干渉防止の要件に準拠する必要があります。 PCB 設計における干渉防止の能力は、設計の重要なポイントとさえ見なされている電子製品の有効性と安定性に直接関係しています。設計の手順で干渉防止の要件が十分に考慮されると、後で干渉防止対策を講じる必要がないため、時間も節約されます。 PCB の干渉発生源 PCB での干渉発生の原因は、次の要素に由来します。a.干渉源とは、リレー、シリコン制御整流器、電気機械、高周波クロックなど、干渉

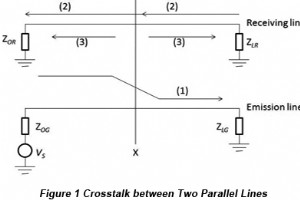

クロストーク理論 電磁理論に基づくと、クロストークは 2 つの信号線間の電磁的デカップリングを指します。信号線間の相互容量や相互インピーダンスによって発生するノイズの一種です。 図 1 では、平行する 2 つのラインのうち、1 つのラインに信号源 (VS) があります。 ) と内部インピーダンス (ZOG ) ラインの一端と負荷インピーダンス (ZLG ) 反対側で、地面を通る閉ループを形成します。もう一方の線には抵抗しかありません (ZOR と ZLR ) アースまで単線の構造。この図では、信号源を持つ導線を発光線または干渉線と呼び、もう一方の線を受信線または干渉線と呼びます

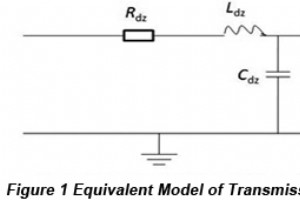

インピーダンス制御技術は、高速 PCB の優れた性能を確保するために効果的な方法を採用する必要がある高速デジタル回路設計において非常に重要です。 PCB 上の高速回路伝送ラインのインピーダンス計算とインピーダンス制御 • 送電線の等価モデル 図 1 は、タンデムおよび複数のコンデンサ、抵抗器、およびインダクタ (RLGC モデル) を含む構造である PCB 上の伝送線路の等価効果を示しています。 タンデム抵抗の典型的な値は 0.25 から 0.55 オーム/フィートの範囲であり、複数の抵抗器の抵抗値は通常非常に高いままです。 PCB 伝送ラインに寄生抵抗、キャパシタンス、およびイン

産業技術